## SPI/Digital or I<sup>2</sup>C µModule Isolator with Fixed ±5V and Adjustable 5V Regulated Power

### **FEATURES**

- 6-Channel Logic Isolator: 2500V<sub>RMS</sub> for 1 Minute

UL-CSA Recognized States Sile #E151738

- Isolated DC Power:

- 3V to 5V Adjustable at Up to 100mA

- ±5V Fixed at Up to 100mA

- No External Components Required

- SPI/Digital (LTM2886-S) or I<sup>2</sup>C (LTM2886-I) Options

- High Common Mode Transient Immunity: 30kV/µs

- High Speed Operation:

- 10MHz Digital Isolation

- 4MHz/8MHz SPI Isolation

- 400kHz I<sup>2</sup>C Isolation

- 3.3V (LTM2886-3) or 5V (LTM2886-5) Operation

- 1.62V to 5.5V (LTM3886-S) or 3V to 5.5V (LTM2886-I) Logic Supply

- ±10kV ESD HBM Across the Isolation Barrier

- Maximum Continuous Working Voltage: 560V<sub>PEAK</sub>

- Low Current Shutdown Mode (<10µA)

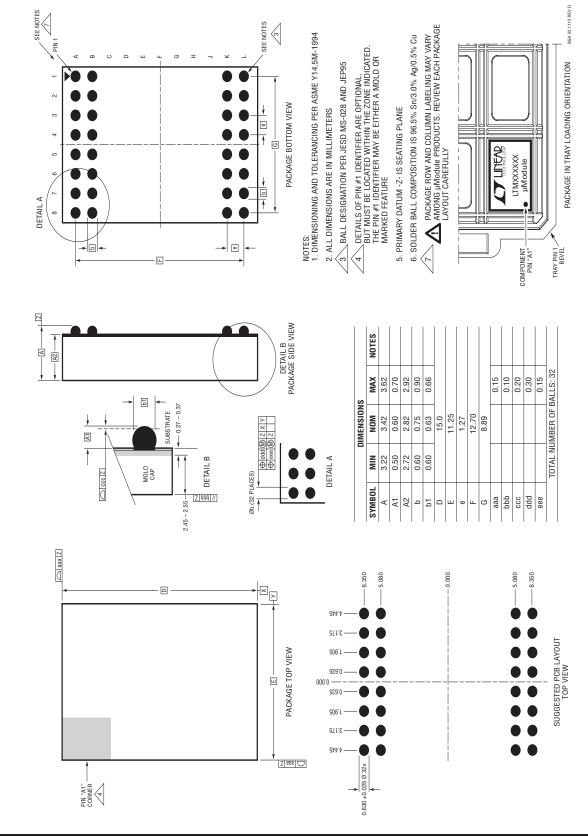

- Low Profile (15mm × 11.25mm × 3.42mm) BGA Package

### APPLICATIONS

- Isolated SPI or I<sup>2</sup>C Interfaces

- Industrial Systems

- Test and Measurement Equipment

- **Breaking Ground Loops**

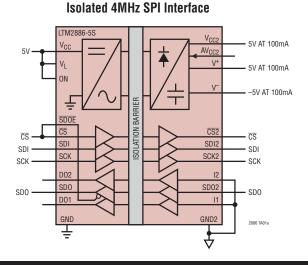

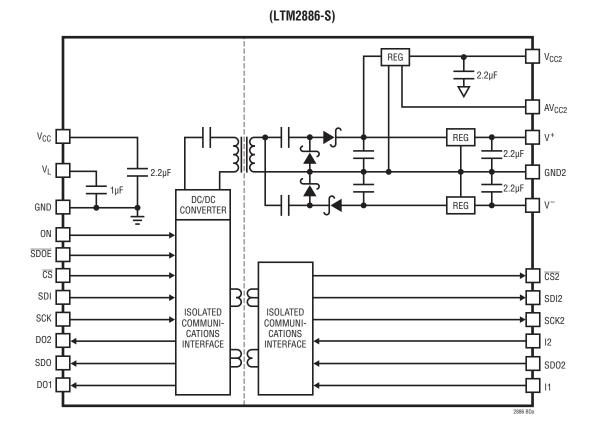

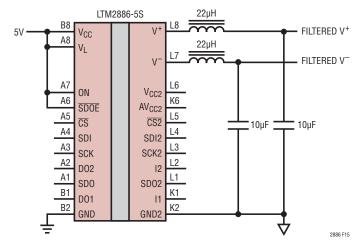

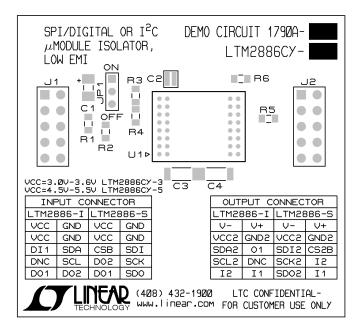

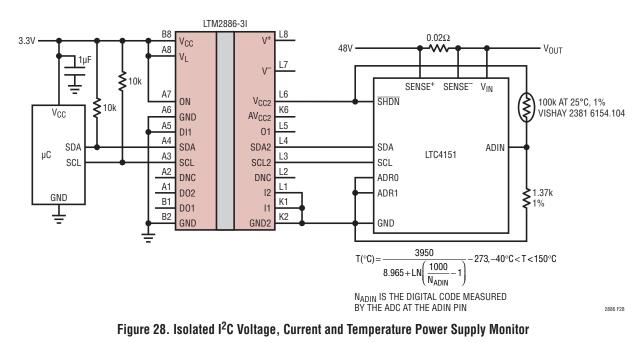

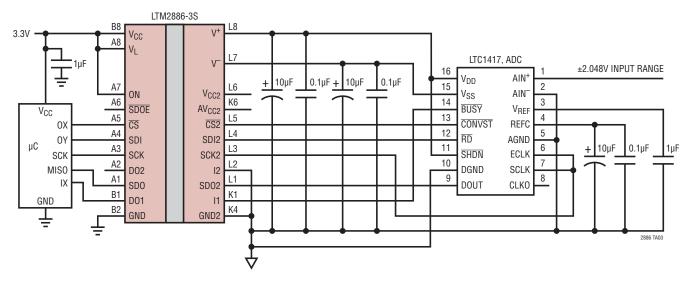

## TYPICAL APPLICATION

## DESCRIPTION

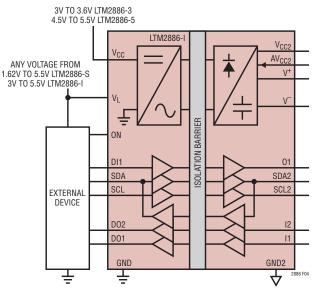

The LTM<sup>®</sup>2886 is a complete galvanic digital µModule<sup>®</sup> (micromodule) isolator. No external components are required. A single 3.3V or 5V supply powers both sides of the interface through an integrated, isolated DC/DC converter. A logic supply pin allows easy interfacing with different logic levels from 1.62V to 5.5V, independent of the main supply.

Available options are compliant with SPI and I<sup>2</sup>C (master mode only) specifications.

The isolated side includes fixed ±5V and 5V adjustable power supplies, each capable of providing more than 100mA of load current. The 5V adjustable supply may be programmed via an external voltage divider.

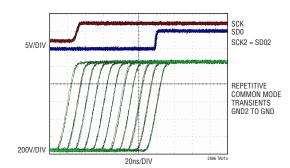

Coupled inductors and an isolation power transformer provide 2500V<sub>RMS</sub> of isolation between the input and output logic interface. This device is ideal for systems where the ground loop is broken, allowing for a large common mode voltage range. Communication is uninterrupted for common mode transients greater than 30kV/µs.

T, LT, LTC, LTM, Linear Technology, the Linear logo and µModule are registered trademarks of Analog Devices, Inc. All other trademarks are the property of their respective owners.

#### LTM2886 Operating Through 50kV/us CM Transients

Rev C

### **ABSOLUTE MAXIMUM RATINGS**

(Note 1)

| V <sub>CC</sub> to GND                       | 0.3V to 6V                        |

|----------------------------------------------|-----------------------------------|

| V <sub>L</sub> to GND                        | 0.3V to 6V                        |

| V <sub>CC2</sub> , AV <sub>CC2</sub> to GND2 | 0.3V to 6V                        |

| V <sup>+</sup> to GND2                       | –0.3V to 6V                       |

| V <sup>-</sup> to GND2                       | 0.3V to -6V                       |

| Logic Inputs                                 |                                   |

| DI1, SCK, SDI, CS, SCL, SD                   | A, <u>SDOE</u> ,                  |

| ON to GND                                    | 0.3V to (V <sub>L</sub> + 0.3V)   |

| I1, I2, SDA2,                                |                                   |

| SDO2 to GND2                                 | 0.3V to (V <sub>CC2</sub> + 0.3V) |

|                                              |                                   |

| D01, D02, SD0 to GND $-0.3V$ to (V <sub>L</sub> + 0.3V) 01, SCK2, SDI2, CS2, |

|------------------------------------------------------------------------------|

| SCL2 to GND2 $-0.3V$ to $(V_{CC2} + 0.3V)$                                   |

| Operating Temperature Range (Note 4)                                         |

| LTM2886C                                                                     |

| LTM2886I–40°C to 85°C                                                        |

| LTM2886H–40°C to 125°C                                                       |

| Maximum Internal Operating Temperature 125°C                                 |

| Storage Temperature Range –55°C to 125°C                                     |

| Peak Body Reflow Temperature                                                 |

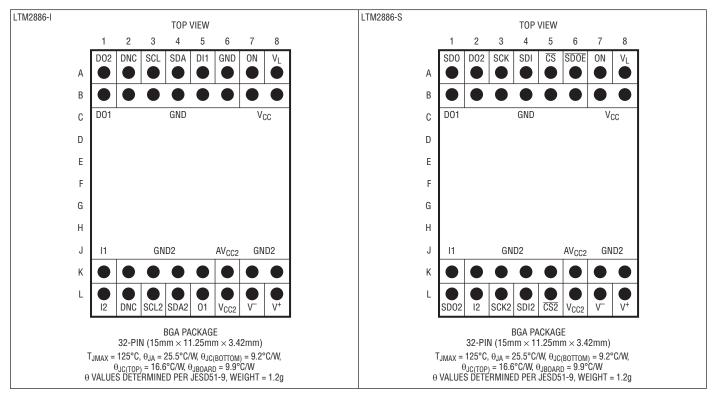

### PIN CONFIGURATION

### **PRODUCT SELECTION GUIDE**

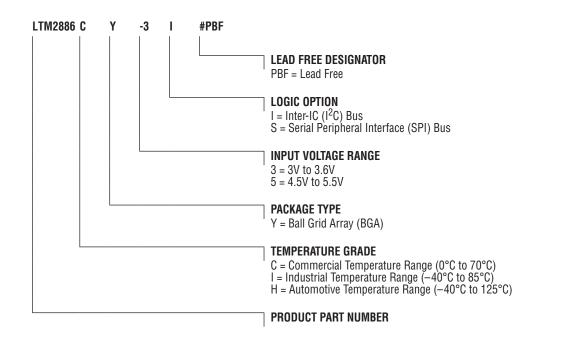

### ORDER INFORMATION http://www.linear.com/product/LTM2886#orderinfo

|                  |                       | PART M                 | ARKING      |                 |               |                        |                  |                      |

|------------------|-----------------------|------------------------|-------------|-----------------|---------------|------------------------|------------------|----------------------|

| PART NUMBER      | PAD OR BALL<br>Finish | DEVICE                 | FINISH CODE | PACKAGE<br>Type | MSL<br>Rating | INPUT VOLTAGE<br>Range | LOGIC<br>Option  | TEMPERATURE<br>RANGE |

| LTM2886CY-3I#PBF |                       |                        |             |                 |               |                        |                  | 0°C to 70°C          |

| LTM2886IY-3I#PBF |                       | LTM2886Y-31            |             |                 |               |                        | I <sup>2</sup> C | -40°C to 85°C        |

| LTM2886HY-3I#PBF |                       |                        |             |                 |               | 3V to 3.6V             |                  | -40°C to 125°C       |

| LTM2886CY-3S#PBF |                       |                        |             |                 |               | 37 10 3.67             | SPI              | 0°C to 70°C          |

| LTM2886IY-3S#PBF |                       | LTM2886Y-3S            |             |                 |               |                        |                  | -40°C to 85°C        |

| LTM2886HY-3S#PBF |                       |                        | at          | DCA             |               |                        |                  | -40°C to 125°C       |

| LTM2886CY-5I#PBF | 5AC305 (R0H5)         | SAC305 (RoHS) e1 BGA 3 | 3           |                 |               | 0°C to 70°C            |                  |                      |

| LTM2886IY-5I#PBF |                       | LTM2886Y-51            |             |                 |               |                        | l <sup>2</sup> C | -40°C to 85°C        |

| LTM2886HY-5I#PBF |                       |                        |             |                 |               |                        |                  | -40°C to 125°C       |

| LTM2886CY-5S#PBF |                       |                        |             |                 |               | 4.5V to 5.5V           |                  | 0°C to 70°C          |

| LTM2886IY-5S#PBF |                       | LTM2886Y-5S            |             |                 |               |                        | SPI              | -40°C to 85°C        |

| LTM2886HY-5S#PBF |                       |                        |             |                 |               |                        |                  | -40°C to 125°C       |

· Device temperature grade is indicated by a label on the shipping container.

· Recommended BGA PCB Assembly and Manufacturing Procedures: www.linear. com/BGA-assy

• Pad or ball finish code is per IPC/JEDEC J-STD-609.

• Terminal Finish Part Marking: www.linear.com/leadfree

· BGA Package and Tray Drawings: www.linear.com/packaging • This product is moisture sensitive. For more information, go to:

This product is not recommended for second side reflow. For • more information, go to www.linear.com/BGA-assy

www.linear.com/BGA-assy

**ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the specified operating temperature range, otherwise specifications are at  $T_A = 25$ °C. LTM2886-3 V<sub>CC</sub> = 3.3V, LTM2886-5 V<sub>CC</sub> = 5V, V<sub>L</sub> = 3.3V, and GND = GND2 = 0V, ON = V<sub>L</sub> unless otherwise noted. Specifications apply to all options unless otherwise noted.

| SYMBOL           | PARAMETER                      | CONDITIONS                                                |   | MIN       | ТҮР           | MAX            | UNITS             |

|------------------|--------------------------------|-----------------------------------------------------------|---|-----------|---------------|----------------|-------------------|

| Input Sup        | plies                          |                                                           |   |           |               |                | . <u> </u>        |

| V <sub>CC</sub>  | Input Supply Range             | LTM2886-3<br>LTM2886-5                                    | • | 3<br>4.5  | 3.3<br>5      | 3.6<br>5.5     | V<br>V            |

| VL               | Logic Supply Range             | LTM2886-S<br>LTM2886-I                                    | • | 1.62<br>3 | 5             | 5.5<br>5.5     | V<br>V            |

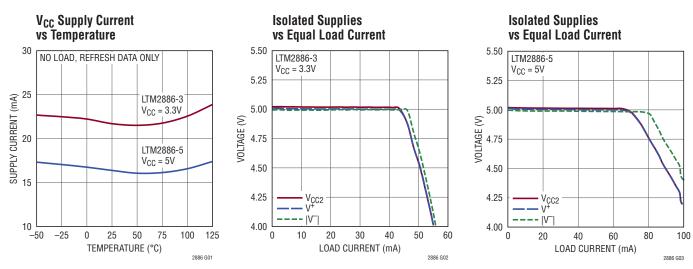

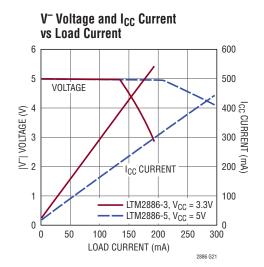

| I <sub>CC</sub>  | Input Supply Current           | ON = 0V<br>LTM2886-3, No Load<br>LTM2886-5, No Load       | • |           | 0<br>25<br>19 | 10<br>37<br>27 | μA<br>mA<br>mA    |

| IL               | Logic Supply Current           | ON = OV<br>LTM2886-S, $ON = V_L$<br>LTM2886-I, $ON = V_L$ | • |           | 0<br>10       | 10<br>150      | μΑ<br>μΑ<br>μΑ    |

| Output Su        | upplies                        |                                                           |   |           |               |                |                   |

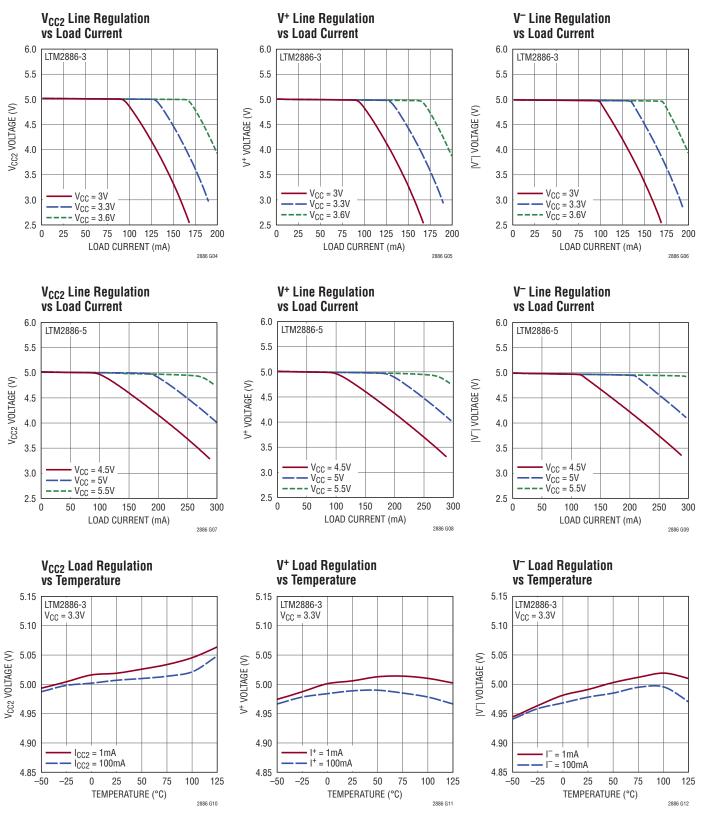

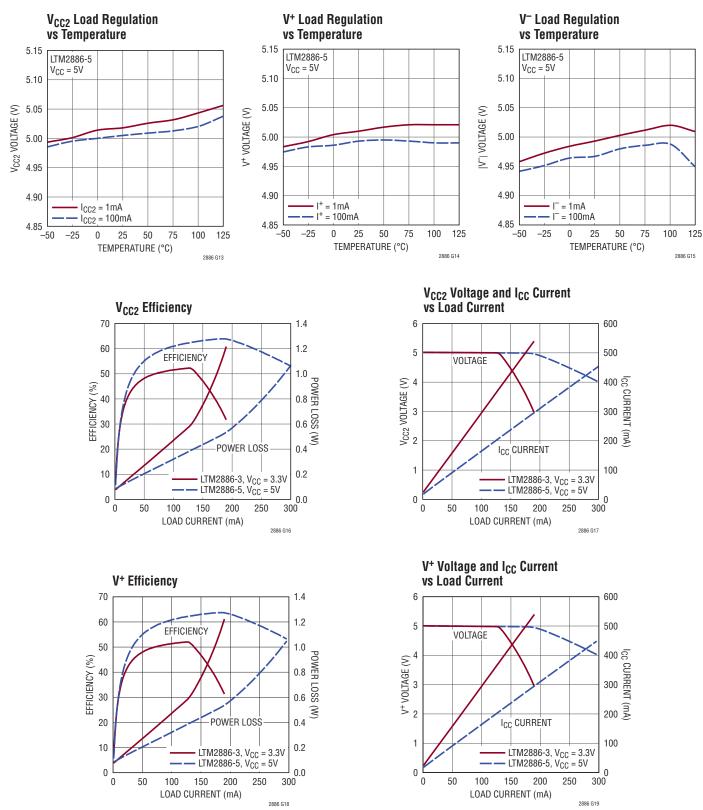

| V <sub>CC2</sub> | Regulated Output Voltage       | No Load, AV <sub>CC2</sub> OPEN                           | • | 4.75      | 5             | 5.25           | V                 |

|                  | Output Voltage Operating Range | (Note 2)                                                  |   | 3         |               | 5.5            | V                 |

|                  | Line Regulation                | $I_{LOAD} = 1$ mA, MIN $\leq V_{CC} \leq$ MAX             | • |           | 2             | 7.5            | mV                |

|                  | Load Regulation                | I <sub>LOAD</sub> = 1mA to 100mA                          | • |           | 15            | 100            | mV                |

|                  | ADJ Pin Voltage                | I <sub>LOAD</sub> = 1mA to 100mA                          | • | 1.15      | 1.220         | 1.27           | V                 |

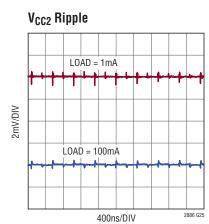

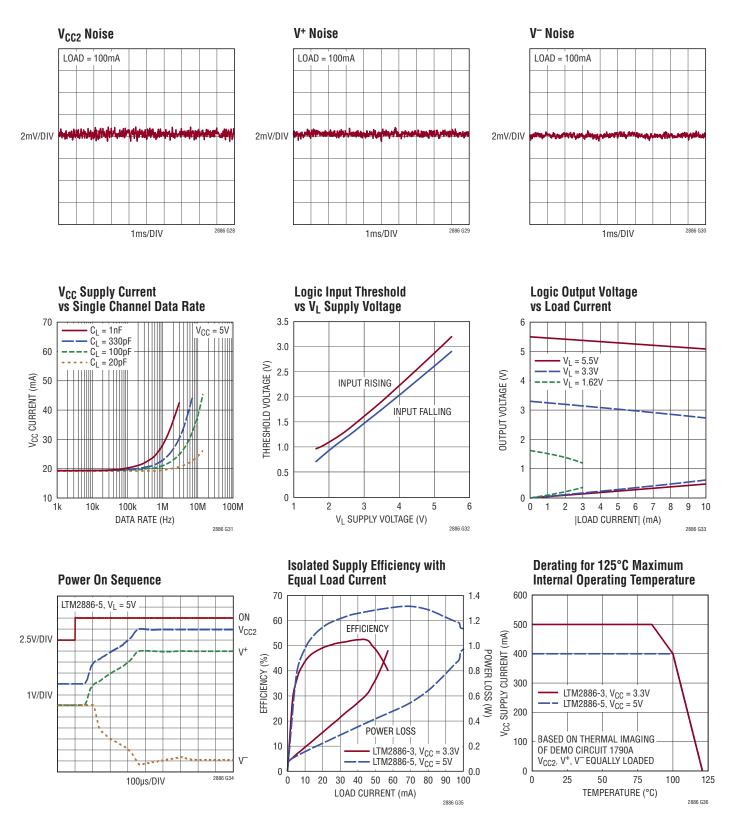

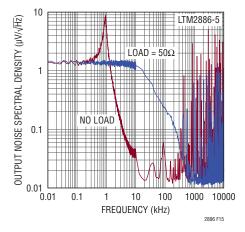

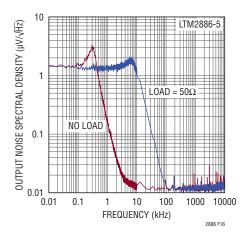

|                  | Voltage Ripple                 | I <sub>LOAD</sub> = 100mA (Note 2)                        |   |           | 1             |                | mV <sub>RMS</sub> |

|                  | Efficiency                     | LTM2886-5, I <sub>LOAD</sub> = 100mA (Note 2)             |   |           | 61            |                | %                 |

| I <sub>CC2</sub> | Output Short Circuit Current   | $V_{CC2} = 0V$                                            |   |           | 150           |                | mA                |

|                  | Current Limit                  | $\Delta V_{\rm CC2} = -5\%$                               | • | 90        |               |                | mA                |

| V <sup>+</sup>   | Regulated Output Voltage       | No Load                                                   | • | 4.8       | 5             | 5.2            | V                 |

|                  | Line Regulation                | $I_{LOAD} = 1mA, MIN \le V_{CC} \le MAX$                  | • |           | 2             | 7.5            | mV                |

|                  | Load Regulation                | I <sub>LOAD</sub> = 1mA to 100mA                          | • |           | 35            | 150            | mV                |

|                  | Voltage Ripple                 | I <sub>LOAD</sub> = 100mA (Note 2)                        |   |           | 1             |                | mV <sub>RMS</sub> |

|                  | Efficiency                     | LTM2886-5, I <sub>LOAD</sub> = 100mA (Note 2)             |   |           | 61            |                | %                 |

| +                | Output Short Circuit Current   | $V^+ = 0V$                                                |   |           | 150           |                | mA                |

|                  | Current Limit                  | $\Delta V^{+} = -5\%$                                     | • | 90        |               |                | mA                |

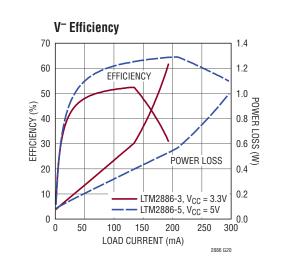

| V-               | Regulated Output Voltage       | No Load                                                   | • | -4.8      | -5            | -5.2           | V                 |

|                  | Line Regulation                | $I_{LOAD}$ = -1mA, MIN $\leq V_{CC} \leq MAX$             | • |           | 5             | 15             | mV                |

|                  | Load Regulation                | I <sub>LOAD</sub> = 1mA to 100mA                          | • |           | 35            | 150            | mV                |

|                  | Voltage Ripple                 | I <sub>LOAD</sub> = 100mA (Note 2)                        |   |           | 1             |                | mV <sub>RMS</sub> |

|                  | Efficiency                     | LTM2886-5, I <sub>LOAD</sub> = 100mA (Note 2)             |   |           | 61            |                | %                 |

| I-               | Output Short-Circuit Current   | V <sup>-</sup> = 0V                                       |   |           | 150           |                | mA                |

|                  | Current Limit                  | $\Delta V^{-} = 5\%$                                      |   | 90        |               |                | mA                |

**ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the specified operating temperature range, otherwise specifications are at  $T_A = 25$ °C. LTM2886-3 V<sub>CC</sub> = 3.3V, LTM2886-5 V<sub>CC</sub> = 5V, V<sub>L</sub> = 3.3V, and GND = GND2 = 0V, ON = V<sub>L</sub> unless otherwise noted. Specifications apply to all options unless otherwise noted.

| SYMBOL           | PARAMETER                | CONDITIONS                                                                                                                                                                                                                                                                                                                                                           |                                         | MIN                                                                       | ТҮР                                              | MAX                                                                       | UNITS                      |

|------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|---------------------------------------------------------------------------|--------------------------------------------------|---------------------------------------------------------------------------|----------------------------|

| Logic/SP         | I                        |                                                                                                                                                                                                                                                                                                                                                                      |                                         |                                                                           |                                                  |                                                                           |                            |

| V <sub>ITH</sub> | Input Threshold Voltage  | $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                               | •                                       | 0.25 • V <sub>L</sub><br>0.33 • V <sub>L</sub><br>0.33 • V <sub>CC2</sub> |                                                  | 0.75 • V <sub>L</sub><br>0.67 • V <sub>L</sub><br>0.67 • V <sub>CC2</sub> | V<br>V<br>V                |

| I <sub>INL</sub> | Input Current            |                                                                                                                                                                                                                                                                                                                                                                      | •                                       |                                                                           |                                                  | ±1                                                                        | μA                         |

| V <sub>HYS</sub> | Input Hysteresis         |                                                                                                                                                                                                                                                                                                                                                                      |                                         |                                                                           | 150                                              |                                                                           | mV                         |

| V <sub>0H</sub>  | Output High Voltage      | D01, D02, SD0, $I_{LOAD} = -1mA, 1.62V \le V_L < 3V, \\ I_{LOAD} = -4mA, 3V \le V_L \le 5.5V$                                                                                                                                                                                                                                                                        | •                                       | V <sub>L</sub> - 0.4                                                      |                                                  |                                                                           | V                          |

|                  |                          | 01, SCK2, SDI2, $\overline{CS2}$ , $I_{LOAD} = -4mA$                                                                                                                                                                                                                                                                                                                 | •                                       | V <sub>CC2</sub> - 0.4                                                    |                                                  |                                                                           | V                          |

| V <sub>OL</sub>  | Output Low Voltage       | D01, D02, SD0, $I_{LOAD}$ = 1mA, 1.62V $\leq$ V <sub>L</sub> $<$ 3V, $I_{LOAD}$ = 4mA, 3V $\leq$ V <sub>L</sub> $\leq$ 5.5V                                                                                                                                                                                                                                          | •                                       |                                                                           |                                                  | 0.4                                                                       | V                          |

|                  |                          | 01, SCK2, SDI2, $\overline{CS2}$ , $I_{LOAD} = 4mA$                                                                                                                                                                                                                                                                                                                  | •                                       |                                                                           |                                                  | 0.4                                                                       | V                          |

| I <sub>SC</sub>  | Short-Circuit Current    | $\begin{array}{l} \text{OV} \leq (\text{D01, D02, SD0}) \leq \text{V}_L \\ \text{OV} \leq (\text{O1, SCK2, SD12, } \overrightarrow{\text{CS2}}) \leq \text{V}_{\text{CC2}} \end{array}$                                                                                                                                                                              | •                                       |                                                                           | ±60                                              | ±85                                                                       | mA<br>mA                   |

| I <sup>2</sup> C |                          |                                                                                                                                                                                                                                                                                                                                                                      |                                         | ~                                                                         |                                                  |                                                                           |                            |

| V <sub>IL</sub>  | Low Level Input Voltage  | SCL, SDA<br>SDA2                                                                                                                                                                                                                                                                                                                                                     | •                                       |                                                                           |                                                  | 0.3 • V <sub>L</sub><br>0.3 • V <sub>CC2</sub>                            | V<br>V                     |

| V <sub>IH</sub>  | High Level Input Voltage | SCL, SDA<br>SDA2                                                                                                                                                                                                                                                                                                                                                     | •                                       | 0.7 • V <sub>L</sub><br>0.7 • V <sub>CC2</sub>                            |                                                  |                                                                           | V<br>V                     |

| I <sub>INL</sub> | Input Current            | SCL, SDA = $V_L$ or 0V<br>SDA2 = $V_{CC2}$ , SDA2 = $V_{CC2}$ = 0V                                                                                                                                                                                                                                                                                                   | •                                       |                                                                           |                                                  | ±1<br>±1                                                                  | μA<br>μA                   |

| V <sub>HYS</sub> | Input Hysteresis         | SCL, SDA<br>SDA2                                                                                                                                                                                                                                                                                                                                                     |                                         |                                                                           | 0.05 • V <sub>L</sub><br>0.05 • V <sub>CC2</sub> |                                                                           | V<br>V                     |

| V <sub>OH</sub>  | Output High Voltage      | SCL2, $I_{LOAD} = -2mA$<br>DO2, $I_{LOAD} = -2mA$                                                                                                                                                                                                                                                                                                                    | •                                       | $V_{CC2} - 0.4 V_L - 0.4$                                                 |                                                  |                                                                           | V<br>V                     |

| V <sub>OL</sub>  | Output Low Voltage       | $\begin{array}{l} \text{SDA, } I_{\text{LOAD}} = 3\text{mA} \\ \text{DO2, } I_{\text{LOAD}} = 2\text{mA} \\ \text{SCL2, } I_{\text{LOAD}} = 2\text{mA} \\ \text{SDA2, No Load, SDA} = 0\text{V, } 4.5\text{V} \leq \text{V}_{\text{CC2}} < 5.5\text{V} \\ \text{SDA2, No Load, SDA} = 0\text{V, } 3\text{V} \leq \text{V}_{\text{CC2}} < 4.5\text{V} \\ \end{array}$ | ••••••••••••••••••••••••••••••••••••••• |                                                                           | 0.3                                              | 0.4<br>0.4<br>0.45<br>0.55                                                | V<br>V<br>V<br>V<br>V      |

| CIN              | Input Pin Capacitance    | SCL, SDA, SDA2 (Note 2)                                                                                                                                                                                                                                                                                                                                              | •                                       |                                                                           |                                                  | 10                                                                        | pF                         |

| C <sub>B</sub>   | Bus Capacitive Load      | $\begin{array}{l} SCL2, Standard Speed (Note 2)\\ SCL2, Fast Speed\\ SDA, SDA2, SR \geq 1V/\mu s, Standard Speed (Note 2)\\ SDA, SDA2, SR \geq 1V/\mu s, Fast Speed \end{array}$                                                                                                                                                                                     | •<br>•<br>•                             |                                                                           |                                                  | 400<br>200<br>400<br>200                                                  | pF<br>pF<br>pF<br>pF       |

|                  | Minimum Bus Slew Rate    | SDA, SDA2                                                                                                                                                                                                                                                                                                                                                            | •                                       | 1                                                                         |                                                  |                                                                           | V/µs                       |

| I <sub>SC</sub>  | Short-Circuit Current    | $\begin{array}{l} \text{SDA2} = 0,  \text{SDA} = \text{V}_L \\ 0\text{V} \leq \text{SCL2} \leq \text{V}_{\text{CC2}} \\ 0\text{V} \leq \text{D02} \leq \text{V}_L \\ \text{SDA} = 0,  \text{SDA2} = \text{V}_{\text{CC2}} \\ \text{SDA} = \text{V}_L,  \text{SDA2} = 0 \end{array}$                                                                                  | •                                       |                                                                           | ±30<br>±30<br>6<br>-1.8                          | 100                                                                       | mA<br>mA<br>mA<br>mA<br>mA |

| ESD (HBI         | M) (Note 2)              |                                                                                                                                                                                                                                                                                                                                                                      |                                         |                                                                           |                                                  |                                                                           |                            |

|                  | Isolation Boundary       | $(V_{CC2}, V^+, V^-, GND2)$ to $(V_{CC}, V_L, GND)$                                                                                                                                                                                                                                                                                                                  |                                         |                                                                           | ±10                                              |                                                                           | kV                         |

**SWITCHING CHARACTERISTICS** The • denotes the specifications which apply over the specified operating temperature range, otherwise specifications are at  $T_A = 25$ °C. LTM2886-3 V<sub>CC</sub> = 3.3V, LTM2886-5 V<sub>CC</sub> = 5V, V<sub>L</sub> = 3.3V, and GND = GND2 = 0V, ON = V<sub>L</sub> unless otherwise noted. Specifications apply to all options unless otherwise noted.

| SYMBOL                              | PARAMETER                                        | CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                      |   | MIN      | ТҮР               | MAX               | UNITS          |

|-------------------------------------|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------|-------------------|-------------------|----------------|

| Logic                               |                                                  |                                                                                                                                                                                                                                                                                                                                                                                                 |   |          |                   |                   |                |

|                                     | Maximum Data Rate                                | $DI1 \rightarrow 01$ , $Ix \rightarrow DOx$ , $C_L = 15pF$ (Note 3)                                                                                                                                                                                                                                                                                                                             |   | 10       |                   |                   | MHz            |

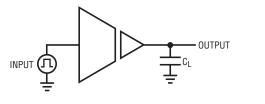

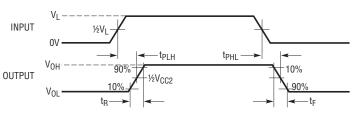

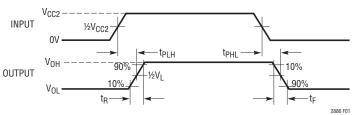

| t <sub>PHL</sub> , t <sub>PLH</sub> | Propagation Delay                                | C <sub>L</sub> = 15pF (Figure 1)                                                                                                                                                                                                                                                                                                                                                                |   | 35       | 60                | 100               | ns             |

| t <sub>R</sub>                      | Rise Time                                        | C <sub>L</sub> = 15pF (Figure 1)<br>LTM2886-1, DO2, C <sub>L</sub> = 15pF (Figure 1)                                                                                                                                                                                                                                                                                                            | • |          | 3<br>20           | 12.5<br>35        | ns<br>ns       |

| t <sub>F</sub>                      | Fall Time                                        | C <sub>L</sub> = 15pF (Figure 1)<br>LTM2886-1, DO2, C <sub>L</sub> = 15pF (Figure 1)                                                                                                                                                                                                                                                                                                            | • |          | 3<br>20           | 12.5<br>35        | ns<br>ns       |

| SPI                                 |                                                  |                                                                                                                                                                                                                                                                                                                                                                                                 |   |          |                   |                   |                |

|                                     | Maximum Data Rate                                | Bidirectional Communication (Note 3)<br>Unidirectional Communication (Note 3)                                                                                                                                                                                                                                                                                                                   | • | 4<br>8   |                   |                   | MHz<br>MHz     |

| t <sub>PHL</sub> , t <sub>PLH</sub> | Propagation Delay                                | C <sub>L</sub> = 15pF (Figure 1)                                                                                                                                                                                                                                                                                                                                                                |   | 35       | 60                | 100               | ns             |

| t <sub>PWU</sub>                    | Output Pulse Width Uncertainty                   | SDO, SDI2, CS2 (Note 2)                                                                                                                                                                                                                                                                                                                                                                         |   |          |                   | ±50               | ns             |

| t <sub>R</sub>                      | Rise Time                                        | C <sub>L</sub> = 15pF (Figure 1)                                                                                                                                                                                                                                                                                                                                                                |   |          | 3                 | 12.5              | ns             |

| t <sub>F</sub>                      | Fall Time                                        | C <sub>L</sub> = 15pF (Figure 1)                                                                                                                                                                                                                                                                                                                                                                |   |          | 3                 | 12.5              | ns             |

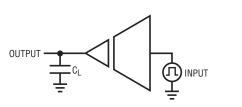

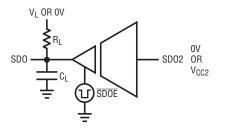

| t <sub>PZH,</sub> t <sub>PZL</sub>  | Output Enable Time                               | $\overline{\text{SDOE}} = \downarrow$ , R <sub>L</sub> = 1k $\Omega$ , C <sub>L</sub> = 15pF (Figure 2)                                                                                                                                                                                                                                                                                         |   |          |                   | 50                | ns             |

| t <sub>PHZ,</sub> t <sub>PLZ</sub>  | Output Disable Time                              | $\overline{\text{SDOE}} = \uparrow$ , R <sub>L</sub> = 1k $\Omega$ , C <sub>L</sub> = 15pF (Figure 2)                                                                                                                                                                                                                                                                                           |   |          |                   | 50                | ns             |

| l <sup>2</sup> C                    |                                                  |                                                                                                                                                                                                                                                                                                                                                                                                 |   |          |                   |                   |                |

|                                     | Maximum Data Rate                                | (Note 3)                                                                                                                                                                                                                                                                                                                                                                                        |   | 400      |                   |                   | kHz            |

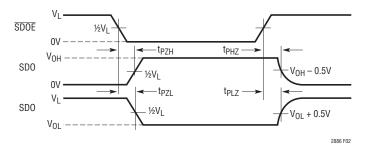

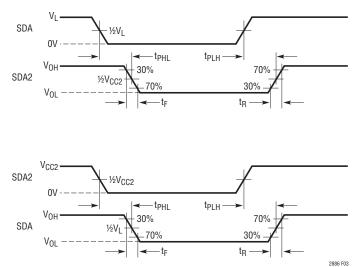

| t <sub>PHL</sub> , t <sub>PLH</sub> | Propagation Delay                                | $\begin{array}{l} \text{SCL} \rightarrow \text{SCL2, } \text{C}_{\text{L}} = 15\text{pF} \text{ (Figure 1)} \\ \text{SDA} \rightarrow \text{SDA2, } \text{R}_{\text{L}} = 0\text{pen, } \text{C}_{\text{L}} = 15\text{pF} \text{ (Figure 3)} \\ \text{SDA2} \rightarrow \text{SDA, } \text{R}_{\text{L}} = 1.1\text{k}\Omega, \text{C}_{\text{L}} = 15\text{pF} \text{ (Figure 3)} \end{array}$ | • |          | 150<br>150<br>300 | 225<br>250<br>500 | ns<br>ns<br>ns |

| t <sub>PWU</sub>                    | Output Pulse Width Uncertainty                   | SDA, SDA2 (Note 2)                                                                                                                                                                                                                                                                                                                                                                              |   |          |                   | ±50               | ns             |

| t <sub>HD;DAT</sub>                 | Data Hold Time                                   | (Note 2)                                                                                                                                                                                                                                                                                                                                                                                        |   |          | 600               |                   | ns             |

| t <sub>R</sub>                      | Rise Time                                        | SDA2, $C_L = 200pF$ (Figure 3)<br>SDA, $R_L = 1.1 k\Omega$ $C_L = 200pF$ (Figure 3)<br>SCL2, $C_L = 200pF$ (Figure 1)                                                                                                                                                                                                                                                                           | • | 40<br>40 |                   | 300<br>250<br>250 | ns<br>ns<br>ns |

| t <sub>F</sub>                      | Fall Time                                        | SDA2, $C_L = 200pF$ (Figure 3)<br>SDA, $R_L = 1.1k\Omega$ $C_L = 200pF$ (Figure 3)<br>SCL2, $C_L = 200pF$ (Figure 1)                                                                                                                                                                                                                                                                            | • | 40<br>40 |                   | 250<br>250<br>250 | ns<br>ns<br>ns |

| t <sub>SP</sub>                     | Pulse Width of Spikes Suppressed by Input Filter |                                                                                                                                                                                                                                                                                                                                                                                                 | • | 0        |                   | 50                | ns             |

| Power Su                            | pply                                             | •                                                                                                                                                                                                                                                                                                                                                                                               |   |          |                   |                   |                |

|                                     | Power-Up Time                                    | $\begin{array}{l} ON = \uparrow \text{ to } V_{CC2} \ (Min) \\ ON = \uparrow \text{ to } V^+ \ (Min) \\ ON = \uparrow \text{ to } V^- \ (Min) \end{array}$                                                                                                                                                                                                                                      | • |          | 0.6<br>0.6<br>0.6 | 5<br>5<br>5       | ms<br>ms<br>ms |

### **ISOLATION CHARACTERISTICS** $T_A = 25 \degree C$ .

| SYMBOL                      | PARAMETER                           | CONDITIONS                                                                                                                                      | MIN             | ТҮР   | MAX | UNITS                                |

|-----------------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------|-----|--------------------------------------|

| V <sub>ISO</sub>            | Rated Dielectric Insulation Voltage | 1 Minute, Derived from 1 Second Test<br>1 Second (Notes 5, 6)                                                                                   | 2500<br>3000    |       |     | V <sub>RMS</sub><br>V <sub>RMS</sub> |

|                             | Common Mode Transient Immunity      | LTM2886-3 V <sub>CC</sub> = 3.3V, LTM2885-5 V <sub>CC</sub> = 5V, V <sub>L</sub> = 0N = 3.3V, V <sub>CM</sub> = 1kV, $\Delta t$ = 33ns (Note 2) | 30              |       |     | kV/µs                                |

| V <sub>IORM</sub> Maximum C | Maximum Continuous Working Voltage  | (Notes 2, 5)                                                                                                                                    | 560             |       |     | V <sub>PEAK</sub> ,                  |

|                             |                                     |                                                                                                                                                 | 400             |       |     | V <sub>DC</sub><br>V <sub>RMS</sub>  |

|                             | Partial Discharge                   | $V_{PD} = 750V_{RMS}$ (Note 5)                                                                                                                  |                 |       | 5   | pC                                   |

| CTI                         | Comparative Tracking Index          | IEC 60112 (Note 2)                                                                                                                              | 600             |       |     | V <sub>RMS</sub>                     |

|                             | Depth of Erosion                    | IEC 60112 (Note 2)                                                                                                                              |                 | 0.017 |     | mm                                   |

| DTI                         | Distance Through Insulation         | (Note 2)                                                                                                                                        |                 | 0.06  |     | mm                                   |

|                             | Input to Output Resistance          | (Notes 2, 5)                                                                                                                                    | 10 <sup>9</sup> |       |     | Ω                                    |

|                             | Input to Output Capacitance         | (Notes 2, 5)                                                                                                                                    |                 | 6     |     | pF                                   |

|                             | Creepage Distance                   | (Note 2)                                                                                                                                        |                 | 9.5   |     | mm                                   |

Note 1: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

Note 2: Guaranteed by design and not subject to production test.

Note 3: Maximum Data rate is guaranteed by other measured parameters and is not tested directly.

Note 4: This Module includes overtemperature protection that is intended to protect the device during momentary overload conditions. Junction temperature will exceed 125°C when overtemperature protection is active. Continuous operation above specified maximum operating junction temperature may result in device degradation or failure.

Note 5: Device considered a 2-terminal device. Pin group A1 through B8 shorted together and pin group K1 through L8 shorted together. **Note 6:** The rated dielectric insulation voltage should not be interpreted as a continuous voltage rating.

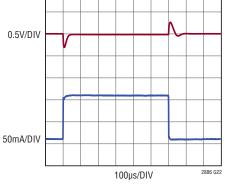

# V<sub>CC2</sub> Transient Response 100mA Load Step

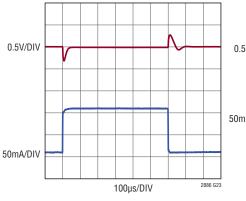

#### V<sup>+</sup> Transient Response 100mA Load Step

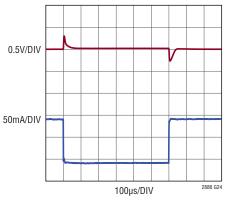

#### V<sup>-</sup> Transient Response 100mA Load Step

2mV/DIV

### PIN FUNCTIONS (LTM2886-I)

#### Logic Side

**D02 (A1):** Digital Output, Referenced to  $V_L$  and GND. Logic output connected to I2 through isolation barrier. Under the condition of an isolation communication failure this output is in a high impedance state.

**DNC (A2):** Do Not Connect. Pin connected internally.

**SCL (A3):** Serial I<sup>2</sup>C Clock Input, Referenced to  $V_L$  and GND. Logic input connected to isolated side SCL2 pin through isolation barrier. Clock is unidirectional from logic to isolated side. Do not float.

**SDA (A4):** Serial I<sup>2</sup>C Data Pin, Referenced to V<sub>L</sub> and GND. Bidirectional logic pin connected to isolated side SDA2 pin through isolation barrier. Under the condition of an isolation communication failure this pin is in a high impedance state. Do not float.

**DI1 (A5):** Digital Input, Referenced to  $V_L$  and GND. Logic input connected to O1 through isolation barrier. The logic state on DI1 translates to the same logic state on O1. Do not float.

GND (A6, B2 to B6): Circuit Ground.

**ON (A7):** Enable, Referenced to  $V_L$  and GND. Enables power and data communication through the isolation barrier. If ON is high the part is enabled and power and communications are functional to the isolated side. If ON is low the logic side is held in reset, all digital outputs are in a high impedance state, and the isolated side is unpowered. Do not float.

$V_L$  (A8): Logic Supply. Interface supply voltage for pins D11, SCL, SDA, D01, D02, and ON. Operating voltage is 3V to 5.5V. Internally bypassed with 1µF.

**D01 (B1):** Digital Output, Referenced to  $V_L$  and GND. Logic output connected to 11 through isolation barrier. Under the condition of an isolation communication failure this output is in a high impedance state.

$V_{CC}$  (B7 to B8): Supply Voltage. Operating voltage is 3V to 3.6V for LTM2886-3 and 4.5V to 5.5V for LTM2886-5. Internally bypassed with 2.2 $\mu$ F.

### Isolated Side

I2 (L1): Digital Input, Referenced to  $V_{CC2}$  and GND2. Logic input connected to DO2 through isolation barrier.

The logic state on I2 translates to the same logic state on DO2. Do not float.

DNC (L2): Do Not Connect. Pin connected internally.

**SCL2 (L3):** Serial I<sup>2</sup>C Clock Output, Referenced to  $V_{CC2}$  and GND2. Logic output connected to logic side SCL pin through isolation barrier. Clock is unidirectional from logic to isolated side. SCL2 has a push-pull output stage, do not connect an external pull-up device. Under the condition of an isolation communication failure this output defaults to a high state.

**SDA2 (L4):** Serial I<sup>2</sup>C Data Pin, Referenced to  $V_{CC2}$  and GND2. Bidirectional logic pin connected to logic side SDA pin through isolation barrier. Output is biased high by a 1.8mA current source. Do not connect an external pullup device to SDA2. Under the condition of an isolation communication failure this output defaults to a high state.

**01 (L5):** Digital Output, Referenced to  $V_{CC2}$  and GND2. Logic output connected to DI1 through isolation barrier. Under the condition of an isolation communication failure 01 defaults to a high state.

$V_{CC2}$  (L6): 3V to 5.5V Adjustable Isolated Supply Voltage. Internally generated from V<sub>CC</sub> by an isolated DC/DC converter and regulated to 5V with no external components. Internally bypassed with 2.2µF.

**V**<sup>-</sup> (L7): -5V Nominal Isolated Supply Voltage. Internally generated from V<sub>CC</sub> by an isolated DC/DC converter and regulated to -5V with no external components. Internally bypassed with 2.2µF.

**V<sup>+</sup>** (L8): 5V Nominal Isolated Supply Voltage. Internally generated from  $V_{CC}$  by an isolated DC/DC converter and regulated to 5V with no external components. Internally bypassed with 2.2µF.

**I1 (K1):** Digital Input, Referenced to  $V_{CC2}$  and GND2. Logic input connected to DO1 through isolation barrier. The logic state on I1 translates to the same logic state on DO1. Do not float.

GND2 (K2 to K5, K7, K8): Isolated Ground.

**AV<sub>CC2</sub> (K6):** 5V Nominal Isolated Supply Voltage Adjust. The adjust pin voltage is 1.22V referenced to GND2. See Applications Information section for details.

### PIN FUNCTIONS (LTM2886-S)

#### Logic Side

**SDO (A1):** Serial SPI Digital Output, Referenced to  $V_L$  and GND. Logic output connected to isolated side SDO2 pin through isolation barrier. Under the condition of an isolation communication failure this output is in a high impedance state.

**D02 (A2):** Digital Output, Referenced to  $V_L$  and GND. Logic output connected to I2 through isolation barrier. Under the condition of an isolation communication failure this output is in a high impedance state.

**SCK (A3):** Serial SPI Clock Input, Referenced to  $V_L$  and GND. Logic input connected to isolated side SCK2 pin through isolation barrier. Do not float.

**SDI (A4):** Serial SPI Data Input, Referenced to  $V_L$  and GND. Logic input connected to isolated side SDI2 pin through isolation barrier. Do not float.

$\overline{\text{CS}}$  (A5): Serial SPI Chip Select, Referenced to V<sub>L</sub> and GND. Logic input connected to isolated side  $\overline{\text{CS2}}$  pin through isolation barrier. Do not float.

**SDOE** (A6): Serial SPI Data Output Enable, Referenced to  $V_L$  and GND. A logic high on SDOE places the logic side SDO pin in a high impedance state, a logic low enables the output. Do not float.

**ON (A7):** Enable, Referenced to  $V_L$  and GND. Enables power and data communication through the isolation barrier. If ON is high the part is enabled and power and communications are functional to the isolated side. If ON is low the logic side is held in reset, all digital outputs are in a high impedance state, and the isolated side is unpowered. Do not float.

$V_L$  (A8): Logic Supply. Interface supply voltage for pins SDI, SCK, SDO, SDOE, DO1, DO2,  $\overline{CS}$ , and ON. Operating voltage is 1.62V to 5.5V. Internally bypassed with 1µF.

**D01 (B1):** Digital Output, Referenced to  $V_L$  and GND. Logic output connected to 11 through isolation barrier. Under the condition of an isolation communication failure this output is in a high impedance state.

GND (B2 to B6): Circuit Ground.

$V_{CC}$  (B7 to B8): Supply Voltage. Operating voltage is 3V to 3.6V for LTM2886-3 and 4.5V to 5.5V for LTM2886-5. Internally bypassed with 2.2µF.

#### **Isolated Side**

**SD02 (L1):** Serial SPI Digital Input, Referenced to  $V_{CC2}$  and GND2. Logic input connected to logic side SDO pin through isolation barrier. Do not float.

**12 (L2):** Digital Input, Referenced to  $V_{CC2}$  and GND2. Logic input connected to DO2 through isolation barrier. The logic state on I2 translates to the same logic state on DO2. Do not float.

**SCK2 (L3):** Serial SPI Clock Output, Referenced to  $V_{CC2}$  and GND2. Logic output connected to logic side SCK pin through isolation barrier. Under the condition of an isolation communication failure this output defaults to a low state.

**SDI2 (L4):** Serial SPI Data Output, Referenced to  $V_{CC2}$  and GND2. Logic output connected to logic side SDI pin through isolation barrier. Under the condition of an isolation communication failure this output defaults to a low state.

**CS2** (L5): Serial SPI Chip Select, Referenced to  $V_{CC2}$  and GND2. Logic output connected to logic side  $\overline{CS}$  pin through isolation barrier. Under the condition of an isolation communication failure this output defaults to a high state.

$V_{CC2}$  (L6): 3V to 5.5V Adjustable Isolated Supply Voltage. Internally generated from V<sub>CC</sub> by an isolated DC/DC converter and regulated to 5V with no external components. Internally bypassed with 2.2µF.

**V**<sup>-</sup> (L7): -5V Nominal Isolated Supply Voltage. Internally generated from V<sub>CC</sub> by an isolated DC/DC converter and regulated to -5V with no external components. Internally bypassed with 2.2µF.

**V<sup>+</sup>** (L8): 5V Nominal Isolated Supply Voltage. Internally generated from  $V_{CC}$  by an isolated DC/DC converter and regulated to 5V with no external components. Internally bypassed with 2.2µF.

**I1 (K1):** Digital Input, Referenced to  $V_{CC2}$  and GND2. Logic input connected to DO1 through isolation barrier. The logic state on I1 translates to the same logic state on DO1. Do not float.

GND2 (K2 to K5, K7, K8): Isolated Ground.

**AV<sub>CC2</sub> (K6):** 5V Nominal Isolated Supply Voltage Adjust. The adjust pin voltage is 1.22V Referenced to GND2. See Applications Information section for details.

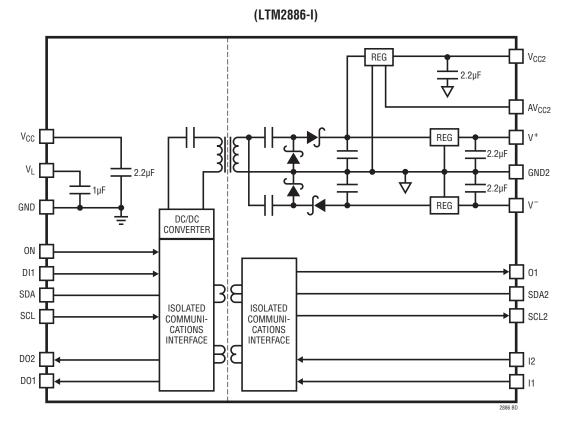

## **BLOCK DIAGRAMS**

Rev C

5

### **TEST CIRCUITS**

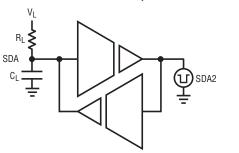

Figure 1. Logic Timing Measurements

#### Overview

The LTM2886 digital  $\mu$ Module isolator provides a galvanically-isolated robust logic interface, powered by an integrated, regulated DC/DC converter, complete with decoupling capacitors. The LTM2886 is ideal for use in networks where grounds can take on different voltages. Isolation in the LTM2886 blocks high voltage differences, eliminates ground loops and is extremely tolerant of common mode transients between ground planes. Error-free operation is maintained through common mode events greater than 30kV/ $\mu$ s providing excellent noise isolation.

#### Isolator µModule Technology

The LTM2886 utilizes isolator  $\mu$ Module technology to translate signals and power across an isolation barrier. Signals on either side of the barrier are encoded into pulses and translated across the isolation boundary using coreless transformers formed in the  $\mu$ Module substrate. This system, complete with data refresh, error checking, safe shutdown on fail, and extremely high common mode immunity, provides a robust solution for bidirectional signal isolation. The  $\mu$ Module technology provides the means to combine the isolated DC/DC converter in one small package.

#### **DC/DC Converter**

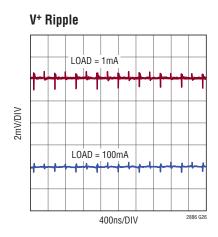

The LTM2886 contains a fully integrated DC/DC converter, including the transformer, so that no external components are necessary. The logic side contains a full-bridge driver, running at 1.6MHz, and is AC-coupled to a single transformer primary. A series DC blocking capacitor prevents transformer saturation due to driver duty cycle imbalance. The transformer scales the primary voltage, and is rectified by a voltage quadrupler. This topology eliminates transformer saturation caused by secondary imbalances.

The quadrupler is grounded in the middle producing symmetrical positive and negative voltage rails. The positive rail is post regulated with two low dropout regulators (LDOs) producing  $V_{CC2}$  and V<sup>+</sup>, the negative rail also has an LDO producing V<sup>-</sup>.

Each voltage rail is capable of producing 100mA of output current, total output power capability is approximately 1W. All voltage rails are bypassed with  $2.2\mu$ F ceramic capacitors.

### $\mathbf{V}_{L}$ Logic Supply

A separate logic supply pin V<sub>L</sub> allows the LTM2886 to interface with any logic signal from 1.62V to 5.5V (LTM2886-S) or 3V to 5.5V (LTM2886-I) as shown in Figure 4. Simply connect the desired logic supply to V<sub>L</sub>.

There is no interdependency between V<sub>CC</sub> and V<sub>L</sub>; they may simultaneously operate at any voltage within their specified operating ranges and sequence in any order. V<sub>L</sub> is bypassed internally by a 1 $\mu$ F capacitor.

Figure 4.  $V_{CC}$  and  $V_L$  Are Independent

### **Hot-Plugging Safely**

Caution must be exercised in applications where power is plugged into the LTM2886's power supplies,  $V_{CC}$  or  $V_L$ , due to the integrated ceramic decoupling capacitors. The parasitic cable inductance along with the high Q characteristics of ceramic capacitors can cause substantial ringing which could exceed the maximum voltage ratings and damage the LTM2886. Refer to Linear Technology Application Note 88, entitled Ceramic Input Capacitors Can Cause Overvoltage Transients for a detailed discussion and mitigation of this phenomenon.

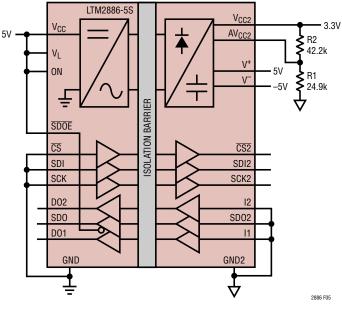

#### Isolated Supply Adjustable Operation

The V<sub>CC2</sub> isolated power rail is nominally 5V, but may be overdriven by adding two external resistors. The unadjusted output voltage represents the maximum for guaranteed performance. Figure 5 illustrates configuration for V<sub>CC2</sub> = 3.3V, V<sup>+</sup> and V<sup>-</sup> are fixed at 5V and -5V respectively.

Figure 5. Adjustable Voltage Rails

The output adjustment range for  $V_{CC2}$  is 3V to 5.5V.  $V_{CC2}$  output voltage is calculated by:

$V_{CC2} = 1.22V(1 + R2/R1)$

The value of R1 should be no greater than 24.9k to minimize errors in the output voltage caused by the  $AV_{CC2}$  pin bias current.

Operation at low output voltages may result in thermal shutdown due to low dropout regulator power dissipation.

### **Channel Timing Uncertainty**

Multiple channels are supported across the isolation boundary by encoding and decoding of the inputs and outputs. Up to three signals in each direction are assembled as a packet and transferred across the isolation barrier. The time required to transfer all 3 bits is 100ns maximum, and sets the limit for how often a signal can change on the opposite side of the barrier. Encoding transmission is independent for each data direction. The technique used assigns SCK or SCL on the logic side, and SDO2 or I2 on the isolated side, the highest priority such that there is no jitter on the associated output channels, only delay. This preemptive scheme will produce a certain amount of uncertainty on the other isolation channels. The resulting pulse width uncertainty on these low priority channels is typically ±6ns, but may vary up to ±50ns if the low priority channels are not encoded within the same high priority serial packet.

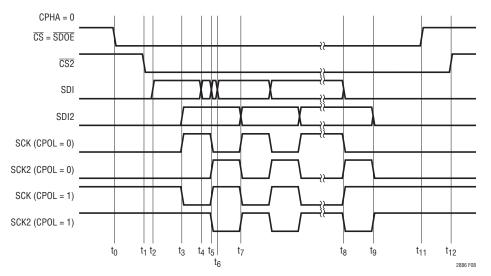

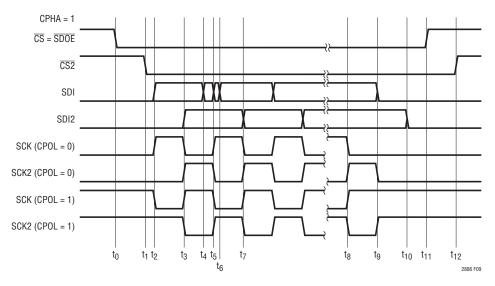

### Serial Peripheral Interface (SPI) Bus

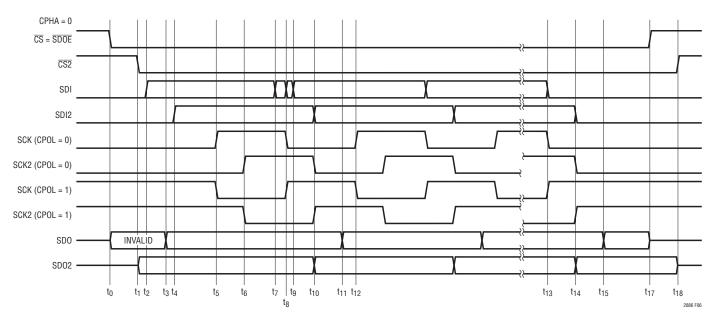

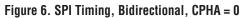

The LTM2886-S provides a SPI compatible isolated interface. The maximum data rate is a function of the inherent channel propagation delays, channel to channel pulse width uncertainty, and data direction requirements. Channel timing is detailed in Figures 6 through 9 and Tables 2 and 3. The SPI protocol supports four unique timing configurations defined by the clock polarity (CPOL) and clock phase (CPHA) summarized in Table 1.

#### Table 1. SPI Mode

| CPOL | CPHA | DATA TO (CLOCK) RELATIONSHIP |                  |  |

|------|------|------------------------------|------------------|--|

| 0    | 0    | Sample (Rising)              | Set-Up (Falling) |  |

| 0    | 1    | Set-Up (Rising)              | Sample (Falling) |  |

| 1    | 0    | Sample (Falling)             | Set-Up (Rising)  |  |

| 1    | 1    | Set-Up (Falling)             | Sample (Rising)  |  |

The maximum data rate for bidirectional communication is 4MHz, based on a synchronous system, as detailed in the timing waveforms. Slightly higher data rates may be achieved by skewing the clock duty cycle and minimizing the SDO to SCK set-up time, however the clock rate is still dominated by the system propagation delays. A discussion of the critical timing paths relative to Figures 6 and 7 follows.

- CS to SCK (master sample SDO, 1st SDO valid)

- $t_0 \rightarrow t_1 \quad \approx 50$ ns,  $\overline{CS}$  to  $\overline{CS2}$  propagation delay

- $\begin{array}{ll} t_1 \rightarrow t_{1+} & \mbox{Isolated slave device propagation} \\ (\mbox{response time}), \mbox{asserts SD02} \end{array}$

- $t_1 \rightarrow t_3 ~~ \approx 50 \text{ns}, \, \text{SDO2 to SDO propagation delay}$

- $t_3 \rightarrow t_5$  Set-up time for master SDO to SCK

- SDI to SCK (master data write to slave)

- $t_2 \rightarrow t_4$   $\approx 50$ ns, SDI to SDI2 propagation delay

- $t_5 \rightarrow t_6$   $\approx$  50ns, SCK to SCK2 propagation delay

- $\begin{array}{ll} t_2 \rightarrow t_5 & \geq 50 \text{ns, SDI to SCK, separate packet} \\ \text{non-zero set-up time} \end{array}$

- $\begin{array}{ll} t_4 \rightarrow t_6 & \geq 50 \text{ns, SDI2 to SCK2, separate packet} \\ \text{non-zero set-up time} \end{array}$

- SDO to SCK (master sample SDO, subsequent SDO valid)

- t<sub>8</sub> set-up data transition SDI and SCK

- $t_8 \rightarrow t_{10} \quad \approx 50 \text{ns, SDI to SDI2 and SCK to SCK2} \\ \text{propagation delay}$

- t<sub>10</sub> SDO2 data transition in response to SCK2

- $t_{10} \rightarrow t_{11}~$   $\approx 50 ns,~SDO2$  to SDO propagation delay

- $t_{11} \rightarrow t_{12}~$  Set-up time for master SDO to SCK

Maximum data rate for single direction communication, master to slave, is 8MHz, limited by the systems encoding/decoding scheme or propagation delay. Timing details for both variations of clock phase are shown in Figures 8 and 9 and Table 3.

Additional requirements to insure maximum data rate are:

- CS is transmitted prior to (asynchronous) or within the same (synchronous) data packet as SDI

- SDI and SCK set-up data transition occur within the same data packet. Referencing Figure 6, SDI can precede SCK by up to 13ns  $(t_7 \rightarrow t_8)$  or lag SCK by 3ns  $(t_8 \rightarrow t_9)$  and not violate this requirement. Similarly in Figure 8, SDI can precede SCK by up to 13ns  $(t_4 \rightarrow t_5)$  or lag SCK by 3ns  $(t_5 \rightarrow t_6)$ .

#### Table 2. Bidirectional SPI Timing Event Description

| TIME                                                                   | CPHA | EVENT DESCRIPTION                                                                                                                                                                      |

|------------------------------------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| to                                                                     | 0, 1 | Asynchronous chip select, may be synchronous to SDI but may not lag by more than 3ns. Logic side slave data output enabled, initial data is not equivalent to slave device data output |

| t <sub>0</sub> to t <sub>1,</sub> t <sub>17</sub> to t <sub>18</sub>   | 0, 1 | Propagation delay chip select, logic to isolated side, 50ns typical                                                                                                                    |

| t <sub>1</sub>                                                         | 0, 1 | Slave device chip select output data enable                                                                                                                                            |

| t <sub>2</sub>                                                         | 0    | Start of data transmission, data set-up                                                                                                                                                |

|                                                                        | 1    | Start of transmission, data and clock set-up. Data transition must be within -13ns to 3ns of clock edge                                                                                |

| t <sub>1</sub> to t <sub>3</sub>                                       | 0, 1 | Propagation delay of slave data, isolated to logic side, 50ns typical                                                                                                                  |

| t <sub>3</sub>                                                         | 0, 1 | Slave data output valid, logic side                                                                                                                                                    |

| t <sub>2</sub> to t <sub>4</sub>                                       | 0    | Propagation delay of data, logic side to isolated side                                                                                                                                 |

|                                                                        | 1    | Propagation delay of data and clock, logic side to isolated side                                                                                                                       |

| t <sub>5</sub>                                                         | 0, 1 | Logic side data sample time, half clock period delay from data set-up transition                                                                                                       |

| t <sub>5</sub> to t <sub>6</sub>                                       | 0, 1 | Propagation delay of clock, logic to isolated side                                                                                                                                     |

| t <sub>6</sub>                                                         | 0, 1 | Isolated side data sample time                                                                                                                                                         |

| t <sub>8</sub>                                                         | 0, 1 | Synchronous data and clock transition, logic side                                                                                                                                      |

| t <sub>7</sub> to t <sub>8</sub>                                       | 0, 1 | Data to clock delay, must be ≤13ns                                                                                                                                                     |

| t <sub>8</sub> to t <sub>9</sub>                                       | 0, 1 | Clock to data delay, must be ≤3ns                                                                                                                                                      |

| t <sub>8</sub> to t <sub>10</sub>                                      | 0, 1 | Propagation delay clock and data, logic to isolated side                                                                                                                               |

| t <sub>10</sub> , t <sub>14</sub>                                      | 0, 1 | Slave device data transition                                                                                                                                                           |

| t <sub>10</sub> to t <sub>11,</sub> t <sub>14</sub> to t <sub>15</sub> | 0, 1 | Propagation delay slave data, isolated to logic side                                                                                                                                   |

| t <sub>11</sub> to t <sub>12</sub>                                     | 0, 1 | Slave data output to sample clock set-up time                                                                                                                                          |

| t <sub>13</sub>                                                        | 0    | Last data and clock transition logic side                                                                                                                                              |

|                                                                        | 1    | Last sample clock transition logic side                                                                                                                                                |

| t <sub>13</sub> to t <sub>14</sub>                                     | 0    | Propagation delay data and clock, logic to isolated side                                                                                                                               |

|                                                                        | 1    | Propagation delay clock, logic to isolated side                                                                                                                                        |

| t <sub>15</sub>                                                        | 0    | Last slave data output transition logic side                                                                                                                                           |

|                                                                        | 1    | Last slave data output and data transition, logic side                                                                                                                                 |

| t <sub>15</sub> to t <sub>16</sub>                                     | 1    | Propagation delay data, logic to isolated side                                                                                                                                         |

| t <sub>17</sub>                                                        | 0, 1 | Asynchronous chip select transition, end of transmission. Disable slave data output logic side                                                                                         |

| t <sub>18</sub>                                                        | 0, 1 | Chip select transition isolated side, slave data output disabled                                                                                                                       |

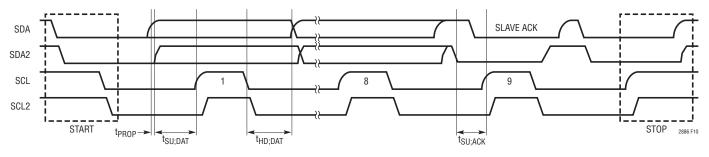

#### Inter-IC Communication (I<sup>2</sup>C) Bus

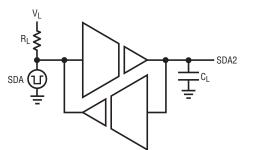

The LTM2886-I provides an I<sup>2</sup>C compatible isolated interface. Clock (SCL) is unidirectional, supporting master mode only, and data (SDA) is bidirectional. The maximum data rate is 400kHz which supports fast-mode I<sup>2</sup>C. Timing is detailed in Figure 10. The data rate is limited by the slave acknowledge setup time ( $t_{SU;ACK}$ ), consisting of the I<sup>2</sup>C standard minimum setup time ( $t_{SU;DAT}$ ) of 100ns, maximum clock propagation delay of 225ns, glitch filter and isolated data delay of 500ns maximum, and the combined isolated and logic data fall time of 300ns at maximum bus loading. The total setup time reduces the  $l^2C$  data hold time  $(t_{HD;DAT})$  to a maximum of 175ns, guaranteeing sufficient data setup time  $(t_{SU;ACK}).$

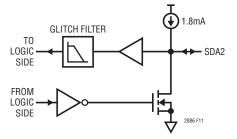

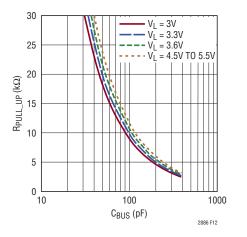

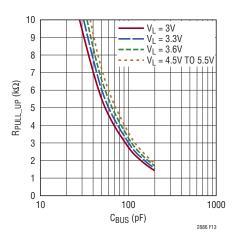

The isolated side bidirectional serial data pin, SDA2, simplified schematic is shown in Figure 11. An internal 1.8mA current source provides a pull-up for SDA2. Do not connect any other pull-up device to SDA2. This current source is sufficient to satisfy the system requirements for bus capacitances greater than 200pF in FAST mode and greater than 400pF in STANDARD mode.

| TIME                                                                                      | CPHA | EVENT DESCRIPTION                                                                                       |

|-------------------------------------------------------------------------------------------|------|---------------------------------------------------------------------------------------------------------|

| t <sub>0</sub>                                                                            | 0, 1 | Asynchronous chip select, may be synchronous to SDI but may not lag by more than 3ns                    |

| t <sub>0</sub> to t <sub>1</sub>                                                          | 0, 1 | Propagation delay chip select, logic to isolated side                                                   |

| t <sub>2</sub> 0                                                                          |      | Start of data transmission, data set-up                                                                 |

|                                                                                           | 1    | Start of transmission, data and clock set-up. Data transition must be within –13ns to 3ns of clock edge |

| t <sub>2</sub> to t <sub>3</sub> 0 Propagation delay of data, logic side to isolated side |      | Propagation delay of data, logic side to isolated side                                                  |

|                                                                                           | 1    | Propagation delay of data and clock, logic side to isolated side                                        |

| t <sub>3</sub>                                                                            | 0, 1 | Logic side data sample time, half clock period delay from data set-up transition                        |

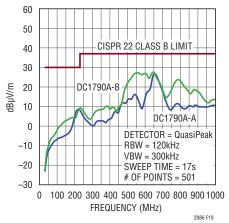

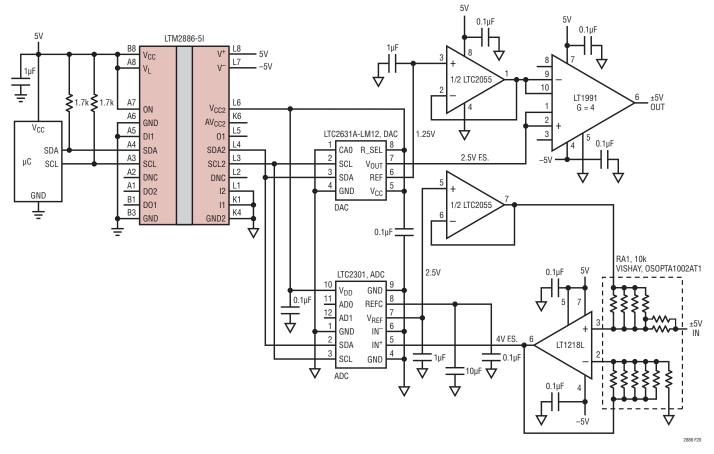

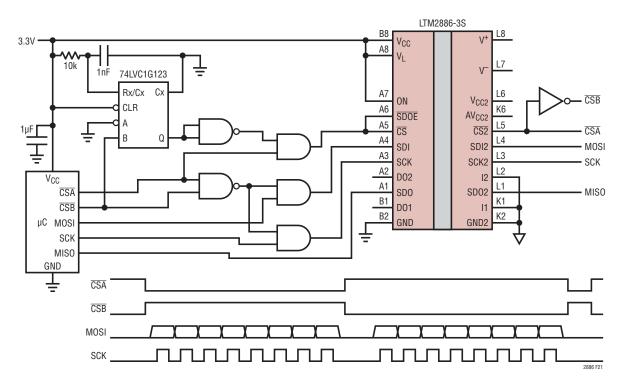

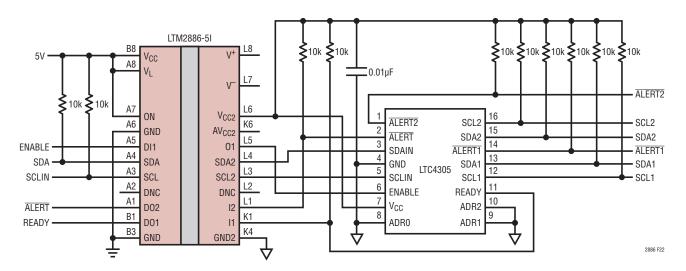

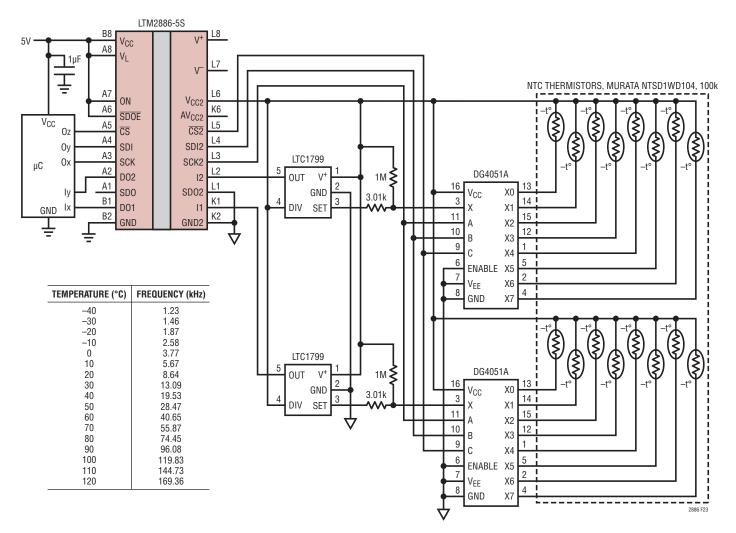

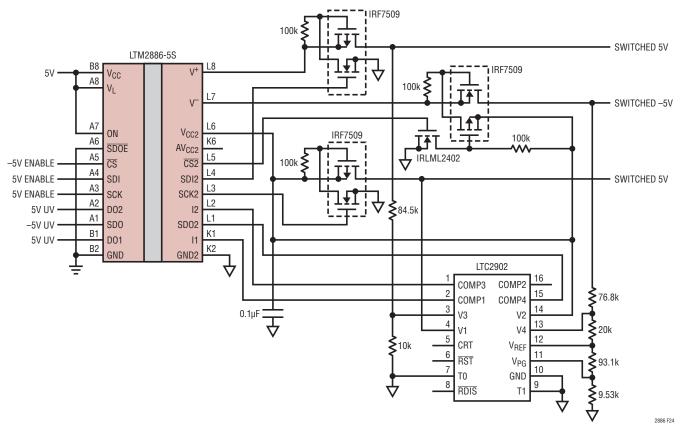

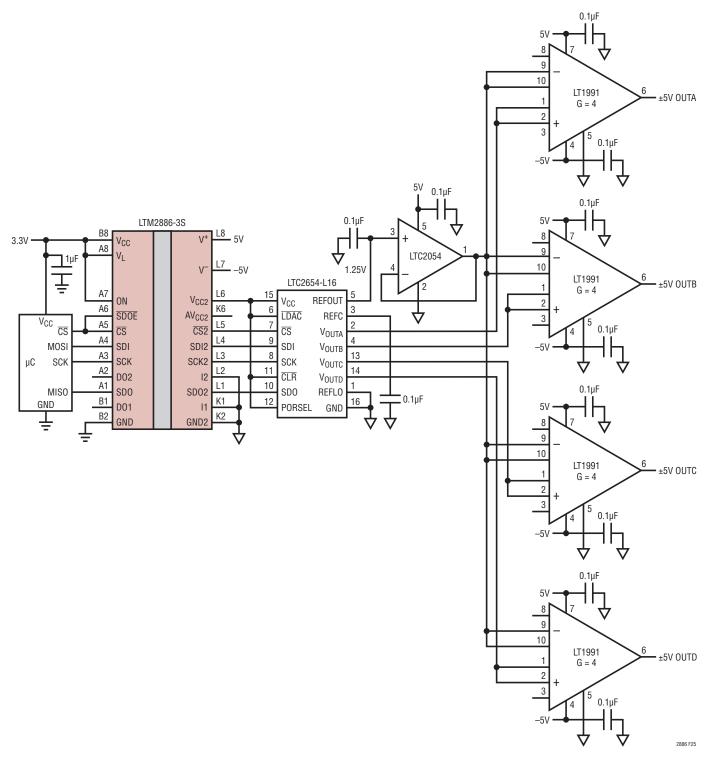

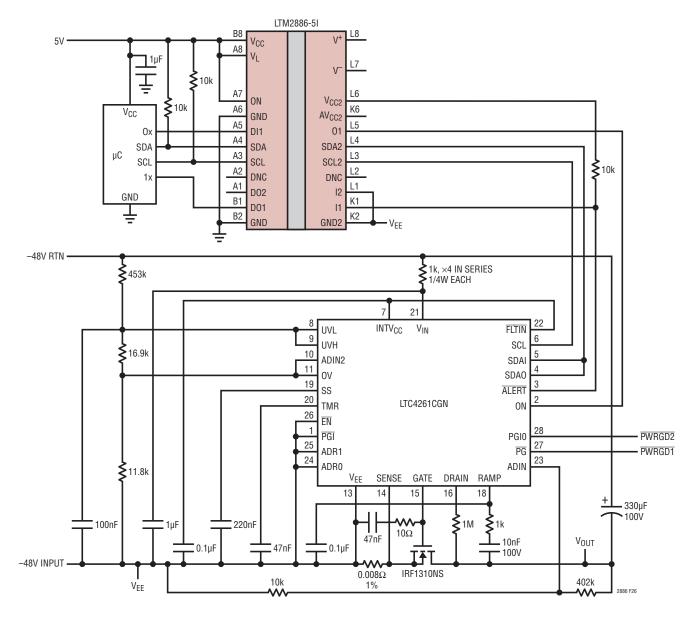

| t <sub>3</sub> to t <sub>5</sub>                                                          | 0, 1 | Clock propagation delay, clock and data transition                                                      |