**MAX77787**

### **General Description**

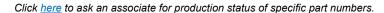

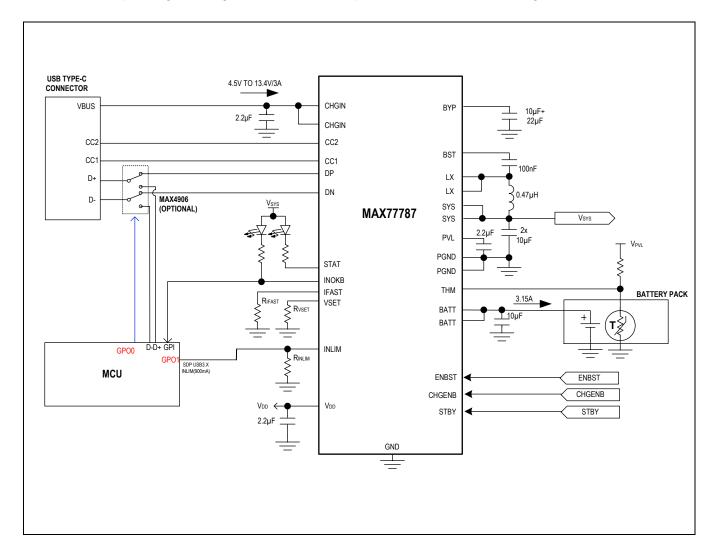

The MAX77787 is a standalone, 3.15A charger with integrated USB Type-C® CC detection and reverse-boost capability. The fast-charge current and termination voltage is easily configured with resistors. The IC operates with an input voltage of 4.5V to 13.4V and has a maximum input current limit of 3A. The IC also implements the adaptive input current limit (AICL) function that regulates the input voltage by reducing input current to prevent the voltage of a weak adapter from collapsing or folding back.

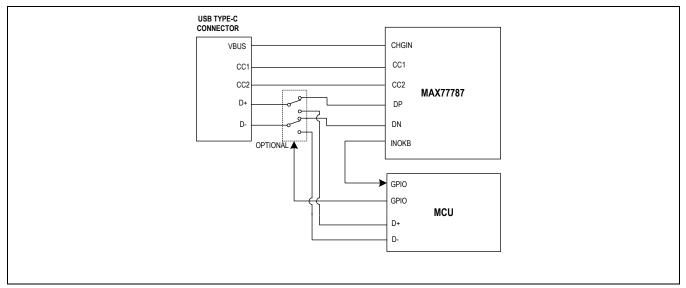

The USB Type-C Configuration Channel (CC) detection pins on the IC enable automatic USB Type-C power source detection and input current limit configuration without any software control as soon as the USB plug is inserted. The IC also integrates BC1.2 and proprietary adapter detection using the D+ and D- pins.

The IC offers reverse-boost capability up to 5.1V, 1.5A, that can be enabled with the ENBST pin, also BYP reverse-boost that can be enabled with the ENBST and STBY pin combination. The STAT pin indicates charging status, while the INOKB pin indicates valid input voltage. Charging can be stopped by pulling the CHGENB pin low.

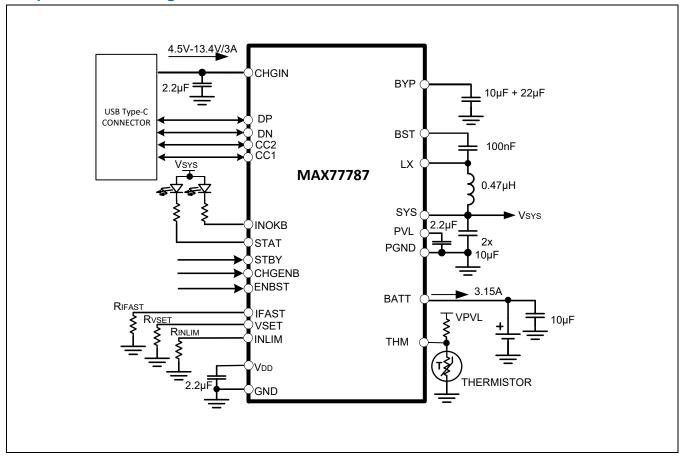

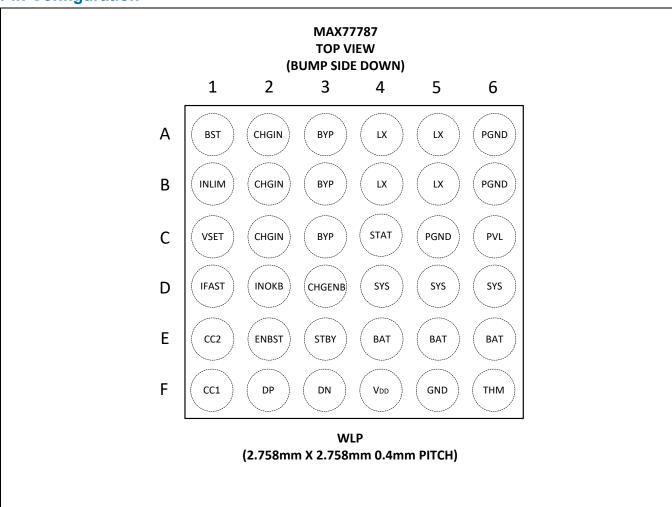

The IC is equipped with a Smart Power Selector™ and a battery true-disconnect FET to control the charging and discharging of the battery or isolate the battery in case of a fault. The IC supports Li-ion batteries with JEITA compliance. It also has another option that supports LiFePO₄ batteries with non-JEITA compliance. The IC comes in a 2.758mm x 2.758mm, 0.4mm pitch, 6 x 6 wafer-level package (WLP) making it suitable for low-cost PCB assembly.

### **Applications**

- Mobile Point-of-Sale (mPOS) Terminals

- Portable Medical Devices

- Wireless Headphones

- GPS Trackers

- Charging Cradles for Wearable Devices

- Power Banks

- Mobile Routers

### **Benefits and Features**

- Up to 16V Protection

- 13.4V Maximum Input Operating Voltage

- 3.15A Maximum Charging Current

- 6A Discharge Current Protection

- · No Firmware or Communication Required

- Integrated CC Detection for USB Type-C

- Integrated BC1.2 Detection for Legacy SDP, DCP, CDP, and DCD Timeout

- Integrated USB Detection for Common Proprietary Charger Types

- Automatic Input Current Limit Configuration

- Input Voltage Regulation with Adaptive Input Current Limit (AICL)

- 5.1V, 1.5A OTG Mode and BYP Reverse Boost

- Safety

- · Charge Safety Timer

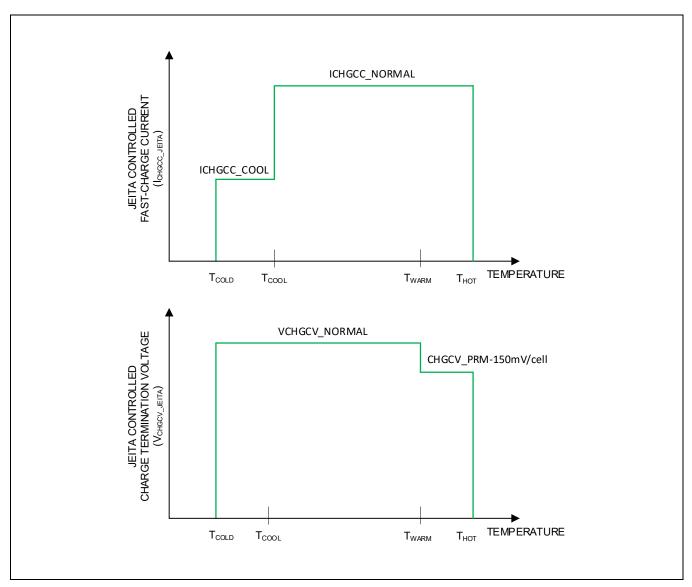

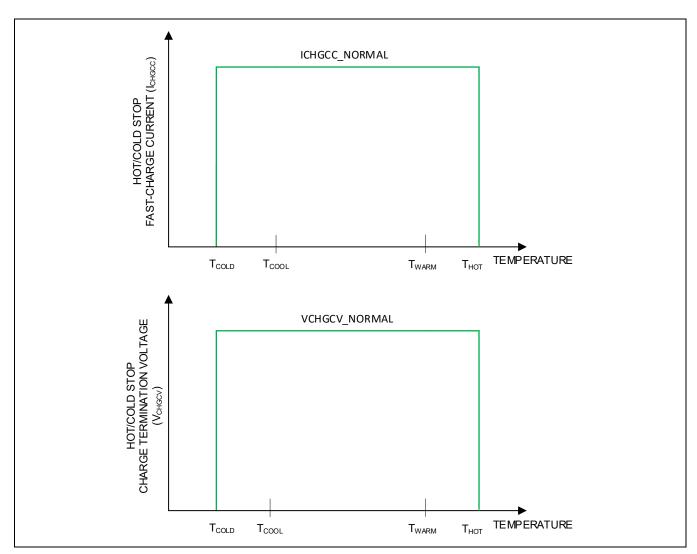

- JEITA Compliance with NTC Thermistor Monitor

- · Thermal Shutdown

- Pin Control of all Functions

- Resistor Configurable Fast-Charge Current/Input Current Limit/Termination Voltage

- · ENBST Pin to Enable and Disable Reverse Boost

- STAT Pin to Indicate Charging Status

- INOKB Pin to Indicate Input Power-OK

- · CHGENB Pin to Enable and Disable Charging

- STBY Pin to Support Suspend Mode

- · THM Pin to Monitor Thermistor

- Integrated Power Path

- Integrated Battery True-Disconnect FET

- 2.758mm x 2.758mm, 6 x 6 WLP

USB Type-C is a registered trademark of USB Implementers Forum. Smart Power Selector is a trademark of Maxim Integrated Products, Inc.

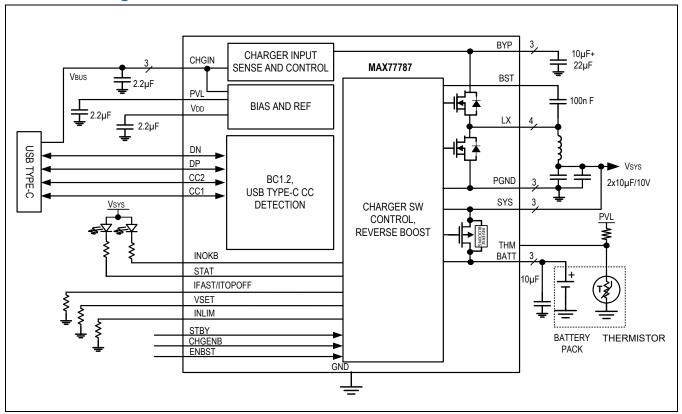

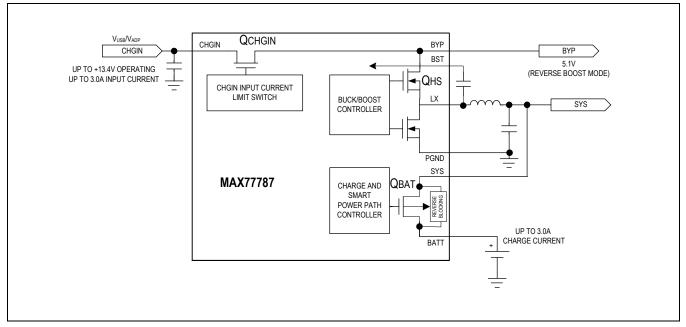

### **Simplified Block Diagram**

### **Absolute Maximum Ratings**

| CHGIN to GND0.3V to +16.0V                                      | THM, IFAST, VSET to GND0.3V to V <sub>DD</sub> + 0.3V |

|-----------------------------------------------------------------|-------------------------------------------------------|

| BYP, LX to PGND0.3V to +16.0V                                   | V <sub>DD</sub> , PVL, INLIM to GND0.2V to +2.2V      |

| BATT, SYS, INOKB, STAT, ENBST, CHGENB, STBY to GND0.3V to +6.0V | V <sub>CHGIN</sub> , BYP Continuous Current           |

| BST to PVL0.3V to +16.0V                                        | LX, PGND Continuous Current                           |

| BST to LX0.3V to +2.2V                                          | SYS, BATT Continuous Current 4.5A <sub>RMS</sub>      |

| DN, DP to GND0.3V to +6.0V                                      | Operating Temperature Range40°C to +85°C              |

| CC1, CC2 to GND0.3V to +6.0V                                    | Storage Temperature Range65°C to +150°C               |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Package Information**

| Package Code                                        | W362K2+1                       |  |

|-----------------------------------------------------|--------------------------------|--|

| Outline Number                                      | <u>21-100576</u>               |  |

| Land Pattern Number                                 | Refer to Application Note 1891 |  |

| Thermal Resistance, Four-Layer Board:               |                                |  |

| Junction-to-Ambient (θ <sub>JA</sub> )              | 45.72°C/W                      |  |

| Junction-to-Case Thermal Resistance $(\theta_{JC})$ | NA                             |  |

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

### **Electrical Characteristics**

$(V_{CHGIN} = 5.0V, Limits are 100\% tested at T_A = +25^{\circ}C.$  Limits over the operating temperature range and relevant supply voltage range

| are guaranteed by design a                            |                              |                                                                                                                          | MIN                          |                         |                              |        |

|-------------------------------------------------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------|------------------------------|-------------------------|------------------------------|--------|

| PARAMETER                                             | SYMBOL                       | SYMBOL CONDITIONS                                                                                                        |                              | TYP                     | MAX                          | UNITS  |

| GENERAL ELECTRICAL                                    | CHARACTERIS                  | TICS                                                                                                                     | •                            |                         |                              |        |

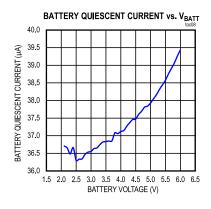

| Battery Only Quiescent<br>Current                     | I <sub>BATT_Q</sub>          | USBC as UFP and BATT = SYS = 3.6V                                                                                        |                              | 30                      | 50                           | μΑ     |

| SWITCHING MODE CHA                                    | RGER                         | <u></u>                                                                                                                  | T                            |                         |                              |        |

| CHGIN Voltage Range                                   | V <sub>CHGIN</sub>           | Operating voltage ( <u>Note 1</u> )                                                                                      | V <sub>CHGIN</sub> _<br>UVLO |                         | V <sub>CHGIN</sub> _<br>OVLO | V      |

| CHGIN Overvoltage<br>Threshold                        | V <sub>CHGIN_OVLO</sub>      | V <sub>CHGIN</sub> rising                                                                                                | 13.4                         | 13.7                    | 14                           | V      |

| CHGIN Overvoltage<br>Threshold Hysteresis             | V <sub>CHGINH</sub> OVL<br>O | V <sub>CHGIN</sub> falling                                                                                               |                              | 300                     |                              | mV     |

| CHGIN to GND<br>Minimum Turn-On<br>Threshold Accuracy | V <sub>CHGIN_UVLO</sub>      | V <sub>CHGIN</sub> rising                                                                                                | 4.6                          | 4.7                     | 4.8                          | ٧      |

| CHGIN to SYS<br>Minimum Turn-On<br>Threshold          | V <sub>CHGIN2SYS</sub>       | V <sub>CHGIN</sub> rising                                                                                                | V <sub>SYS</sub> + 0.12      | V <sub>SYS</sub> + 0.20 | V <sub>SYS</sub> + 0.28      | V      |

| CHGIN Adaptive Voltage Regulation Threshold Accuracy  | V <sub>CHGIN_REG</sub>       |                                                                                                                          | 4.4                          | 4.5                     | 4.6                          | V      |

| CHGIN Current Limit                                   | CHGIN_ILIM                   | Automatically configured after charger type detection                                                                    | 0.5                          |                         | 3.0                          | А      |

| Range                                                 | CHGIN_ILIW                   | Externally configured by R <sub>INLIM</sub> when charger type detected as unknown                                        | 0.5                          | 0.5                     |                              | X.     |

| CHGIN Minimum Current Threshold                       | l <sub>ULO</sub>             |                                                                                                                          |                              | 65                      |                              | mA     |

| CHGIN Supply Current                                  | I <sub>IN</sub>              | V <sub>CHGIN</sub> = 5.0V, charger enabled, V <sub>SYS</sub> = V <sub>BATT</sub> = 4.5V, (No switching, battery charged) |                              | 2.7                     | 4                            | mA     |

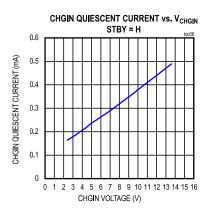

| Cricin Cuppiy Curion                                  | I <sub>IN</sub> STBY         | DCDC off, STBY = H, V <sub>CHGIN</sub> = 5V                                                                              |                              | 0.2                     |                              | 1117 ( |

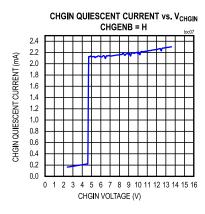

|                                                       | I <sub>IN_CHGENB</sub>       | CHGENB = H, V <sub>CHGIN</sub> = 5V                                                                                      |                              | 2.7                     |                              |        |

|                                                       |                              | Charger enabled, 500mA input current setting, T <sub>A</sub> = 0°C to +85°C                                              | 423                          | 460                     | 500                          |        |

| V <sub>CHGIN</sub> Input Current<br>Limit             | I <sub>INLIMIT</sub>         | Charger enabled, 1500mA input current setting, T <sub>A</sub> = 0°C to +85°C                                             | 1300                         | 1400                    | 1500                         | mA     |

|                                                       |                              | Charger enabled, 3000mA input current setting, T <sub>A</sub> = 0°C to +85°C                                             | 2600                         | 2800                    | 3000                         |        |

| CHGIN Self-Discharge<br>Down to UVLO Time             | t <sub>INSD</sub>            | Time required for the charger input to cause CHGIN capacitor to decay from 6.0V to 4.3V                                  |                              | 100                     |                              | ms     |

| CHGIN Input Self-<br>Discharge Resistance             | R <sub>INSD</sub>            |                                                                                                                          |                              | 44                      |                              | kΩ     |

| CHGIN to BYP<br>Resistance                            | R <sub>CHGIN2BYP</sub>       | Bidirectional                                                                                                            |                              | 20                      |                              | mΩ     |

| LX High Side<br>Resistance                            | R <sub>HS</sub>              |                                                                                                                          |                              | 41                      |                              | mΩ     |

| LX Low Side Resistance                                | R <sub>LS</sub>              |                                                                                                                          |                              | 41                      |                              | mΩ     |

| BATT to SYS Dropout<br>Resistance                     | R <sub>BAT2SYS</sub>         |                                                                                                                          |                              | 13                      |                              | mΩ     |

$(V_{CHGIN} = 5.0V, Limits are 100\% tested at T_A = +25^{\circ}C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.)$

| are guaranteed by design PARAMETER       | SYMBOL                  | CONDITIONS                                                                                                   | MIN  | TYP  | MAX  | UNITS |

|------------------------------------------|-------------------------|--------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| CHGIN to BATT                            |                         | Calculation estimates a $0.04\Omega$ inductor resistance (R <sub>L</sub> )                                   | MIIV |      | MAX  | ONITO |

| Dropout Resistance                       | R <sub>C</sub> HGIN2BAT | R <sub>CHGIN2BAT</sub> = R <sub>CHGIN2BYP</sub> + R <sub>HS</sub> + R <sub>L</sub><br>+ R <sub>BAT2SYS</sub> |      | 114  |      | mΩ    |

|                                          |                         | LX = PGND or BYP, T <sub>A</sub> = +25°C                                                                     |      | 0.01 | 10   |       |

| LX Leakage Current                       |                         | LX = PGND or BYP, T <sub>A</sub> = +85°C                                                                     |      | 1    |      | μA    |

|                                          |                         | BST = PGND or 1.8V, T <sub>A</sub> = +25°C                                                                   |      | 0.01 | 10   |       |

| BST Leakage Current                      |                         | BST = PGND or 1.8V, T <sub>A</sub> = +85°C                                                                   |      | 1    |      | μA    |

| DVD I also Oscarla                       |                         | V <sub>BYP</sub> = 5V, V <sub>CHGIN</sub> = 0V, LX = 0V,<br>charger Disabled, T <sub>A</sub> = +25°C         |      | 0.01 | 10   |       |

| BYP Leakage Current                      |                         | $V_{BYP}$ = 5V, $V_{CHGIN}$ = 0V, LX = 0V, charger disabled, $T_A$ = +85°C                                   |      | 1    |      | μА    |

| SYS Leakage Current                      |                         | $V_{SYS} = 0V$ , $V_{BATT} = 4.2V$ , charger disabled, $T_A = +25^{\circ}C$                                  |      | 0.01 | 10   | μА    |

| OTO Leakage Current                      |                         | $V_{SYS} = 0V$ , $V_{BATT} = 4.2V$ , charger disabled, $T_A = +85^{\circ}C$                                  |      | 1    |      | μΛ    |

| Minimum ON Time                          | t <sub>ON-MIN</sub>     |                                                                                                              |      | 75   |      | ns    |

| Minimum OFF Time                         | toff-min                |                                                                                                              |      | 75   |      | ns    |

| Buck Current Limit                       | I <sub>LIM</sub>        |                                                                                                              | 5.16 | 6.0  | 6.84 | Α     |

| Reverse Boost<br>Quiescent Current       |                         | Non-switching: output forced 200mV above its target regulation voltage                                       |      | 2000 |      | μΑ    |

| Reverse Boost BYP<br>Voltage in OTG Mode | V <sub>BYP.OTG</sub>    |                                                                                                              | 4.94 | 5.1  | 5.26 | V     |

| CHGIN Output Current<br>Limit            | ICHGIN.OTG.LI<br>M      | 3.4V < V <sub>BATT</sub> < 4.5V, T <sub>A</sub> = 0°C to +85°C                                               | 1500 |      | 1725 | mA    |

| Reverse Boost Output<br>Voltage Ripple   |                         | Discontinuous inductor current (i.e., skip mode)                                                             |      | ±150 |      | . mV  |

|                                          |                         | Continuous inductor current                                                                                  |      | ±150 |      |       |

| BATT Regulation<br>Voltage Accuracy      |                         | T <sub>A</sub> = +25°C, BATT regulation voltage (See <u>Table 5</u> )                                        | -0.9 | -0.3 | +0.3 | %     |

| BATT Regulation<br>Voltage               | V <sub>BATREG</sub>     | Externally programmable by R <sub>VSET</sub>                                                                 | 3.6  |      | 4.55 | V     |

| BATT Regulation Voltage Accuracy         |                         | T <sub>A</sub> = 0°C to +85°C, BATT regulation voltage (See <u>Table 5</u> )                                 | -1   | -0.3 | +0.5 | %     |

| Fast-Charge Current<br>Program Range     |                         | External resistor programmable                                                                               | 0.5  |      | 3.15 | Α     |

|                                          |                         | T <sub>A</sub> = 0°C to +85°C, V <sub>BATT</sub> > V <sub>SYSMIN</sub> , programmed for 3.0A                 | 2850 | 3000 | 3150 |       |

| Fast-Charge Currents                     | I <sub>FC</sub>         | T <sub>A</sub> = 0°C to +85°C, V <sub>BATT</sub> > V <sub>SYSMIN</sub> , programmed for 2.0A                 | 1900 | 2000 | 2100 | mA    |

|                                          |                         | T <sub>A</sub> = 0°C to +85°C, V <sub>BATT</sub> > V <sub>SYSMIN</sub> , programmed for 0.5A                 | 465  | 500  | 535  |       |

| Trickle Charge<br>Threshold              | V <sub>TRICKLE</sub>    | V <sub>BATT</sub> rising                                                                                     | 3.0  | 3.1  | 3.2  | V     |

| Precharge Threshold                      | V <sub>PRECHG</sub>     | V <sub>BATT</sub> rising                                                                                     | 2.4  | 2.5  | 2.6  | V     |

| Prequalification Threshold Hysteresis    | V <sub>PQ-H</sub>       | Applies to both V <sub>TRICKLE</sub> and V <sub>PRECHG</sub>                                                 |      | 100  |      | mV    |

$(V_{CHGIN} = 5.0V, Limits are 100\% tested at T_A = +25^{\circ}C. Limits over the operating temperature range and relevant supply voltage range$

| are guaranteed by design a                                                    |                      |                                                                                                                   |                   |                                                           |      | Т     |

|-------------------------------------------------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------|-------------------|-----------------------------------------------------------|------|-------|

| PARAMETER                                                                     | SYMBOL               | CONDITIONS                                                                                                        | MIN               | TYP                                                       | MAX  | UNITS |

| Trickle Charge Current                                                        | I <sub>TRICKLE</sub> | I <sub>TRICKLE</sub> for termination voltage from 4.1V to 4.5V option; trickle charge is disabled for 3.6V option |                   |                                                           | 330  | mA    |

| Precharge Charge<br>Current                                                   | I <sub>PRECHG</sub>  |                                                                                                                   | 40                | 55                                                        | 80   | mA    |

| Charger Restart<br>Threshold                                                  | V <sub>RSTRT</sub>   |                                                                                                                   | 50                | 100                                                       | 150  | mV    |

| Charger Restart<br>Deglitch Time                                              |                      | 10mV overdrive, 100ns rise time                                                                                   |                   | 130                                                       |      | ms    |

| Top-Off Current<br>Program Range                                              | I <sub>TO</sub>      | See <u>Table 6</u>                                                                                                | 50                |                                                           | 150  | mA    |

| Top-Off Current                                                               | <b>I</b>             | T <sub>A</sub> = 0°C to +85°C, programmed for 150mA                                                               | 130               | 150                                                       | 170  | A     |

| Accuracy                                                                      | I <sub>TO</sub>      | T <sub>A</sub> = 0°C to +85°C, programmed for 50mA                                                                | 25                | 50                                                        | 75   | mA    |

| Charge Termination Deglitch Time                                              | t <sub>TERM</sub>    | 2mV overdrive, 100ns rise/fall time                                                                               |                   | 30                                                        |      | ms    |

| Charger Soft-Start Time                                                       | t <sub>SS</sub>      |                                                                                                                   |                   | 1.5                                                       |      | ms    |

| BATT to SYS Reverse                                                           |                      | I <sub>BATT</sub> = 10mA                                                                                          |                   | 70                                                        |      | mV    |

| Regulation Voltage                                                            | V <sub>BSREG</sub>   | Load regulation during the reverse regulation mode                                                                |                   | 1                                                         |      | mV/A  |

|                                                                               | $V_{SYSMIN}$         | For termination voltage from 4.1V to 4.5V                                                                         | 3.5               |                                                           |      | - v   |

| Minimum SYS Voltage                                                           | * 2 t 2 ivilin       | For 3.6V termination voltage                                                                                      | 3.0               |                                                           |      | V     |

| Minimum SYS Voltage<br>Accuracy                                               | V <sub>SYSMIN</sub>  | -3 +3                                                                                                             |                   | +3                                                        | %    |       |

| Prequalification Time                                                         | t <sub>PQ</sub>      | Applies to both low-battery precharge and trickle modes                                                           |                   | 30                                                        |      | min   |

| Fast-Charge Constant<br>Current Plus Fast-<br>Charge Constant<br>Voltage Time | t <sub>FC</sub>      |                                                                                                                   |                   | 6                                                         |      | hours |

| Top-Off Time                                                                  | t <sub>TO</sub>      |                                                                                                                   |                   | 30                                                        |      | s     |

| Timer Accuracy                                                                |                      |                                                                                                                   | -20               |                                                           | +20  | %     |

| Thermal Shutdown                                                              | T <sub>SHDN</sub>    | T <sub>J</sub> rising ( <u>Note 2</u> )                                                                           |                   | 165                                                       |      | °C    |

| Thermal Shutdown<br>Hysteresis                                                |                      | T <sub>J</sub> failing                                                                                            |                   | 15                                                        |      | °C    |

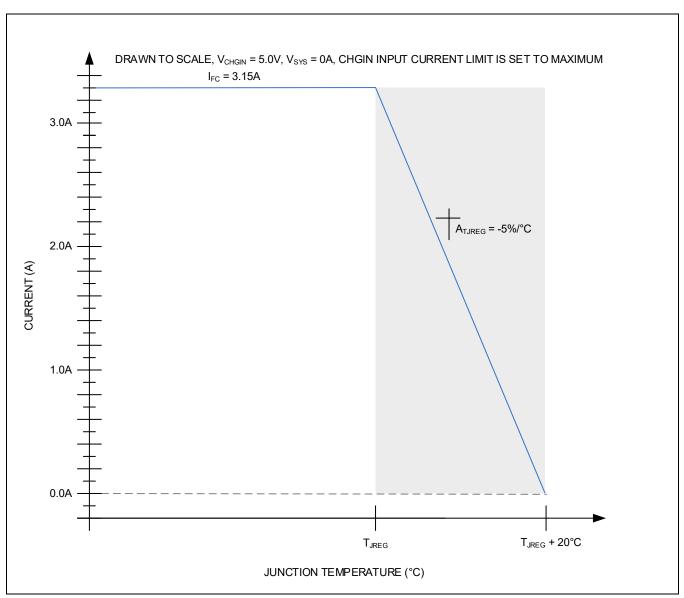

| Junction Temperature<br>Thermal Regulation<br>Loop Setpoint Program<br>Range  | T <sub>REG</sub>     | Junction temperature when charge current is reduced                                                               |                   |                                                           | °C   |       |

| Thermal Regulation<br>Gain                                                    | $AT_{JREG}$          | I <sub>FC</sub> = 3.15A -157.5                                                                                    |                   | mA/°C                                                     |      |       |

| THM Threshold, COLD                                                           | THM_COLD             | V <sub>THM</sub> /V <sub>PVL</sub> rising, 1% hysteresis<br>(thermistor temperature falling)                      | 72.5              | 74                                                        | 75.5 | %     |

| THM Threshold, COOL                                                           | THM_COOL             | V <sub>THM</sub> /V <sub>PVL</sub> rising, 1% hysteresis (thermistor temperature falling)                         | 63.5              | 65                                                        | 66.5 | %     |

| THM Threshold, WARM                                                           | THM_WARM             | V <sub>THM</sub> /V <sub>PVL</sub> falling, 1% hysteresis<br>(thermistor temperature rising)                      | ng, 1% hysteresis |                                                           | %    |       |

| THM Threshold, HOT                                                            | THM_HOT              | V <sub>THM</sub> /V <sub>PVL</sub> falling, 1% hysteresis<br>(thermistor temperature rising)                      | 21.5              | V <sub>THM</sub> /V <sub>PVL</sub> falling, 1% hysteresis |      |       |

(V<sub>CHGIN</sub> = 5.0V, Limits are 100% tested at T<sub>A</sub> = +25°C. Limits over the operating temperature range and relevant supply voltage range

are guaranteed by design and characterization.)

| PARAMETER                                              | SYMBOL                 | CONDITIONS                                                                                              | MIN | TYP                           | MAX | UNITS |

|--------------------------------------------------------|------------------------|---------------------------------------------------------------------------------------------------------|-----|-------------------------------|-----|-------|

| Charger Disable<br>Threshold                           | V <sub>CHGR_EN</sub>   | V <sub>THM</sub> /V <sub>PVL</sub> falling, 1% hysteresis<br>(charger is disabled below this threshold) | 4.5 | 6                             | 7.5 | %     |

| THM Input Leakage                                      |                        | V <sub>THM</sub> = GND or V <sub>PVL</sub> ; T <sub>A</sub> = +25°C                                     |     | 0.1                           | 1   |       |

| Current                                                |                        | V <sub>THM</sub> = GND or V <sub>PVL</sub> ; T <sub>A</sub> = +85°C                                     |     | 0.1                           |     | μA    |

| Battery Overcurrent<br>Threshold                       | I <sub>BOVCR</sub>     |                                                                                                         |     | 6.0                           |     | Α     |

| Battery Overcurrent                                    | t <sub>BOVRC</sub>     |                                                                                                         | 6   |                               |     | ms    |

| Debounce Time Battery Overcurrent                      | t <sub>OCP_RETRY</sub> |                                                                                                         |     | 0.15                          |     | sec   |

| Retry                                                  | OOI _ILETIKI           |                                                                                                         |     | 0.10                          |     |       |

| Battery Overcurrent<br>Protection Quiescent<br>Current | I <sub>BOVRC</sub>     |                                                                                                         |     | 3+I <sub>BATT</sub><br>/18040 |     | μA    |

| System Power-Up<br>Current                             | I <sub>SYSPU</sub>     |                                                                                                         | 35  | 50                            | 80  | mA    |

| System Power-Up<br>Voltage                             | V <sub>SYSPU</sub>     | V <sub>SYS</sub> rising, 100mV hysteresis                                                               | 1.9 | 2.0                           | 2.1 | V     |

| INOKB, STAT                                            |                        |                                                                                                         |     |                               |     |       |

| Logic Input Leakage Current                            |                        |                                                                                                         |     | 0.1                           | 1   | μA    |

| Output Low Voltage<br>INOKB, STAT                      |                        | I <sub>source</sub> = 5mA, T <sub>A</sub> = +25°C                                                       |     |                               | 0.4 | V     |

| Output High Leakage                                    |                        | V <sub>SYS</sub> = 5.5V, T <sub>A</sub> = +25°C                                                         | -1  | 0                             | +1  |       |

| INOKB, STAT                                            |                        | V <sub>SYS</sub> = 5.5V, T <sub>A</sub> = +85°C                                                         | •   | 0.1                           |     | μA    |

| ENBST                                                  | 1                      |                                                                                                         |     |                               |     |       |

| Logic Input Low<br>Threshold                           | V <sub>IL</sub>        |                                                                                                         |     |                               | 0.4 | V     |

| Logic Input High<br>Threshold                          | V <sub>IH</sub>        |                                                                                                         | 1.4 |                               |     | V     |

| Logic Input Leakage<br>Current                         | I <sub>ENBST</sub>     | V = 5.5V (including current through pulldown resistor)                                                  |     | 24                            | 60  | μΑ    |

| Pulldown Resistor                                      | R <sub>ENBST</sub>     |                                                                                                         |     | 235                           |     | kΩ    |

| STBY                                                   |                        |                                                                                                         |     |                               |     | I     |

| Logic Input Low<br>Threshold                           | V <sub>IL</sub>        |                                                                                                         |     |                               | 0.4 | V     |

| Logic Input High<br>Threshold                          | V <sub>IH</sub>        |                                                                                                         | 1.4 |                               |     | V     |

| Logic Input Leakage<br>Current                         | I <sub>STBY</sub>      | V = 5.5V (including current through pulldown resistor)                                                  |     | 24                            | 60  | μA    |

| Pulldown Resistor                                      | R <sub>STBY</sub>      |                                                                                                         |     | 235                           |     | kΩ    |

| CHGENB                                                 |                        |                                                                                                         |     | <u> </u>                      |     |       |

| Logic Input Low Threshold                              | V <sub>IL</sub>        |                                                                                                         |     |                               | 0.4 | V     |

| Logic Input High                                       | V <sub>IH</sub>        |                                                                                                         | 1.4 |                               |     | V     |

| Threshold  Logic Input Leakage                         | I <sub>CHGENB</sub>    | V = 5.5V (including current through                                                                     |     | 24                            | 60  | μA    |

| Current Pulldown Resistor                              | R <sub>CHGENB</sub>    | pulldown resistor)                                                                                      |     |                               |     | -     |

| ruliuowii Resistor                                     | CHGENB                 |                                                                                                         |     | 235                           |     | kΩ    |

$(V_{CHGIN} = 5.0V, Limits are 100\% tested at T_A = +25^{\circ}C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.)$

| are guaranteed by design           | and characterizat                      | ion.)                                                                                          | Т     |       |      | Т     |

|------------------------------------|----------------------------------------|------------------------------------------------------------------------------------------------|-------|-------|------|-------|

| PARAMETER                          | SYMBOL                                 | CONDITIONS                                                                                     | MIN   | TYP   | MAX  | UNITS |

| BC1.2 State Timeout                | t <sub>TMO</sub>                       |                                                                                                | 180   | 200   | 220  | ms    |

| Data Contact Detect<br>Time-Out    | t <sub>DCDtmo</sub>                    |                                                                                                | 700   | 800   | 900  | ms    |

| Proprietary Charger<br>Debounce    | t <sub>PRDeb</sub>                     |                                                                                                | 5     | 7.5   | 10   | ms    |

| Primary to Secondary<br>Timer      | <sup>t</sup> PDSDWait                  |                                                                                                | 27    | 35    | 39   | ms    |

| Charger Detection<br>Debounce      | t <sub>CDDeb</sub>                     |                                                                                                | 45    | 50    | 55   | ms    |

| V <sub>BUS64</sub> Threshold       | V <sub>BUS64</sub>                     | DP and DN pins. Threshold in percent of V <sub>BUS</sub> voltage; 3V < V <sub>BUS</sub> < 5.5V | 57    | 64    | 71   | %     |

| V <sub>BUS64</sub> Hysteresis      | V <sub>BUS64</sub> _H                  |                                                                                                |       | 0.015 |      | V     |

| V <sub>BUS47</sub> Threshold       | V <sub>BUS47</sub>                     | DP and DN pins. Threshold in percent of V <sub>BUS</sub> voltage; 3V < V <sub>BUS</sub> < 5.5V | 43.3  | 47    | 51.7 | %     |

| V <sub>BUS47</sub> Hysteresis      |                                        |                                                                                                |       | 0.015 |      | V     |

| V <sub>BUS31</sub> Threshold       | V <sub>BUS31</sub>                     | DP and DN pins. Threshold in percent of V <sub>BUS</sub> voltage; 3V < V <sub>BUS</sub> < 5.5V | 26    | 31    | 36   | %     |

| V <sub>BUS31</sub> Hysteresis      |                                        |                                                                                                |       | 0.015 |      | V     |

| I <sub>WEAK</sub> Current          | I <sub>WEAK</sub>                      |                                                                                                | 0.01  | 0.1   | 0.5  | μΑ    |

| R <sub>DM DWN</sub> Resistor       | R <sub>DM DWN</sub>                    |                                                                                                | 14.25 | 20    | 24.8 | kΩ    |

| I <sub>DP SRC</sub> Current        | I <sub>DP_SRC</sub> /I <sub>DCD</sub>  | Accurate over 0V to 2.5V                                                                       | 7     | 10    | 13   | μA    |

| I <sub>DM_SINK</sub> Current       | I <sub>DM_SINK</sub> /I <sub>DAT</sub> | Accurate over 0.15V to 3.6V                                                                    | 45    | 80    | 125  | μA    |

| V <sub>LGC</sub> Threshold         | V <sub>LGC</sub>                       |                                                                                                | 1.62  | 1.7   | 1.9  | V     |

| V <sub>LGC</sub> Hysteresis        | V <sub>LGC_H</sub>                     |                                                                                                |       | 0.015 |      | V     |

| V <sub>DAT_REF</sub> Threshold     | V <sub>DAT_REF</sub>                   |                                                                                                | 0.25  | 0.32  | 0.4  | V     |

| V <sub>DAT_REF</sub> Hysteresis    | V <sub>DAT_REF_H</sub>                 |                                                                                                |       | 0.015 |      | V     |

| V <sub>DN_SRC</sub> Voltage        | V <sub>DN_SRC</sub> /V <sub>SR</sub>   | Accurate over I <sub>LOAD</sub> = 0 to 200μA                                                   | 0.5   | 0.6   | 0.7  | V     |

| V <sub>DP_SRC</sub> Voltage        | V <sub>DP_SRC</sub> /V <sub>SR</sub>   | Accurate over I <sub>LOAD</sub> = 0 to 200μA                                                   | 0.5   | 0.6   | 0.7  | V     |

| COMP2 Load Resistor                | R <sub>USB</sub>                       | Load resistor on DP/DN                                                                         | 3     | 6.1   | 12   | МΩ    |

| CC DETECTION                       | 1                                      |                                                                                                |       |       |      | L     |

| CC Pin Voltage in DFP<br>1.5A Mode | V <sub>CC_PIN</sub>                    | Measured at CC pins with 126kΩ load.<br>IDFP1.5_CC enable and V <sub>AVL</sub> ≥ 2.5V          | 1.85  |       |      | V     |

| CC Pin Clamp Voltage               | V <sub>CC_CIAMP</sub>                  | 60µA ≤ I <sub>CC</sub> ≤ 600µA                                                                 |       | 1.1   | 1.32 | V     |

| CC Pin Clamp Voltage (5.5V)        |                                        | I <sub>CC</sub> _<2mA                                                                          |       | 5.25  | 5.5  | V     |

| CC UFP Pulldown<br>Resistance      | R <sub>PD_UFP</sub>                    |                                                                                                | -10%  | 5.1k  | +10% | Ω     |

| CC DFP 1.5A Current<br>Source      | I <sub>DFP1.5</sub> _CC                |                                                                                                | -8%   | 180   | +8%  | μΑ    |

| CC RA RD Threshold                 | V <sub>RA RD0.5</sub>                  |                                                                                                | 0.15  | 0.2   | 0.25 | V     |

| CC UFP 0.5A RD<br>Threshold        | V <sub>UFP_RD0.5</sub>                 |                                                                                                | 0.61  | 0.66  | 0.7  | V     |

| CC UFP 0.5A RD<br>Hysteresis       | V <sub>UFP_RD0.5_</sub> H              |                                                                                                |       | 0.015 |      | V     |

$(V_{CHGIN} = 5.0V, Limits are 100\% tested at T_A = +25^{\circ}C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.)$

| PARAMETER                    | SYMBOL                    | CONDITIONS                                                                 | MIN  | TYP  | MAX  | UNITS |

|------------------------------|---------------------------|----------------------------------------------------------------------------|------|------|------|-------|

| CC UFP 1.5A RD<br>Threshold  | V <sub>UFP_RD1.5</sub>    |                                                                            | 1.16 | 1.23 | 1.31 | ٧     |

| CC UFP 1.5A RD<br>Hysteresis | V <sub>UFP_RD1.5_</sub> H |                                                                            |      | 0.15 |      | ٧     |

| CC Pin Power-Up Time         | t <sub>ClampSwap</sub>    | Max time allowed from removal of voltage clamp till 5.1k resistor attached |      |      | 15   | ms    |

| CC Detection Debounce        | t <sub>CCDeb</sub>        |                                                                            | 100  | 119  | 200  | ms    |

| USB Type-C Debounce          | t <sub>PDDeb</sub>        |                                                                            | 10   | 15   | 20   | ms    |

| USB Type-C Quick<br>Debounce | t <sub>QDeb</sub>         |                                                                            | 0.9  | 1    | 1.1  | ms    |

Note 1: The CHGIN input must be less than  $V_{CHGIN\_OVLO}$  and greater than both  $V_{CHGIN\_UVLO}$  and  $V_{CHGIN2SYS}$  for the charger to turn on.

Note 2: T<sub>SHDN</sub> only sets charger from charging to buck mode, T<sub>SHDN</sub> is invalid in reverse-boost mode

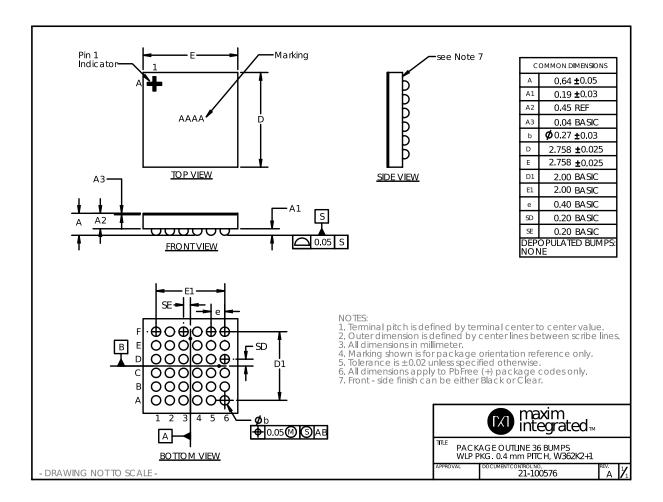

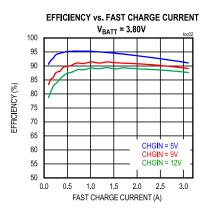

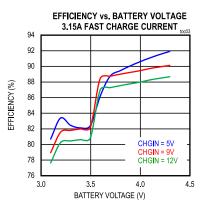

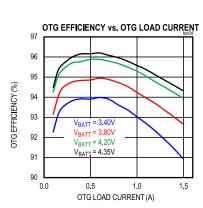

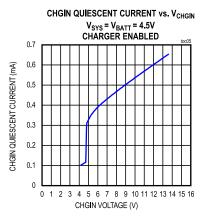

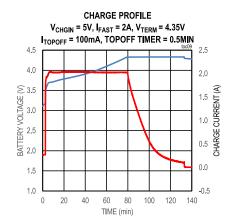

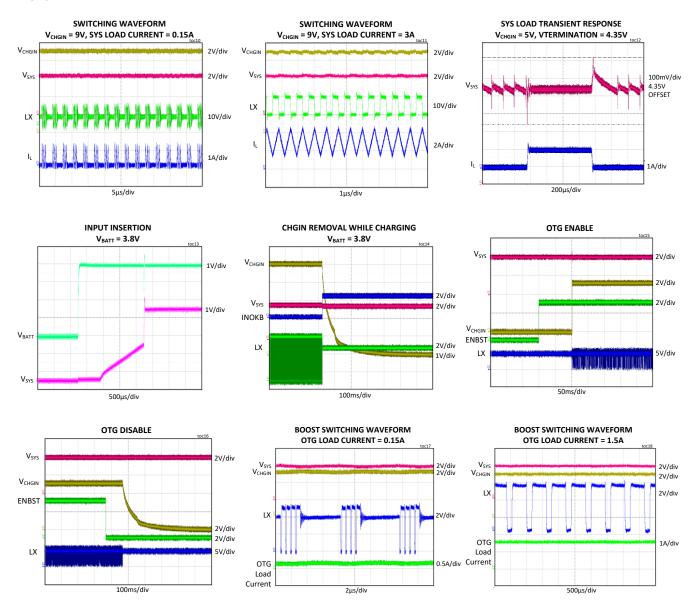

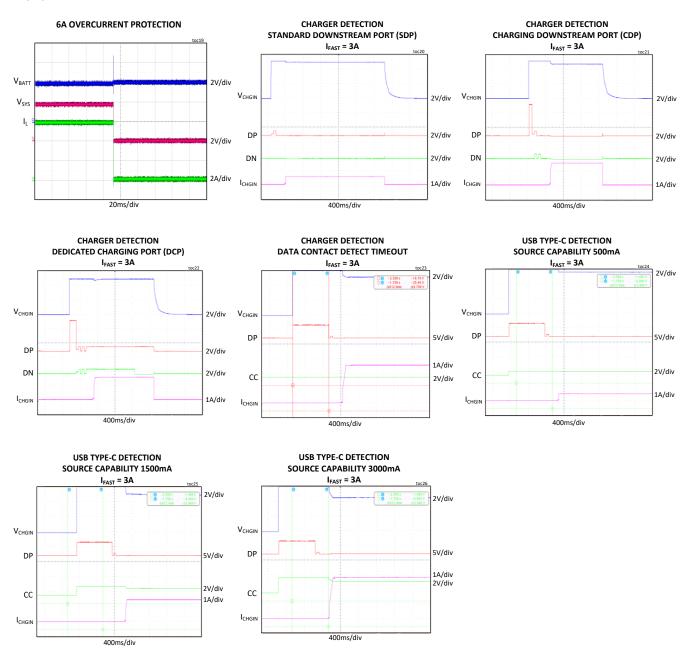

### **Typical Operating Characteristics**

$(V_{CHGIN} = 5V, V_{BATT} = 3.8V, T_A = +25^{\circ}C, unless otherwise noted.)$

( $V_{CHGIN}$  = 5V,  $V_{BATT}$  = 3.8V,  $T_A$  = +25°C, unless otherwise noted.)

( $V_{CHGIN}$  = 5V,  $V_{BATT}$  = 3.8V,  $T_A$  = +25°C, unless otherwise noted.)

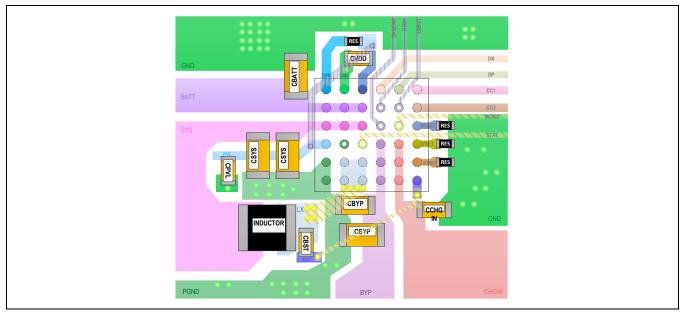

### **Pin Configuration**

### **Pin Descriptions**

| PIN | NAME  | FUNCTION                                                                                                                                                                                                                             |

|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1  | BST   | Provides Drive to High-Side Internal nMOS. Connect a 100nF/6.3V bootstrap capacitor between this pin and the LX node.                                                                                                                |

| D2  | INOKB | Charger Input Valid, Active-Low Logic Output Flag. The open-drain output indicates when a valid voltage is present at CHGIN.                                                                                                         |

| C4  | STAT  | Open-Drain Charge Status Indication Output. STAT is toggling low and high impedance during charge. STAT becomes low when a top-off threshold is detected and in a done state. STAT becomes high impedance when charge faults happen. |

| E1  | CC2   | USB Type-C CC2 Connection                                                                                                                                                                                                            |

| F1  | CC1   | USB Type-C CC1 Connection                                                                                                                                                                                                            |

| F2  | DP    | Positive Line of the USB Data Line Pair. Connect to D+ on USB Type-C or micro USB connector.                                                                                                                                         |

| F3  | DN    | Negative Line of the USB Data Line Pair. Connect to D- on USB Type-C or micro USB connector.                                                                                                                                         |

| E2  | ENBST | Active-High Logic Input. Enable/disable the reverse-boost converter.                                                                                                                                                                 |

| F5  | GND   | Analog Ground. Short to ground plane.                                                                                                                                                                                                |

| F4              | $V_{DD}$ | Output of On-Chip LDO Used to Power On-Chip, Low-Noise Circuits. Bypass with a $2.2\mu F/10V$ ceramic capacitor to GND. Powering external loads from $V_{DD}$ is not recommended other than pullup resistors.                                                                                                                                        |

|-----------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F6              | THM      | Thermistor Connection. Connect an external negative temperature coefficient (NTC) thermistor from THM to GND. Connect a resistor equal to the thermistor +25°C resistance from THM to PVL. See the <u>JEITA Compliance</u> for details.                                                                                                              |

| D1              | IFAST    | Fast-Charge Current Setting Pin. Connect a resistor ( $R_{IFAST}$ ) from IFAST to GND to program the fast-charge current. Use 24.9k $\Omega$ for 3.15A fast-charge current.                                                                                                                                                                          |

| E4,E5,E6        | BATT     | Battery Power Connection. Connect to the positive terminal of a single-cell (or parallel cell) Li-ion battery. Bypass BATT to PGND ground plane with a 10µF ceramic capacitor.                                                                                                                                                                       |

| D4,D5,D6        | SYS      | System Power Node. Bypass SYS to PGND with a 2x10µF/10V ceramic capacitor.                                                                                                                                                                                                                                                                           |

| C6              | PVL      | Output of On-Chip LDO, Noisy Rail due to Bootstrap Operation. Bypass with a 2.2µF/10V ceramic capacitor to PGND. Powering external loads from PVL is not recommended.                                                                                                                                                                                |

| A6,B6,C5        | PGND     | Power Ground. Connect the return of the buck output capacitor close to these pins.                                                                                                                                                                                                                                                                   |

| A4,A5,B4,<br>B5 | LX       | Switching Node. Connect an inductor between LX and SYS. When the buck converter is enabled, LX switches between BYP and PGND to control the input current, battery current, battery voltage, and die temperature.                                                                                                                                    |

| A3,B3,C3        | BYP      | System Power Connection. Output of OVP adapter input block and input to switching charger. Bypass with a 22µF/16V ceramic capacitor from BYP to PGND.                                                                                                                                                                                                |

| A2,B2,C2        | CHGIN    | Charger Input. Up to 13.4V operating, 16VDC withstand input pin connected to an adapter or USB power source. Connect a 2.2µF/16V ceramic capacitor from CHGIN to GND.                                                                                                                                                                                |

| C1              | VSET     | Charge Termination Voltage Setting Input. Connecting a resistor (R <sub>VSET</sub> ) from VSET to GND programs the charge termination voltage.                                                                                                                                                                                                       |

| D3              | CHGENB   | Active-Low Input. Battery charging is enabled when CHGENB connects to low.                                                                                                                                                                                                                                                                           |

| E3              | STBY     | Active-High Input. Connect high to disable the DCDC between CHGIN input and SYS output. CHGIN supply current reduces to I <sub>CHGIN_STBY</sub> . The battery supplies the system power. Connect low to control the DCDC with the power path-state machine                                                                                           |

| B1              | INLIM    | Charger Input Current Limit Setting Input. Connecting a resistor (R <sub>INLIM</sub> ) from INLIM to GND programs the charger input current limit. The input current limit setting through a resistor is valid only when the adaptor is detected as unknown. Else, the input current limit is programmed by D+/D- detection and CC detection result. |

### **Functional Diagram**

### **Detailed Description**

The MAX77787 is a highly integrated USB Type-C charger with autonomous configuration. The IC can operate input range from 4.5V to 13.4V to support 5V, 9V, and 12V AC adapter and USB input. The fast-charge current is up to 3.15A and the max input current limit is 3.0A.

The IC can run BC1.2 and USB Type-C CC detection upon input insertion and configure input source to max power option and charger input current limit to max power.

Fast-charge current and top-off current threshold can be programmed with an external resistor. Input voltage regulation feature (AICL) even allows users to use weak AC adapters without preventing charge.

Power path design provides system power even when the battery is fully discharged and it supplements current from the battery and charge input automatically when the system demands higher current.

Reverse boost from the battery can be enabled by the ENBST and STBY pins to allow 5.1V/1.5A OTG to V<sub>BUS</sub> or BYP.

### **Switching Mode Charger**

#### **Features**

- Complete Li+/LiPoly/LiFePO<sub>4</sub> Battery Charger

- · Prequalification, Constant Current, Constant Voltage

- 55mA Pre-charge Current

- 300mA Trickle Charge Current for MAX77787J Version. For the MAX77787H version, the trickle charge current is disabled.

- · Resistor Adjustable Constant Current Charge

- 500mA to 3.15A (See *Table 6*)

- · Resistor Adjustable Battery Regulation Voltage

- 3.6V to 4.55V (See <u>Table 5</u>)

- -0.9/+0.3% Accuracy at +25°C

- -1/+0.5% Accuracy from 0°C to +85°C

- Synchronous Switch-Mode Based Design

- Smart Power Selector

- · Optimally Distributes Power Between the Charge Adapter, System, and Main Battery

- · When Powered by a Charge Adapter, the Main Battery can Provide Supplemental Current to the System

- The Charge Adapter can Support the System without the Main Battery

- No External MOSFETs Required

- Single Input Operation

- Reverse Leakage Protection Prevents the Battery Leaking Current to the Inputs

- V<sub>CHGIN OVLO</sub> = 13.4V

- · Supports AC-to-DC Wall Adapters

- · Automatic Input Current Limit Selection after Charger Type Detection

- 500mA, 1A, 2A, 2.5A, 3A

- · External Programmable Input Current Limit when Unknown Charger Type is detected

- 500mA to 3A (See *Table 4*)

- Charge Safety Timer

- 6 Hour

- Die Temperature Monitor with Thermal Foldback Loop

- Die Temperature Thresholds (°C): 130°C

- Input Voltage Regulation allows Operation from High-Impedance Sources (AICL)

- BATT to SYS Switch is 13mΩ Typical

- Capable of 4.5A Steady-State Operation from BATT to SYS

- Short Circuit Protection

- · BATT to SYS Overcurrent Threshold: 6A

- SYS Short-to-Ground

- Buck Operates with Input Current Limit to 200mA when V<sub>SYS</sub> < V<sub>SYSPU</sub>

Figure 1. Simplified Functional Diagram

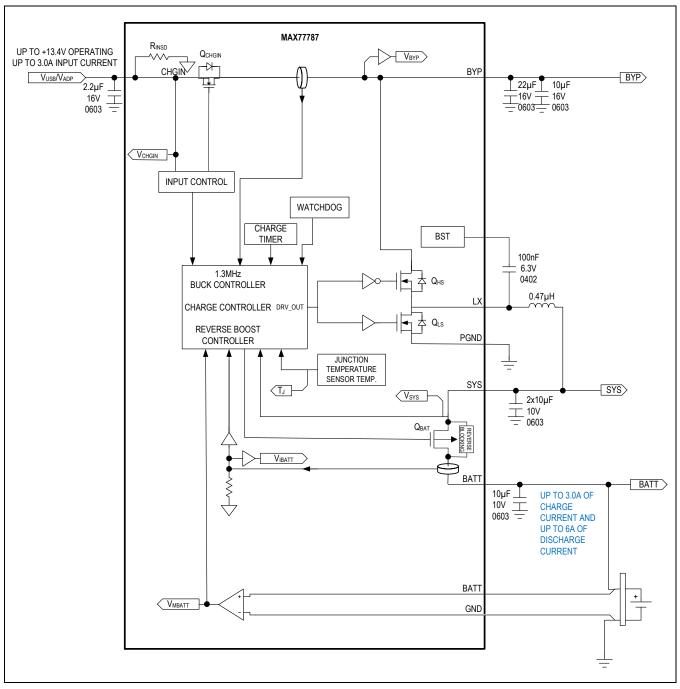

Figure 2. Main Battery Charger Detailed Functional Diagram

### **Detailed Description**

The IC is a switch-mode charger for a one-cell lithium-ion (Li+), lithium polymer (Li-polymer) battery, or LiFePO<sub>4</sub> battery. As shown in <u>Figure 2</u>, the current limit for CHGIN input is automatically configured allowing the flexibility for connection to either an AC-to-DC wall charger or a USB port.

The synchronous switch-mode DC-DC converter utilizes a high 1.3MHz switching frequency which is ideal for portable devices because it allows the use of small components while eliminating excessive heat generation. The DC-DC has both a buck and a boost mode of operation. When charging the main battery the converter operates as a buck. The DC-DC buck operates from a 4.5V to 13.4V source and delivers up to 3.15A to the battery. The battery charge current is programmable from 500mA to 3.15A with an external resistor.

As a boost converter, the DC-DC uses energy from the main battery to boost the voltage at BYP. The boosted BYP voltage is useful to supply the USB OTG voltage which is fixed to 5.1V.

Maxim's Smart Power Selector architecture makes the best use of the limited adapter power and the battery's power at all times to supply up to Buck Current Limit from the buck to the system. (Additionally, supplement mode provides additional current from the battery to the system up to B2SOVRC.) Adapter power that is not used for the system goes to charging the battery. All power switches for charging and switching the system load between the battery and adapter power are included on-chip—no external MOSFETs are required.

Maxim's proprietary process technology allows for low- $R_{DSON}$  devices in a small solution size. The total dropout resistance from adapter power input to the battery is  $114m\Omega$  (typ) assuming that the inductor has  $0.04\Omega$  of ESR. This  $114m\Omega$  typical dropout resistance allows for charging a battery up to 3.0A from a 5V supply. The resistance from the BATT-to-SYS node is  $13m\Omega$ , allowing for low power dissipation and long battery life.

A multitude of safety features ensures reliable charging. Features include a charge timer, junction thermal regulation, over/undervoltage protection, and short circuit protection.

The BATT-to-SYS switch has overcurrent protection (see the <u>Main Battery Overcurrent Protection</u> section for more information).

#### **Smart Power Selector (SPS)**

The SPS architecture is a network of internal switches and control loops that distributes energy between an external power source CHGIN, BYP, SYS, and BATT.

<u>Figure 1</u> shows a simplified arrangement for the Smart Power Selector's power steering switches. <u>Figure 2</u> shows a more detailed arrangement of the Smart Power Selector switches and gives them the following names: Q<sub>CHGIN</sub>, Q<sub>HS</sub>, Q<sub>LS</sub>, and Q<sub>BAT</sub>.

### **Switch and Control Loop Descriptions**

- CHGIN Input Switch: Q<sub>CHGIN</sub> provides the input overvoltage protection of +16V. The input switch is either completely

on or completely off. As shown in <u>Figure 2</u>, there are SPS control loops that monitor the current through the input

switches as well as the input voltage.

- DC-DC Switches: Q<sub>HS</sub> and Q<sub>LS</sub> are the DC-DC switches that can operate as a buck (step-down) or a boost (step-up).

When operating as a buck, energy is moved from BYP to SYS. When operating as a boost, energy is moved from SYS to BYP. SPS control loops monitor the DC-DC switch current, the SYS voltage, and the BYP voltage.

- Battery-to-System Switch: Q<sub>BAT</sub> controls the battery charging and discharging. Additionally, Q<sub>BAT</sub> allows the battery

to be isolated from the system (SYS). An SPS control loop monitors the Q<sub>BAT</sub> current.

#### **SYS Regulation Voltage**

- When the DC-DC is enabled as a buck and the charger is enabled but in a non-charging state such as done, thermal shutdown, or timer fault, V<sub>SYS</sub> is regulated to V<sub>BATTREG</sub>, and Q<sub>BAT</sub> is off.

- When the DC-DC is enabled as a buck and charging in trickle-charge, fast-charge, or top-off modes, V<sub>SYS</sub> is regulated to V<sub>SYSMIN</sub> when the V<sub>PRECHG</sub> < V<sub>BATT</sub> < V<sub>SYSMIN</sub>. And, when the DC-DC is enabled as a buck and charging in precharge mode (V<sub>BATT</sub> < V<sub>PRECHG</sub>), V<sub>SYS</sub> is regulated to V<sub>BATTREG</sub>. In these modes, the Q<sub>BAT</sub> switch acts as a linear regulator and dissipates power [P = (V<sub>SYS</sub> V<sub>BATT</sub>) × I<sub>BATT</sub>]. When V<sub>BATT</sub> > V<sub>SYSMIN</sub>, then V<sub>SYS</sub> = V<sub>BATT</sub> + I<sub>BATT</sub> × R<sub>BATZSYS</sub>. In this mode, the Q<sub>BAT</sub> switch is closed.

In all of the above modes, if the combined SYS loading exceeds the input current limit, then  $V_{SYS}$  drops to  $V_{BATT} - V_{BSREG}$ , and the battery provides supplemental current.

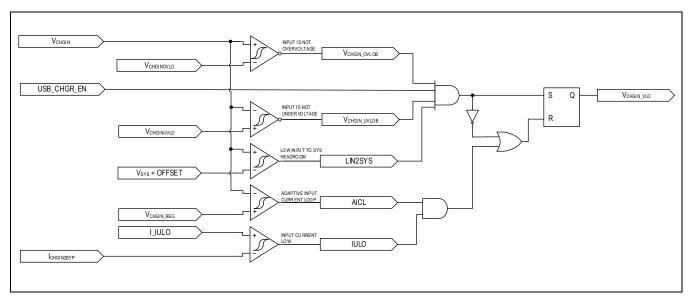

### **Input Validation**

The charger input is compared with several voltage thresholds to determine if it is valid. A charger input must meet the following three characteristics to be valid:

- CHGIN must be above V<sub>CHGIN\_UVLO</sub> to be valid. Once CHGIN is above the UVLO threshold, the information (together

with LIN2SYS, described below) is latched and can only be reset when the charger is in the adaptive input current

loop (AICL) and the input current is lower than the IULO threshold of 60mA. Note that V<sub>CHGIN\_REG</sub> is lower than their

UVLO falling threshold, respectively.

- CHGIN must be below its overvoltage lockout threshold (V<sub>CHGIN OVLO</sub>)

- CHGIN must be above the system voltage by V<sub>CHGIN2SYS</sub>

Figure 3. CHGIN Valid Signal Generation Logic

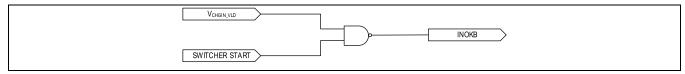

The INOKB pin is pulled down when CHGINOK = 1 and the switcher starts.

Figure 4. INOKB Signal Generation Logic

#### **Input Current Limit**

The IC has two ways to control the input current limit. After the charger-type detection is done, the IC automatically configures the input current limit to the highest settings that the source can provide. If the input source is not a standard power source described by BC1.2, USB Type-C, or proprietary charger type that the IC can detect, the IC sets the input current limit according to R<sub>INLIM</sub>. In the case of floating R<sub>INLIM</sub>, the IC input current limit is set to 500mA when an unknown proprietary charger is detected.

### Input Voltage Regulation Loop

An input voltage regulation loop allows the charger to be well behaved when it is attached to a poor-quality charge source. The loop improves performance with relatively high resistance charge sources that exist when long cables are used or devices are charged with non-compliant USB hub configurations.

The input voltage regulation loop automatically reduces the input current limit to keep the input voltage at V<sub>CHGIN\_REG</sub>. If the input current limit is reduced to I<sub>ULO</sub> (65mA typ) and the input voltage is below V<sub>CHGIN\_REG</sub>, then the charger input is turned off.

### Input Self-Discharge

To ensure that a rapid removal and reinsertion of a charge source always results in a charger input interrupt, the charger input presents loading to the input capacitor to ensure that when the charge source is removed the input voltage decays below the UVLO threshold in a reasonable time ( $t_{INSD}$ ). The input self-discharge is implemented with a 44k $\Omega$  resistor ( $R_{INSD}$ ) from CHGIN input to ground.

### **Charger States**

### Li+/Li-Poly Battery

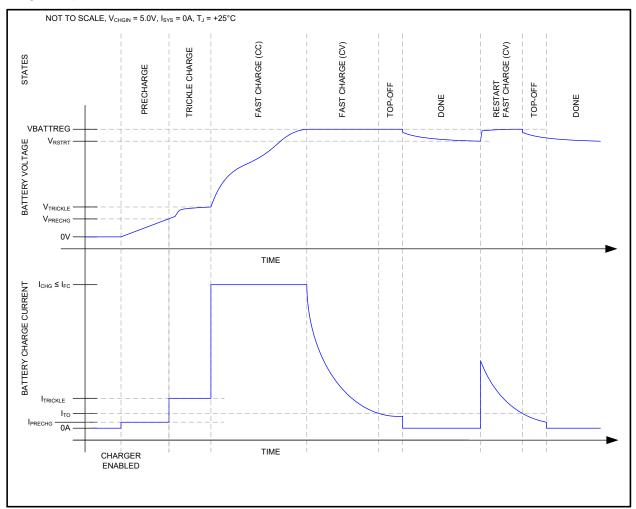

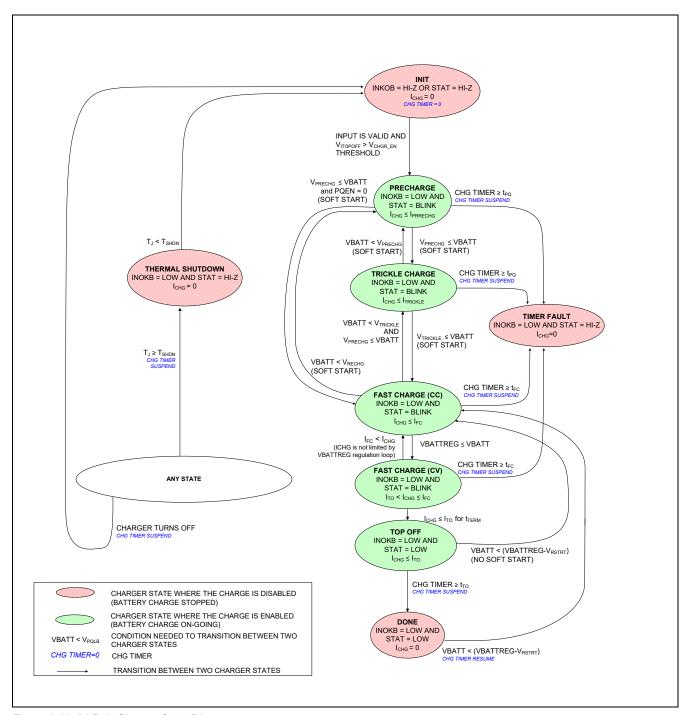

The MAX77787J utilizes several charging states to safely and quickly charge Li+/Li-Poly batteries as shown in <u>Figure 5</u> and <u>Figure 6</u>. Figure 5 shows an exaggerated view of the Li+/Li-Poly battery progressing through the following charge states when there is no system load and the die and battery is close to room temperature: precharge  $\rightarrow$  trickle  $\rightarrow$  fast-charge  $\rightarrow$  top-off  $\rightarrow$  done.

Figure 5. Li+/Li-Poly Charge Profile

Figure 6. Li+/Li-Poly Charger State Diagram

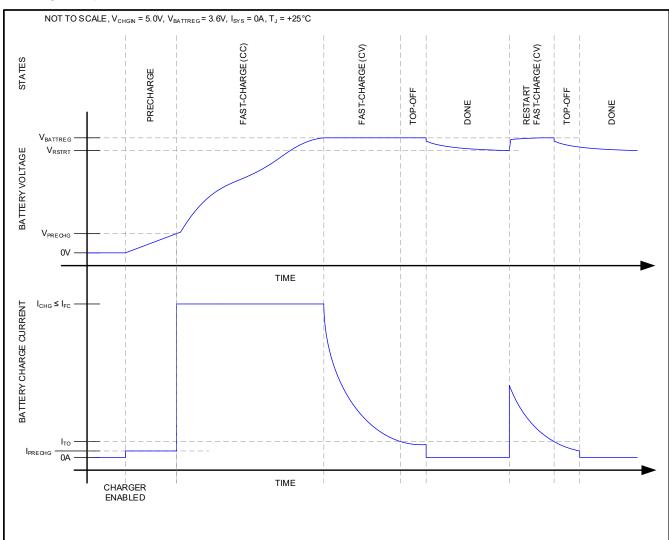

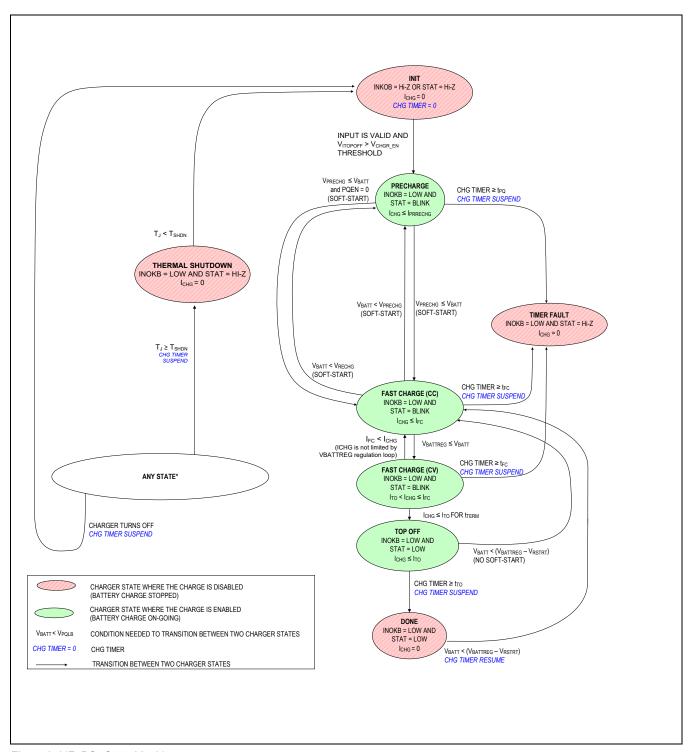

### LiFePO<sub>4</sub> Battery

As for the LiFePO<sub>4</sub> battery, the MAX77787H skips the trickle charge state and directly enters the fast-charge state after the precharge state. <u>Figure 7</u> and <u>Figure 8</u> presents the LiFePO<sub>4</sub> battery charge profile and state machine: precharge  $\rightarrow$  fast-charge  $\rightarrow$  top-off  $\rightarrow$  done.

Figure 7. LiFePO<sub>4</sub> Battery Charge Profile

Figure 8. LiFePO<sub>4</sub> State Machine

#### **INIT State**

From any state shown in <u>Figure 6</u> except thermal shutdown, the "INIT" state is entered whenever the charger inputs CHGIN is invalid or the charger timer is suspended.

While in the "INIT" state, the charger current is 0mA, the charge timer is forced to 0, and the power to the system is provided by the battery.

To exit the "INIT" state the charger input must be valid.

### **Pre-Charge State**

As shown in <u>Figure 6</u>, the pre-charge state occurs when the main battery voltage is less than V<sub>PRECHG</sub>. In the pre-charge state, the charge current into the battery is I<sub>PRECHG</sub>.

The following events cause the state machine to exit this state:

- The main battery voltage rises above V<sub>PRECHG</sub> and the charger enters the next state in the charging cycle, trickle charge.

- If the battery charger remains in this state for longer than t<sub>PQ</sub>, the charger state machine transitions to the timer fault state

Note that the pre-charge state works with battery voltages down to 0V. The low 0V operation typically allows the battery charger to recover batteries that have an "open" internal pack protector. Typically, a pack internal protection circuit opens if the battery has seen an overcurrent, undervoltage, or overvoltage. When a battery with an "open" internal pack protector is used with this charger, the pre-charge mode current flows into the 0V battery—this current raises the pack's terminal voltage to the point where the internal pack protection switch closes.

Note that a normal battery typically stays in the pre-charge state for several minutes or less. Therefore, a battery that stays in the pre-charge state for longer than tp<sub>Q</sub> might be experiencing a problem.

### **Trickle Charge State**

The trickle charge mode described below is for Li-ion and Li-poly batteries only, with charge termination voltage from 4.1V to 4.5V.

As shown in Figure 6, the trickle charge state occurs when VBATT > VPRECHG and VBATT < VTRICKLE.

When the MAX77787J is in its trickle charge state, the charge current in the battery is less than or equal to ITRICKLE.

Charge current might be less than ITRICKLE for the following reasons:

- The charger input is in the input current limit

- The charger input voltage is low

- · The charger is in thermal foldback

- The system load is consuming adapter current. Note that the system load always gets priority over the battery charge current.

The following events cause the state machine to exit this state:

- When the main battery voltage rises above V<sub>TRICKLE</sub>, the charger enters the next state in the charging cycle, fast charge (CC).

- If the battery charger remains in this state for longer than t<sub>PQ</sub>, the charger state machine transitions to the timer fault state.

Note that a normal battery typically stays in the trickle charge state for several minutes or less. Therefore, a battery that stays in trickle charge for longer than  $t_{PQ}$  might be experiencing a problem.

Based on the characteristic of the LiFePO4 battery, the trickle charge state of MAX77787H is disabled. After the precharge state, when V<sub>PRECHG</sub> < V<sub>BATTREG</sub>, MAX77787H enters the fast-charge constant current state to improve the charger efficiency.

### Fast-Charge Constant Current (CC) State

As shown in <u>Figure 6</u>, the fast-charge constant current (CC) state occurs when the main-battery voltage is greater than the trickle threshold and less than the battery regulation threshold ( $V_{TRICKLE} < V_{BATTREG}$ ).

In the fast-charge CC state, the current into the battery is less than or equal to I<sub>FC</sub>. Charge current can be less than I<sub>FC</sub> for the following reasons:

- The charger input is in the input current limit

- · The charger input voltage is low

- · The charger is in thermal foldback

- The system load is consuming adapter current. Note that the system load always gets priority over the battery charge current.

The following events cause the state machine to exit this state:

- When the main battery voltage rises above V<sub>BATTREG</sub>, the charger enters the next state in the charging cycle, fast charge (CV).

- If the battery charger remains in this state for longer than t<sub>FC</sub>, the charger state machine transitions to the timer fault state

The battery charger dissipates the most power in the fast-charge constant current state. This power dissipation causes the internal die temperature to rise. If the die temperature exceeds T<sub>REG</sub>, I<sub>FC</sub> is reduced. See the <u>Thermal Foldback</u> section for more information.

### Fast-Charge Constant Voltage (CV) State

As shown in <u>Figure 6</u>, the fast-charge constant voltage (CV) state occurs when the battery voltage rises to V<sub>BATTREG</sub> from the fast-charge CC state.

In the fast-charge CV state, the battery charger maintains  $V_{BATTREG}$  across the battery and the charge current is less than or equal to  $I_{FC}$ . As shown in <u>Figure 5</u>, charger current decreases exponentially in this state as the battery becomes fully charged.

The Smart Power Selector control circuitry might reduce the charge current lower than the battery can otherwise consume for the following reasons:

- The charger input is in the input current limit

- The charger input voltage is low

- The charger is in thermal foldback

- The system load is consuming adapter current. Note that the system load always gets priority over the battery charge current.

The following events cause the state machine to exit this state:

- When the charger current is below I<sub>TO</sub> for t<sub>TERM</sub>, the charger enters the next state in the charging cycle, top off.

- If the battery charger remains in this state for longer than t<sub>FC</sub>, the charger state machine transitions to the timer fault state.

### **Top-Off State**

As shown in <u>Figure 6</u>, the top-off state can only be entered from the fast-charge CV state when the charger current decreases below  $I_{TO}$  for  $I_{TERM}$ . In the top-off state, the battery charger tries to maintain  $V_{BATTREG}$  across the battery, and typically the charge current is less than or equal to  $I_{TO}$ .

The Smart Power Selector control circuitry might reduce the charge current lower than the battery can otherwise consume for the following reasons:

- The charger input is in the input current limit

- The charger input voltage is low

- The charger is in thermal foldback

- The system load is consuming adapter current. Note that the system load always gets priority over the battery charge current.

The following events cause the state machine to exit this state:

- After being in this state for the top-off time (t<sub>TO</sub>), the charger enters the next state in the charging cycle, done.

- If VBATT < VBATTREG VRSTRT, the charger goes back to the fast charge (CC) state</li>

#### **Done State**

As shown in Figure 6, the battery charger enters its done state after the charger has been in the top-off state for t<sub>TO</sub>.

The following event causes the state machine to exit this state:

• If  $V_{BATT} < V_{BATTREG} - V_{RSTRT}$ , the charger goes back to the fast charge (CC) state

In the done state, the charge current into the battery ( $I_{CHG}$ ) is 0A. In the done state, the charger presents a very low quiescent current to the battery. If the system load presented to the battery is low (<<100 $\mu$ A), then a typical system can remain in the done state for many days. If left in the done state long enough, the battery voltage decays below the restart threshold ( $V_{RSTRT}$ ), and the charger state machine transitions back into the fast-charge CC state. There is no soft-start (di/dt limiting) during the done to fast-charge state transition.

#### **Timer Fault State**

The battery charger provides both a charge timer to ensure safe charging. As shown in <u>Figure 6</u>, the charge timer prevents the battery from charging indefinitely. The time that the charger is allowed to remain in each of its prequalification states is  $t_{PQ}$ . The time that the charger is allowed to remain in the fast-charge CC and CV states is  $t_{FC}$ . Finally, the time that the charger is in the top-off state is  $t_{TO}$ . Upon entering the timer fault state, STAT becomes Hi-Z.

In the timer fault state, the charger is off. The charger input can be removed and re-inserted to exit the timer fault state (see the "any state" bubble in the lower left of <u>Figure 6</u>).

### **Thermal Shutdown State**

As shown in <u>Figure 6</u>, the thermal shutdown state occurs when the battery charger is in any state and the junction temperature  $(T_J)$  exceeds the device's thermal shutdown threshold  $(T_{SHDN})$ . When  $T_J$  is close to  $T_{REG}$ , the charger folds back the input current limit to 0A so that the charger and inputs are effectively off.

In the thermal shutdown state, the charger is off.

### **Reverse Boost Mode**

The DC-DC converter topology of the IC allows it to operate as a buck converter or as a reverse-boost converter. The modes of the DC-DC converter are controlled by ENBST. When ENBST = high, the DC-DC converter operates in reverse boost mode allowing it to source current to BYP and CHGIN, this mode allows current to be sourced from CHGIN and is commonly referred to as OTG mode or a source role. When the OTG mode is enabled, the unipolar CHGIN transfer function measures the current going out of CHGIN. The BYP to CHGIN switch automatically tries to retry after 300ms if CHGIN loading exceeds the 1.5A current limit. If the overload at CHGIN persists, then the CHGIN switch toggles ON and OFF with approximately 60ms ON and approximately 300ms OFF.

The IC also allows it to be sourced from BYP with ENBST = high and STBY = high.

The current through the BYP to CHGIN switch is limited to 1.5A minimum.