# **64 Analog Input Telemetry Controller for Space**

# **Description**

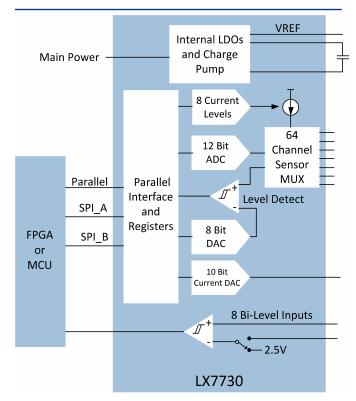

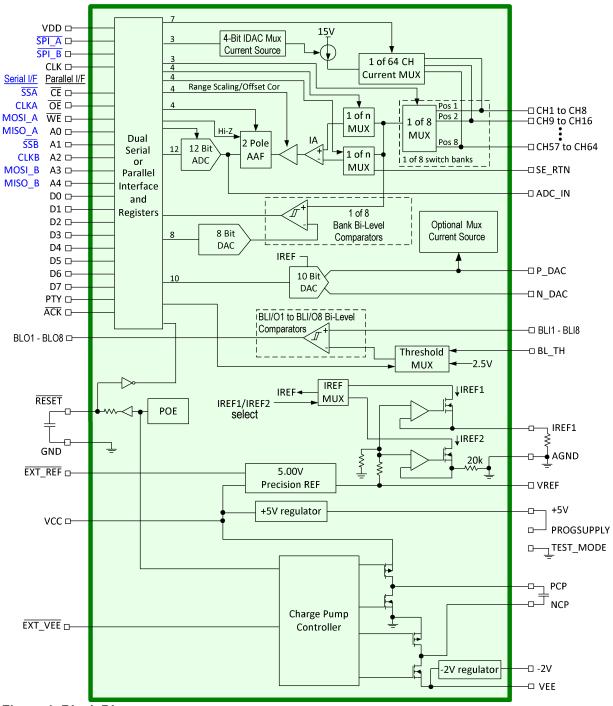

The LX7730 is a spacecraft telemetry manager that is radiation-hardened by design and works with either a space FPGA controller such as <a href="RTG4">RTG4</a>, <a href="RTAX-S/SL">RTAX-S/SL</a>, and <a href="RT PolarFire">RT PolarFire</a>, or a space MCU such as <a href="SAMRH71F20">SAMRH71F20</a>, <a href="SAMV71Q21RT">SAMV71Q21RT</a>, and <a href="SAMSX8ERT">SAMSX8ERT</a>.

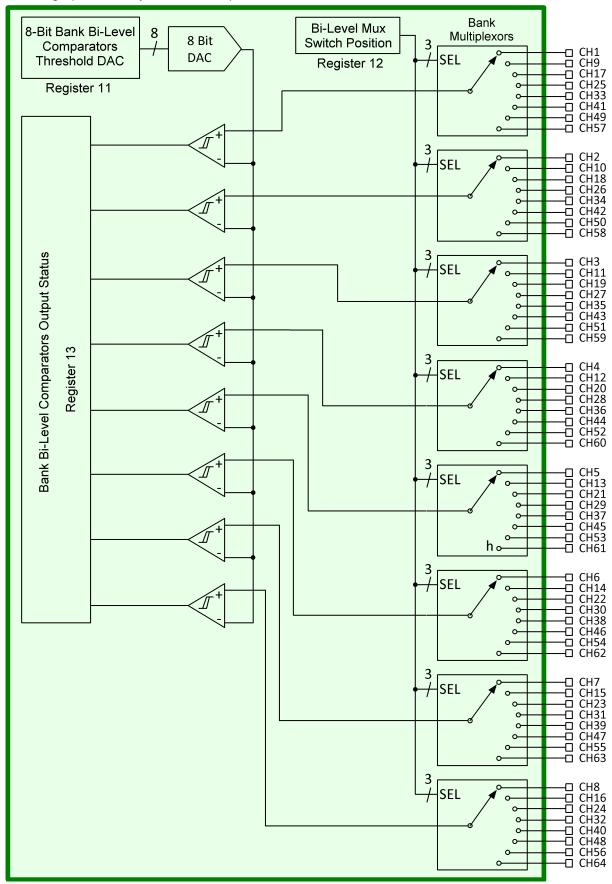

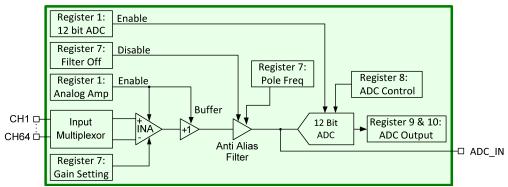

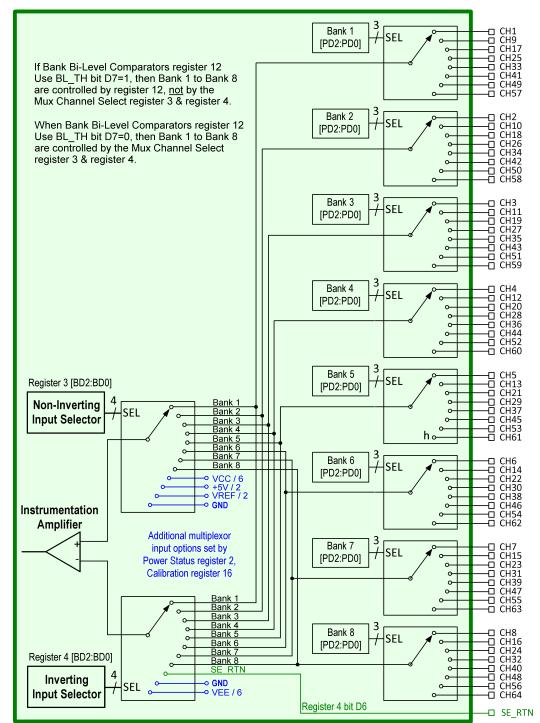

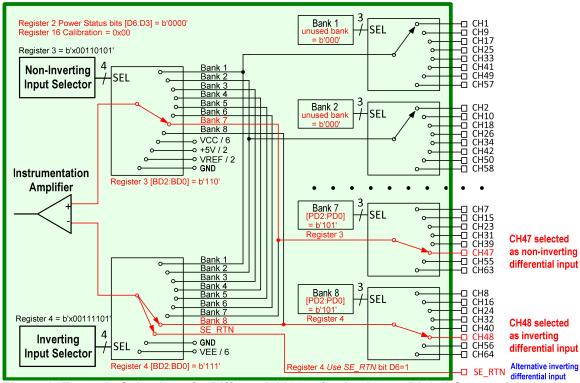

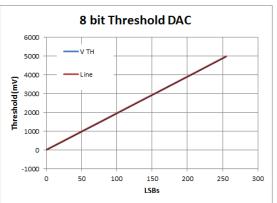

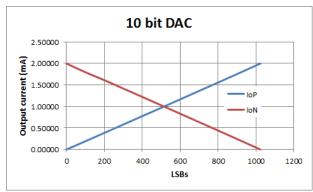

The LX7730 contains a 64 universal input multiplexer that can be configured for a mix of differential and/or single ended sensor inputs. The internal programmable current source can be directed to any of the 64 universal inputs. The universal inputs can be acquired by the internal 12-bit ADC at a sample rate up to 13kHz. The universal inputs also function as variable bi-level inputs with the threshold set by an internal 8-bit DAC. There is an additional 10-bit current DAC with complementary outputs. Finally, there are 8 fixed threshold bi-level inputs with logic outputs.

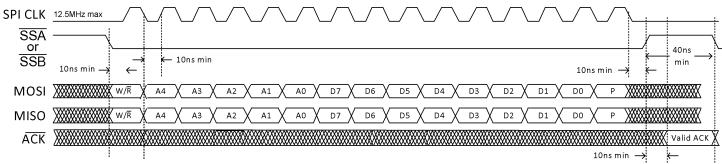

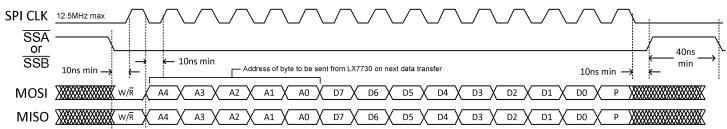

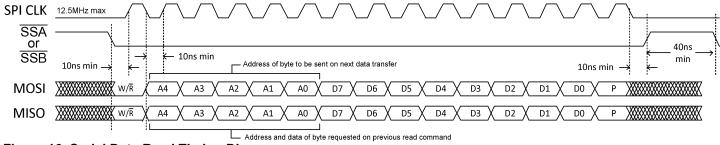

The LX7730 is register programmable with 17 addressable 8-bit registers. Two options are available for communication with the host system controller. First there is an 8-bit parallel bus with 5 address bits, a parity bit, and a read/write bit that can communicate at a speed of up to 25Mword/s. The second option is a pair of 12.5Mbit/s SPI interfaces that support redundant communication to two different hosts.

The LX7730 has enable registers that allow most of the device to be shut down to reduce power consumption, and supports cold sparing on its signal pins. The dielectric isolated process is failsafe.

The LX7730LMFQ offers lower guaranteed operating and standby supply currents than the LX7730MFQ, as shown in the Electrical Characteristics. Operation is identical in all other respects. All other references to LX7730 in this data sheet apply to the LX7730LMFQ, LX7730MFQ, and LX7730LMMF.

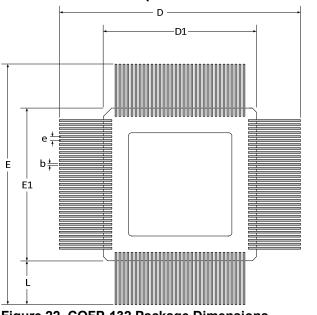

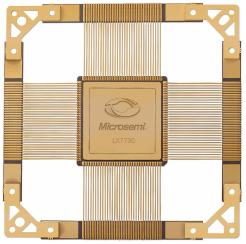

The LX7730(L)MFQ is packaged in a 132-pin hermetic ceramic quad flat pack. The LX7730LMMF is packaged in a lead-free 208 pin non-hermetic plastic quad flat pack. Both parts operate over a 55°C to 125°C temperature range, and are radiation tolerant to 100krad(Si) TID and 50krad(Si) ELDRs, as well as single event effects.

### **Features**

- 64 channel analog input multiplexer

- Break-Before-Make switching

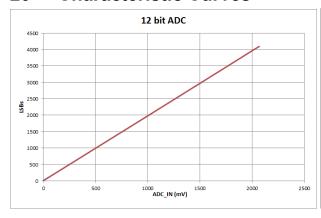

- 13ksps 12-bit ADC

- 1% precision 5V voltage reference

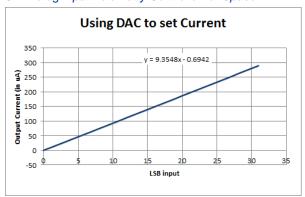

- 3% precision adjustable current source

- Threshold monitoring

- 8 bi-level analog inputs and logic outputs

- 8 additional bi-level inputs from the multiplexer

- 10-bit DAC

- · Parallel interface or dual SPI interface

- Radiation tolerant: 100krad(Si) TID, 50krad(Si) ELDRS, SEL immune up to 87MeV.cm²/mg and 125°C (fluence of 10<sup>8</sup> particles/cm²)

# **Applications**

- Spacecraft health monitoring

- Attitude control

- Payload equipment

**Typical Telemetry System**

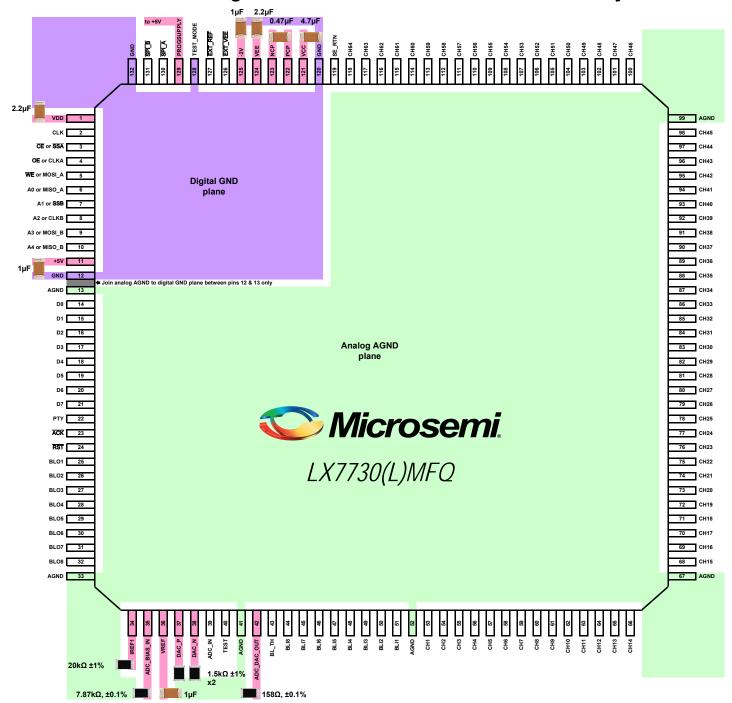

# 1 CQFP-132 Pin Configuration and Pinout with Recommended Layout

# 2 Ordering Information

| Operating Temperature | Package Type | Package     | Part Number   | SMD Number         | Flow                  | Shipping<br>Type |

|-----------------------|--------------|-------------|---------------|--------------------|-----------------------|------------------|

|                       |              |             | LX7730MFQ-V   | SMD5962-1721901VXC | QML-V                 |                  |

|                       | Hermetic     | CQFP        | LX7730MFQ-Q   | SMD5962-1721901QXC | QML-Q                 |                  |

| -55°C                 | Ceramic      | 132L        | LX7730LMFQ-EV | TBD                | MIL-PRF-38535 Class V |                  |

| to                    |              | 1021        | LX7730LMFQ-EQ | TBD                | MIL-PRF-38535 Class Q | Tray             |

| 125°C                 | Ceramic      |             | LX7730MFQ-ES  | ī                  | Engineering Samples   |                  |

|                       | Plastic      | QFP<br>208L | LX7730LMMF    | -                  | JEDEC                 |                  |

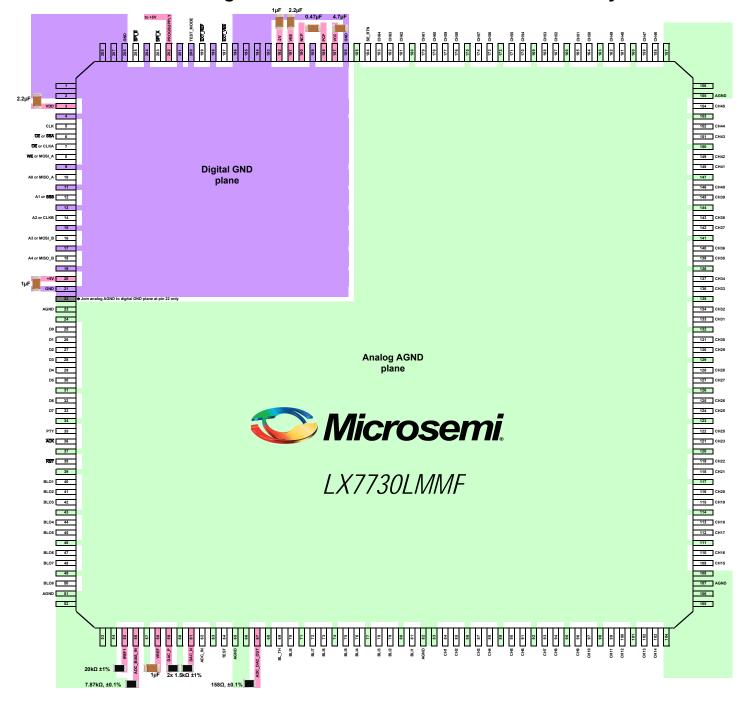

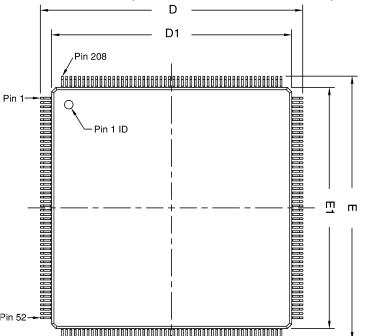

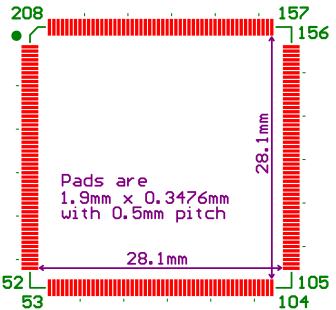

# 3 QFP-208 Pin Configuration and Pinout with Recommended Layout

- Note 1. The layout examples show split planes for SGND and MGND. Separate SGND and MGND planes can be used

- Note 3. The QFP has many unused pins, shown as un-named pins. These pins are not bonded internally. The layout example connects these pins to one or the other of the ground planes to assist with connectivity

- Note 4. The pin marked TEST (CQFP pin 40, QFP pin 64) is a factory test pin which must be left open

# 4 CQFP-132-pin Numbering and Pin Descriptions

|         |                  | •                                |                               | nu Pin Descriptions                                                                                                                                                                                                                                                                                         |

|---------|------------------|----------------------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 132L    | Name             | Pin Type                         | Pin Function                  | Description                                                                                                                                                                                                                                                                                                 |

| 1       | VDD              | Power                            | I/O Supply                    | Connect to the external logic controller's (FPGA, MCU) I/O power supply (2.25V to 5.5V) to set the I/O logic level for all logic I/Os. Bypass close to the pin with a 2.2µF capacitor to GND                                                                                                                |

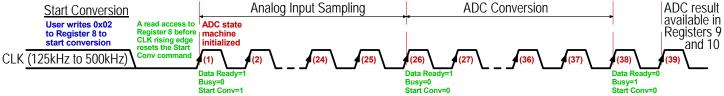

| 2       | CLK              | Logic Input (1M $\Omega$ to GND) | ADC Clock                     | Connect a 125kHz to 500kHz clock to operate the ADC logic                                                                                                                                                                                                                                                   |

| 3       | CE, or<br>SSA    | Logic Input<br>(1MΩ to VDD)      | Chip Enable<br>Slave Select A | Active low chip enable for the parallel interface (SPI_A = SPI_B = 1) Active low slave select for SPI channel A interface (SPI_A = 0, SPI_B = 1)                                                                                                                                                            |

| 4       | OE, or<br>CLKA   | Logic Input (1MΩ to VDD)         | Output Enable<br>Clock A      | Active low output enable (read) for the parallel interface (SPI_A = SPI_B = 1)  Clock input for SPI channel A interface (SPI_A = 0, SPI_B = 1)                                                                                                                                                              |

| 5       | WE, or<br>MOSI_A | Logic Input (1MΩ to VDD)         | Write Enable<br>MOSI A        | Active low write enable for the parallel interface (SPI_A = SPI_B = 1)  Data input for SPI channel A interface (SPI_A = 0, SPI_B = 1)                                                                                                                                                                       |

| 6       | A0, or<br>MISO_A | Logic I/O<br>(1MΩ to GND)        | Address A0<br>MISO A          | Register address bit A0 (LSB) for the parallel interface (SPI_A = SPI_B = 1)  Data output for SPI channel A interface (SPI_A = 0, SPI_B = 1)                                                                                                                                                                |

| 7       | A1, or<br>SSB    | Logic Input<br>(1MΩ to VDD)      | Address A1<br>Slave Select B  | Register address bit A1 for the parallel interface (SPI_A = SPI_B = 1) Active low slave select for SPI channel B interface (SPI_A = 1, SPI_B = 0)                                                                                                                                                           |

| 8       | A2, or<br>CLKB   | Logic Input<br>(1MΩ to GND)      | Address A2<br>Clock B         | Register address bit A2 for the parallel interface (SPI_A = SPI_B = 1)  Clock input for SPI channel B interface (SPI_A = 1, SPI_B = 0)                                                                                                                                                                      |

| 9       | A3, or<br>MOSI B | Logic Input<br>(1MΩ to GND)      | Address A3<br>MOSI B          | Register address bit A3 for the parallel interface (SPI_A = SPI_B = 1)  Data input for SPI channel B interface (SPI_A = 1, SPI_B = 0)                                                                                                                                                                       |

| 10      | A4, or<br>MISO_B | Logic I/O<br>(1MΩ to GND)        | Address A4<br>MISO B          | Register address bit A4 (MSB) for the parallel interface (SPI_A = SPI_B = 1)  Data output for SPI channel B interface (SPI_A = 1, SPI_B = 0)                                                                                                                                                                |

| 11      | +5V              | Power                            | Internal +5V<br>Supply        | Bypass close to the pin with a 1µF capacitor to GND. Optionally overdrive pin with an external 5.5V ±0.25V supply which shuts down the internal regulator                                                                                                                                                   |

| 12      | GND              | Ground                           | Digital and<br>Power Ground   | All GND pins 12, 120, and 132 must be used, connected together via a plane or split-plane on the PCB, and used for connection and termination of digital and power external components. Only join GND here at pin 12 to AGND at pin 13 as a star point                                                      |

| 13      | AGND             | Ground                           | Analog Ground                 | All AGND pins 13, 33, 41, 52, 67, and 99 must be used, connected together via a plane or split-plane on the PCB, and used for termination of analog signals only. Only join AGND here at pin 13 to GND at pin 12 as a star point                                                                            |

| 14 - 21 | D0 - D7          | Logic I/O (1M $\Omega$ to GND)   | Data Bus                      | Data bus D0 (LSB) to D7 (MSB) for the parallel interface                                                                                                                                                                                                                                                    |

| 22      | PTY              | Logic I/O (1M $\Omega$ to GND)   | Data Bus Parity               | Even parity bit for the parallel interface combined address (A0 - A4), data (D0 - D7) bits, and the PTY signal. A write parity error sets the ACK output high                                                                                                                                               |

| 23      | ACK              | Logic Output                     | Data Bus Write<br>Acknowledge | Data write acknowledge output for the serial and parallel interfaces. ACK is active low to validate data (indicate no parity error) for serial or parallel writes to LX7730                                                                                                                                 |

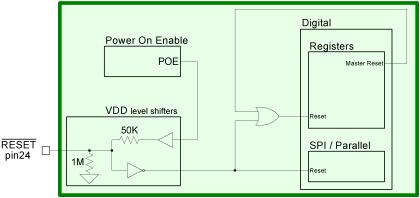

| 24      | RESET            | Logic I/O                        | System Reset                  | Active low input resets the LX7730 internal settings to the POR state. An optional capacitor to GND extends the internal reset time                                                                                                                                                                         |

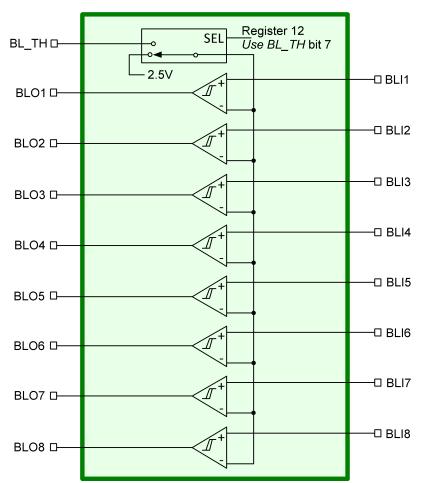

| 25 - 28 | BLO1 -<br>BLO4   | Logic<br>Outputs                 | Bi-Level<br>Outputs 1 to 4    | Output of fixed threshold bi-level monitor (comparator) input BLI1, BLI2, BLI3 and BLI4 at pins 51, 50, 49, and 48 respectively                                                                                                                                                                             |

| 29      | BLO5             | Logic Output                     | Bi-Level Output<br>5          | Output of fixed threshold bi-level monitor (comparator) input BLI5 at pin 47 When the LX7730 is in reset state (either RESET pin 24 held active low, or Master Reset register 0 contains 0x6A) then output is instead VCC LVD status, Power Status Register 2 bit D2 (Table 18 on page 33)                  |

| 30      | BLO6             | Logic Output                     | Bi-Level Output<br>6          | Output of fixed threshold bi-level monitor (comparator) input BLI6 at pin 46 When the LX7730 is in reset state (either RESET pin 24 held active low, or Master Reset register 0 contains 0x6A) then output is instead VEE LVD status, Power Status Register 2 bit D1 (Table 18 on page 33)                  |

| 31      | BLO7             | Logic Output                     | Bi-Level Output<br>7          | Output of fixed threshold bi-level monitor (comparator) input BLI7 at pin 45 When the LX7730 is in reset state (either RESET pin 24 held active low, or Master Reset register 0 contains 0x6A) then output is instead +5V LVD status, Power Status Register 2 bit D0 (Table 18 on page 33)                  |

| 32      | BLO8             | Logic Output                     | Bi-Level Output<br>8          | Output of fixed threshold bi-level monitor (comparator) input BLI8 at pin 44 When the LX7730 is in reset state (either RESET pin 24 held active low, or Master Reset register 0 contains 0x6A) then output is instead Power On Enable status, which is high when the internal logic is ready after power-up |

| 33      | AGND             | Ground                           | Analog Ground                 | All AGND pins 13, 33, 41, 52, 67, and 99 must be used, connected together via a plane or split-plane on the PCB, and used for termination of analog signals only. Only join AGND to GND at pins 12 and 13                                                                                                   |

|           |                     |                  |                                             | CQFP-132-pin Numbering and Pin Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------|---------------------|------------------|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 132L      | Name                | Pin Type         | Pin Function                                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 34        | IREF1               | Analog Input     | Current<br>Reference Bias<br>Resistor       | Connect a $20k\Omega \pm 1\%$ resistor from IREF1 to AGND pin 33 to set the internal reference current. Minimize the track length from the resistor to pin 34, and route a direct track to AGND pin 33. The voltage at IREF1 is 1.6V                                                                                                                                                                                                                                                                             |

| 35        | ADC_<br>BIAS_IN     | Analog Input     | ADC Bias<br>Resistor                        | Connect a $7.87k\Omega$ , $\pm 0.1\%$ resistor from ADC_BIAS_IN to AGND pin 33 to set the internal precision current reference for the ADC. Minimize the track length to pin 35, and route a direct track to AGND pin 33. The voltage at ADC_BIAS_IN is $1.6V$                                                                                                                                                                                                                                                   |

| 36        | VREF                | Analog I/O       | Internal VREF Output External VREF Input    | To use the internal +5V ±1% reference voltage, connect a 1µF capacitor from VREF to AGND pin 33 and tie EXT_REF pin 127 to +5V.  To use an external reference voltage up to 5.5V, connect the external reference to VREF, and tie EXT_REF pin 127 to either GND or AGND                                                                                                                                                                                                                                          |

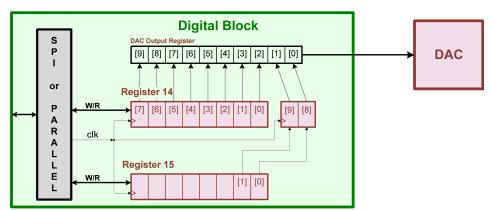

| 37        | DAC_P               | Analog<br>Output | 10-Bit Current<br>DAC (+) Output            | Positive output for the 10-bit current DAC. The code range 0x000 to 0x3FF in the 10-bit DAC registers 14 and 15 (Table 30 on page 46) sources an increasing output current from 0 to 2mA. Terminate DAC_P with a resistor ≤1.5kΩ to AGND to develop a nominal output voltage ≤3V maximum at code 0x3FF.  To assign the DAC_P output alternatively to internal use as the current source for the analog input multiplexer, set Current Mux Level register 5 bit D7 = 0 (Table 21 on page 38) and leave DAC_P open |

| 38        | DAC_N               | Analog<br>Output | 10-Bit Current<br>DAC (-) Output            | Negative output for the 10-bit current DAC. The code range 0x000 to 0x3FF in the 10-bit DAC registers 14 and 15 (Table 30 on page 46) sources a decreasing output current from 2 to 0mA. Terminate DAC_N with a resistor ≤1.5kΩ to AGND to develop a nominal output voltage ≤3V maximum at code 0x000.  If the 10-bit DAC is to be assigned to internal use as the current source for the analog input multiplexer (Current Mux Level register 5 bit D7 = 0), terminate DAC_N to either GND or AGND              |

| 39        | ADC_IN              | Analog I/O       | AFE Output<br>ADC Input                     | Optionally connect a redundant ADC here to monitor the final output from the complete AFE multiplexer-gain-filter system.  Alternatively, to assert a unipolar input signal with 0 to 2V range directly to the ADC, disable the AFE by setting ADC Control register bit D0 = 1 (Table 24 on page 40)                                                                                                                                                                                                             |

| 40        | TEST                | Factory Use      | Test                                        | Internally bonded test node. Leave this pin floating                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 41        | AGND                | Ground           | Analog Ground                               | All AGND pins 13, 33, 41, 52, 67, and 99 must be used, connected together via a plane or split-plane on the PCB, and used for termination of analog signals only. Only join AGND to GND at pins 12 and 13                                                                                                                                                                                                                                                                                                        |

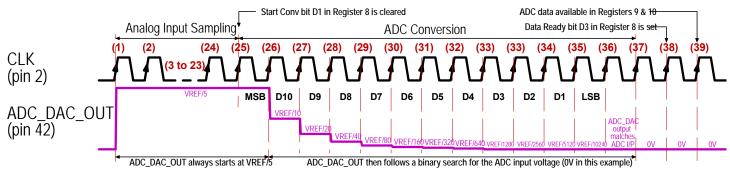

| 42        | ADC_<br>DAC_<br>OUT | Analog Input     | DAC bias<br>resistor                        | Connect a 158Ω, ±0.1% resistor from ADC_ DAC_OUT to AGND pin 41 to provide the precision load for the ADC's current output DAC. Minimize the track length to pin 42, and route a direct track to AGND pin 41. The voltage at ADC_DAC_OUT ranges from 1V minimum to 2V maximum during an ADC conversion, and returns to 0V at the end of the conversion                                                                                                                                                           |

| 43        | BL_TH               | Analog Input     | Bi-Level (-)<br>external<br>threshold input | Optional external negative (-) threshold voltage for the fixed threshold bi-level monitors (comparators) BL1 to BLI8  To use an external reference voltage between 0.1V and 4.9V on BL_TH, set bit B7 in the Bi-Level Bank register 12 (Table 28 on page 44)  To use the internal 2.5V ±50mV threshold, clear bit B7 in the Bi-Level Bank register 12, and connect the BL_TH pin to either GND or AGND                                                                                                           |

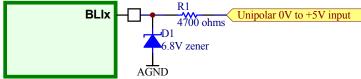

| 44 - 51   | BLI8 -<br>BLI1      | Analog<br>Inputs | Bi-Level (+)<br>inputs 8 to 1               | Fixed threshold bi-level monitor (comparator) positive (+) inputs 8 to 1 which are compared against either an internal 2.5V ±50mV threshold, or an external voltage between 0.1V and 4.9V on the BL_TH pin 43                                                                                                                                                                                                                                                                                                    |

| 52        | AGND                | Ground           | Analog Ground                               | All AGND pins 13, 33, 41, 52, 67, and 99 must be used, connected together via a plane or split-plane on the PCB, and used for termination of analog signals only. Only join AGND to GND at pins 12 and 13                                                                                                                                                                                                                                                                                                        |

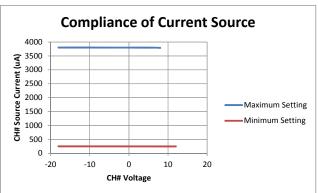

| 53 - 66   | CH1 -<br>CH14       | Analog I/Os      | ADC Inputs,<br>Current Source               | Sensor/signal acquisition inputs up to ±10V, selectable current source output                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 67        | AGND                | Ground           | Analog Ground                               | All AGND pins 13, 33, 41, 52, 67, and 99 must be used, connected together via a plane or split-plane on the PCB, and used for termination of analog signals only. Only join AGND to GND at pins 12 and 13                                                                                                                                                                                                                                                                                                        |

| 68-98     | CH15 -<br>CH45      | Analog I/Os      | ADC Inputs,<br>Current Source               | Sensor/signal acquisition inputs up to ±10V, selectable current source output                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 99        | AGND                | Ground           | Analog Ground                               | All AGND pins 13, 33, 41, 52, 67, and 99 must be used, connected together via a plane or split-plane on the PCB, and used for termination of analog signals only. Only join AGND to GND at pins 12 and 13                                                                                                                                                                                                                                                                                                        |

| 100 - 118 | CH46 -<br>CH64      | Analog I/Os      | ADC Inputs,<br>Current Source               | Sensor/signal acquisition inputs up to ±10V, selectable current source output                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 132L | Name           | Pin Type                       | Pin Function                                         | Description                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------|----------------|--------------------------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

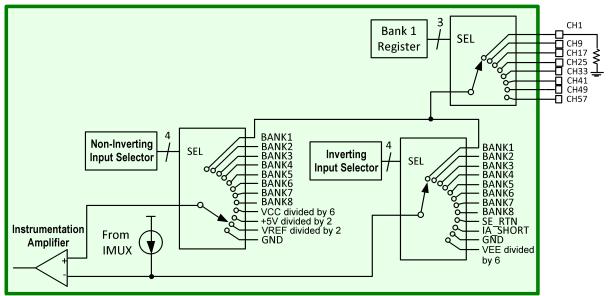

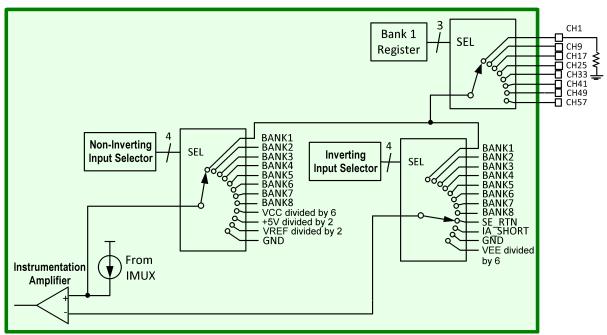

| 119  | SE_RTN         | Analog Input                   | Sensor Return                                        | Common return for single ended sensor/signal inputs. Typically connected to AGND, or a remote signal ground in the range ±10V for differential sensor/signal inputs. Tie to AGND if unused                                                                                                                                                                                                                                             |

| 120  | GND            | Ground                         | Digital and<br>Power Ground                          | All GND pins 12, 120, and 132 must be used, connected together via a plane or split-plane on the PCB, and used for connection and termination of digital and power external components. Only join GND to AGND at pins 12 and 13                                                                                                                                                                                                        |

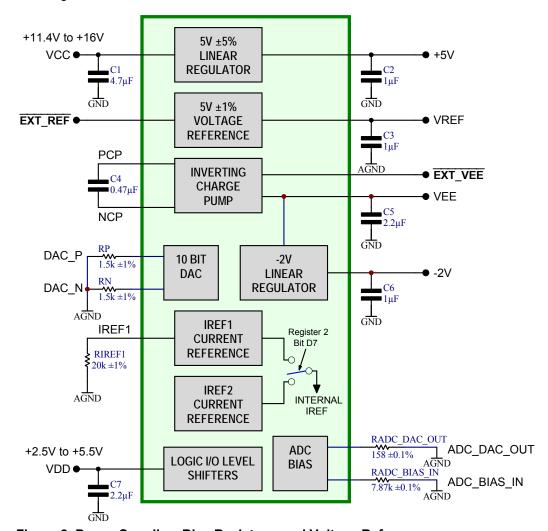

| 121  | VCC            | Power                          | Input Supply                                         | Connect to the main power supply (11.4V to 16V). Bypass close to the pin with a 4.7μF capacitor to GND                                                                                                                                                                                                                                                                                                                                 |

| 122  | PCP            | Output                         | Charge Pump<br>Flying<br>Capacitor non-<br>inverting | Flying capacitor positive node for the internal VEE inverting charge pump. If the internal VEE charge pump is used (EXT_VEE pin 126 tied to +5V), connect a 0.47µF capacitor between this pin and the NCP pin. PCP swings between GND and VCC. If an external VEE supply is used (EXT_VEE pin 126 tied to either GND or AGND), leave PCP open                                                                                          |

| 123  | NCP            | Output                         | Charge Pump<br>Flying<br>Capacitor<br>inverting      | Flying capacitor negative node for the internal VEE inverting charge pump. If the internal VEE charge pump is used (EXT_VEE pin 126 tied to +5V), connect a 0.47µF capacitor between this pin and the PCP pin. NCP swings between GND and VEE.  If an external VEE supply is used (EXT_VEE pin 126 tied to either GND or AGND), leave NCP open                                                                                         |

| 124  | VEE            | Power                          | -10V to -16V<br>Supply                               | If the internal inverting charge pump is used to generate VEE (EXT_VEE pin 126 tied to +5V), bypass close to the pin with a 2.2µF capacitor to GND (not AGND)  If an external VEE supply is used (EXT_VEE pin 126 tied to GND), connect to an external voltage in the range -10V to -16V, and bypass close to the pin with a 2.2µF capacitor to either GND or AGND                                                                     |

| 125  | -2V            | Power                          | Internal -2V<br>Supply                               | Bypass close to the pin with a 1µF capacitor to GND                                                                                                                                                                                                                                                                                                                                                                                    |

| 126  | EXT_VEE        | Logic Input<br>(1MΩ to +5V)    | VEE Select                                           | To use the internal inverting charge pump to generate VEE, tie EXT_VEE to +5V.  To use an external negative supply on VEE pin 124, tie EXT_VEE to either GND or AGND                                                                                                                                                                                                                                                                   |

| 127  | EXT_REF        | Logic Input<br>(1MΩ to +5V)    | VREF Select                                          | To use the internal +5V ±1% reference voltage, tie $\overline{EXT}$ $\overline{REF}$ to +5V.  To use an external reference voltage on VREF pin 36, tie $\overline{EXT}$ $\overline{REF}$ to either GND or AGND                                                                                                                                                                                                                         |

| 128  | TEST_<br>MODE  | Factory Use                    | Test                                                 | Internally bonded test node. Connect to either GND or AGND                                                                                                                                                                                                                                                                                                                                                                             |

| 129  | PROG<br>SUPPLY | Factory Use                    | Test                                                 | Internally bonded test node. Connect to +5V pin 11                                                                                                                                                                                                                                                                                                                                                                                     |

| 130  | SPI_A          | Logic Input<br>(1MΩ to<br>VDD) | SPI Interface A<br>Enable                            | A falling edge on the SPI_A input selects the SPI channel A interface and deselects both the parallel interface and the SPI channel B interface. The SPI channel A interface remains selected while active low, or until a falling edge on the SPI_B input over-rides and selects the SPI channel B interface instead. Select the parallel interface instead of one of the SPI channels by taking both the SPI_A and SPI_B inputs high |

| 131  | SPI_B          | Logic Input<br>(1MΩ to<br>VDD) | SPI Interface B<br>Enable                            | A falling edge on the SPI_B input selects the SPI channel B interface and deselects both the parallel interface and the SPI channel A interface. The SPI channel B interface remains selected while active low, or until a falling edge on the SPI_A input over-rides and selects the SPI channel A interface instead. Select the parallel interface instead of one of the SPI channels by taking both the SPI_A and SPI_B inputs high |

| 132  | GND            | Ground                         | Digital and<br>Power Ground                          | All GND pins 12, 120, and 132 must be used, connected together via a plane or split-plane on the PCB, and used for connection and termination of digital and power external components. Only join GND to AGND at pins 12 and 13                                                                                                                                                                                                        |

5

| 208L               | Name             |                                  | Pin Function                  | Description                                                                                                                                                                                                                                                                                                 |

|--------------------|------------------|----------------------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 208L               | Name             | Pin Type                         | Pin Function                  | Description                                                                                                                                                                                                                                                                                                 |

| 3                  | VDD              | Power                            | I/O Supply                    | Connect to the external logic controller's (FPGA, MCU) I/O power supply (2.25V to 5.5V) to set the I/O logic level for all logic I/Os. Bypass close to the pin with a 2.2µF capacitor to GND                                                                                                                |

| 5                  | CLK              | Logic Input (1M $\Omega$ to GND) | ADC Clock                     | Connect a 125kHz to 500kHz clock to operate the ADC logic                                                                                                                                                                                                                                                   |

| 6                  | CE, or<br>SSA    | Logic Input (1M $\Omega$ to VDD) | Chip Enable<br>Slave Select A | Active low chip enable for the parallel interface (SPI_A = SPI_B = 1) Active low slave select for SPI channel A interface (SPI_A = 0, SPI_B = 1)                                                                                                                                                            |

| 7                  | OE, or<br>CLKA   | Logic Input (1MΩ to VDD)         | Output Enable<br>Clock A      | Active low output enable (read) for the parallel interface (SPI_A = SPI_B = 1)  Clock input for SPI channel A interface (SPI_A = 0, SPI_B = 1)                                                                                                                                                              |

| 8                  | WE, or<br>MOSI A | Logic Input                      | Write Enable<br>MOSI A        | Active low write enable for the parallel interface (SPI_A = SPI_B = 1)  Data input for SPI channel A interface (SPI_A = 0, SPI_B = 1)                                                                                                                                                                       |

| 10                 | A0, or<br>MISO A | Logic I/O<br>(1MΩ to GND)        | Address A0<br>MISO A          | Register address bit A0 (LSB) for the parallel interface (SPI_A = SPI_B = 1)  Data output for SPI channel A interface (SPI_A = 0, SPI_B = 1)                                                                                                                                                                |

| 12                 | A1, or SSB       | Logic Input<br>(1MΩ to VDD)      | Address A1<br>Slave Select B  | Register address bit A1 for the parallel interface (SPI_A = SPI_B = 1)  Active low slave select for SPI channel B interface (SPI_A = 1, SPI_B = 0)                                                                                                                                                          |

| 14                 | A2, or           | Logic Input                      | Address A2                    | Register address bit A2 for the parallel interface (SPI_A = SPI_B = 1)                                                                                                                                                                                                                                      |

| 16                 | A3, or           | (1MΩ to GND) Logic Input         | Clock B<br>Address A3         | Clock input for SPI channel B interface (SPI_A = 1, SPI_B = 0)  Register address bit A3 for the parallel interface (SPI_A = SPI_B = 1)                                                                                                                                                                      |

| 18                 | MOSI_B<br>A4, or | (1MΩ to GND) Logic I/O           | MOSI B<br>Address A4          | Data input for SPI channel B interface (SPI_A = 1, SPI_B = 0)  Register address bit A4 (MSB) for the parallel interface (SPI_A = SPI_B = 1)                                                                                                                                                                 |

| 20                 | MISO_B<br>+5V    | (1MΩ to GND)  Power              | MISO B<br>Internal +5V        | Data output for SPI channel B interface (SPI_A = 1, SPI_B = 0)  Bypass close to the pin with a 1µF capacitor to GND. Optionally overdrive pin  with an external 5 5V 10 25V curply which above the internal regulator.                                                                                      |

|                    |                  |                                  | Supply                        | with an external 5.5V ±0.25V supply which shuts down the internal regulator All GND pins 21, 186, and 206 must be used, connected together via a plane                                                                                                                                                      |

| 21                 | GND              | Ground                           | Digital and<br>Power Ground   | or split-plane on the PCB, and used for connection and termination of digital and power external components. Only join GND here at pin 21 to AGND at pin 23 as a star point                                                                                                                                 |

| 23                 | AGND             | Ground                           | Analog Ground                 | All AGND pins 23, 51, 65, 82, 107, and 155 must be used, connected together via a plane or split-plane on the PCB, and used for termination of analog signals only. Only join AGND here at pin 23 to GND at pin 21 as a star point                                                                          |

| 25 - 30,<br>32, 33 | D0 - D7          | Logic I/O (1M $\Omega$ to GND)   | Data Bus                      | Data bus D0 (LSB) to D7 (MSB) for the parallel interface                                                                                                                                                                                                                                                    |

| 35                 | PTY              | Logic I/O<br>(1MΩ to GND)        | Data Bus Parity               | Even parity bit for the parallel interface combined address (A0 - A4), data (D0 - D7) bits, and the PTY signal. A write parity error sets the ACK output high                                                                                                                                               |

| 36                 | ĀCK              | Logic Output                     | Data Bus Write<br>Acknowledge | Data write acknowledge output for the serial and parallel interfaces. ACK is active low to validate data (indicate no parity error) for serial or parallel writes to LX7730                                                                                                                                 |

| 38                 | RESET            | Logic I/O                        | System Reset                  | Active low input resets the LX7730 internal settings to the POR state. An optional capacitor to GND extends the internal reset time                                                                                                                                                                         |

| 40 - 42,<br>44     | BLO1 -<br>BLO4   | Logic<br>Outputs                 | Bi-Level<br>Outputs 1 to 4    | Output of fixed threshold bi-level monitor (comparator) input BLI1, BLI2, BLI3 and BLI4 at pins 81, 79, 78, and 76 respectively                                                                                                                                                                             |

| 45                 | BLO5             | Logic Output                     | Bi-Level Output<br>5          | Output of fixed threshold bi-level monitor (comparator) input BLI5 at pin 75 When the LX7730 is in reset state (either RESET pin 24 held active low, or Master Reset register 0 contains 0x6A) then output is instead VCC LVD status, Power Status Register 2 bit D2 (Table 18 on page 33)                  |

| 47                 | BLO6             | Logic Output                     | Bi-Level Output<br>6          | Output of fixed threshold bi-level monitor (comparator) input BLI6 at pin 73 When the LX7730 is in reset state (either RESET pin 24 held active low, or Master Reset register 0 contains 0x6A) then output is instead VEE LVD status, Power Status Register 2 bit D1 (Table 18 on page 33)                  |

| 48                 | BLO7             | Logic Output                     | Bi-Level Output<br>7          | Output of fixed threshold bi-level monitor (comparator) input BLI7 at pin 72 When the LX7730 is in reset state (either RESET pin 24 held active low, or Master Reset register 0 contains 0x6A) then output is instead +5V LVD status, Power Status Register 2 bit D0 (Table 18 on page 33)                  |

| 50                 | BLO8             | Logic Output                     | Bi-Level Output<br>8          | Output of fixed threshold bi-level monitor (comparator) input BLI8 at pin 70 When the LX7730 is in reset state (either RESET pin 24 held active low, or Master Reset register 0 contains 0x6A) then output is instead Power On Enable status, which is high when the internal logic is ready after power-up |

| 51                 | AGND             | Ground                           | Analog Ground                 | All AGND pins 23, 51, 65, 82, 107, and 155 must be used, connected together via a plane or split-plane on the PCB, and used for termination of analog signals only. Only join AGND to GND at pins 21 and 23                                                                                                 |

| 208L                                                                        | Name                | Pin Type         | Pin Function                                      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------------------------------------------------------------------|---------------------|------------------|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 55                                                                          | IREF1               | Analog Input     | Current<br>Reference Bias<br>Resistor             | Connect a $20k\Omega$ ±1% resistor from IREF1 to AGND pin 51 to set the internal reference current. Minimize the track length from the resistor to pin 55, and route a direct track to AGND pin 51. The voltage at IREF1 is 1.6V                                                                                                                                                                                                                                                                                 |

| 56                                                                          | ADC_<br>BIAS_IN     | Analog Input     | ADC Bias<br>Resistor                              | Connect a 7.87kΩ, ±0.1% resistor from ADC_BIAS_IN to AGND pin 51 to set the internal precision current reference for the ADC. Minimize the track length to pin 56, and route a direct track to AGND pin 51. The voltage at ADC_BIAS_IN is 1.6V                                                                                                                                                                                                                                                                   |

| 58                                                                          | VREF                | Analog I/O       | Internal VREF<br>Output<br>External VREF<br>Input | To use the internal +5V ±1% reference voltage, connect a 1µF capacitor from VREF to AGND pin 51 and tie EXT_REF pin 199 to +5V.  To use an external reference voltage up to 5.5V, connect the external reference to VREF, and tie EXT_REF pin 199 to either GND or AGND                                                                                                                                                                                                                                          |

| 59                                                                          | DAC_P               | Analog<br>Output | 10-Bit Current<br>DAC (+) Output                  | Positive output for the 10-bit current DAC. The code range 0x000 to 0x3FF in the 10-bit DAC registers 14 and 15 (Table 30 on page 46) sources an increasing output current from 0 to 2mA. Terminate DAC_P with a resistor ≤1.5kΩ to AGND to develop a nominal output voltage ≤3V maximum at code 0x3FF.  To assign the DAC_P output alternatively to internal use as the current source for the analog input multiplexer, set Current Mux Level register 5 bit D7 = 0 (Table 21 on page 38) and leave DAC_P open |

| 61                                                                          | DAC_N               | Analog<br>Output | 10-Bit Current<br>DAC (-) Output                  | Negative output for the 10-bit current DAC. The code range 0x000 to 0x3FF in the 10-bit DAC registers 14 and 15 (Table 30 on page 46) sources a decreasing output current from 2 to 0mA. Terminate DAC_N with a resistor ≤1.5kΩ to AGND to develop a nominal output voltage ≤3V maximum at code 0x000.  If the 10-bit DAC is to be assigned to internal use as the current source for the analog input multiplexer (Current Mux Level register 5 bit D7 = 0), terminate DAC_N to either GND or AGND              |

| 62                                                                          | ADC_IN              | Analog I/O       | AFE Output<br>ADC Input                           | Optionally connect a redundant ADC here to monitor the final output from the complete AFE multiplexer-gain-filter system.  Alternatively, to assert a unipolar input signal with 0 to 2V range directly to the ADC, disable the AFE by setting ADC Control register bit D0 = 1 (Table 24 on page 40)                                                                                                                                                                                                             |

| 64                                                                          | TEST                | Factory Use      | Test                                              | Internally bonded test node. Leave this pin floating                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 65                                                                          | AGND                | Ground           | Analog Ground                                     | All AGND pins 23, 51, 65, 82, 107, and 155 must be used, connected together via a plane or split-plane on the PCB, and used for termination of analog signals only. Only join AGND to GND at pins 21 and 23                                                                                                                                                                                                                                                                                                      |

| 67                                                                          | ADC_<br>DAC_<br>OUT | Analog Input     | DAC bias<br>resistor                              | Connect a $158\Omega$ , $\pm 0.1\%$ resistor from ADC_ DAC_OUT to AGND pin 65 to provide the precision load for the ADC's current output DAC. Minimize the track length to pin 67, and route a direct track to AGND pin 65. The voltage at ADC_DAC_OUT ranges from 1V minimum to 2V maximum during an ADC conversion, and returns to 0V at the end of the conversion                                                                                                                                             |

| 69                                                                          | BL_TH               | Analog Input     | Bi-Level (-)<br>external<br>threshold input       | Optional external negative (-) threshold voltage for the fixed threshold bi-level monitors (comparators) BL1 to BLI8  To use an external reference voltage between 0.1V and 4.9V on BL_TH, set bit B7 in the Bi-Level Bank register 12 (Table 28 on page 44)  To use the internal 2.5V ±50mV threshold, clear bit B7 in the Bi-Level Bank register 12, and connect the BL_TH pin to either GND or AGND                                                                                                           |

| 70, 72,<br>73, 75,<br>76, 78,<br>79, 81                                     | BLI8 -<br>BLI1      | Analog<br>Inputs | Bi-Level (+) inputs 8 to 1                        | Fixed threshold bi-level monitor (comparator) positive (+) inputs 8 to 1 which are compared against either an internal 2.5V ±50mV threshold, or an external voltage between 0.1V and 4.9V on the BL_TH pin 69                                                                                                                                                                                                                                                                                                    |

| 82                                                                          | AGND                | Ground           | Analog Ground                                     | All AGND pins 23, 51, 65, 82, 107, and 155 must be used, connected together via a plane or split-plane on the PCB, and used for termination of analog signals only. Only join AGND to GND at pins 21 and 23                                                                                                                                                                                                                                                                                                      |

| 84, 85,<br>87, 88,<br>90, 91,<br>93, 94,<br>96, 97,<br>99, 100,<br>102, 103 | CH1 -<br>CH14       | Analog I/Os      | ADC Inputs,<br>Current Source                     | Sensor/signal acquisition inputs up to ±10V, selectable current source output                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 107                                                                         | AGND                | Ground           | Analog Ground                                     | All AGND pins 23, 51, 65, 82, 107, and 155 must be used, connected together via a plane or split-plane on the PCB, and used for termination of analog signals only. Only join AGND to GND at pins 21 and 23                                                                                                                                                                                                                                                                                                      |

| 208L                                                                                                                                                                               | Name           | Pin Type                    | Pin Function                                         | Description                                                                                                                                                                                                                                                                                                                                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------------------|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 109, 110,                                                                                                                                                                          |                |                             |                                                      |                                                                                                                                                                                                                                                                                                                                                                    |

| 112, 113,<br>115, 116,<br>118, 119,<br>121, 122,<br>124, 125,<br>127, 128,<br>130, 131,<br>133, 134,<br>136, 137,<br>139, 140,<br>142, 143,<br>145, 146,<br>148, 149,<br>151, 152, | CH15 -<br>CH45 | Analog I/Os                 | ADC Inputs,<br>Current Source                        | Sensor/signal acquisition inputs up to ±10V, selectable current source output                                                                                                                                                                                                                                                                                      |

| 155                                                                                                                                                                                | AGND           | Ground                      | Analog Ground                                        | All AGND pins 23, 51, 65, 82, 107, and 155 must be used, connected together via a plane or split-plane on the PCB, and used for termination of analog signals only. Only join AGND to GND at pins 21 and 23                                                                                                                                                        |

| 158, 159,<br>161, 162,<br>164, 165,<br>167, 168,<br>170, 171,<br>173, 174,<br>176, 177,<br>178, 179,<br>181, 182,<br>183                                                           | CH46 -<br>CH64 | Analog I/Os                 | ADC Inputs,<br>Current Source                        | Sensor/signal acquisition inputs up to ±10V, selectable current source output                                                                                                                                                                                                                                                                                      |

| 184                                                                                                                                                                                | SE_RTN         | Analog Input                | Sensor Return                                        | Common return for single ended sensor/signal inputs. Typically connected to AGND, or a remote signal ground in the range ±10V for differential sensor/signal inputs. Tie to AGND if unused                                                                                                                                                                         |

| 186                                                                                                                                                                                | GND            | Ground                      | Digital and<br>Power Ground                          | All GND pins 21, 186, and 206 must be used, connected together via a plane or split-plane on the PCB, and used for connection and termination of digital and power external components. Only join GND to AGND at pins 21 and 23                                                                                                                                    |

| 187                                                                                                                                                                                | VCC            | Power                       | Input Supply                                         | Connect to the main power supply (11.4V to 16V). Bypass close to the pin with a 4.7µF capacitor to GND                                                                                                                                                                                                                                                             |

| 188                                                                                                                                                                                | PCP            | Output                      | Charge Pump<br>Flying<br>Capacitor non-<br>inverting | Flying capacitor positive node for the internal VEE inverting charge pump. If the internal VEE charge pump is used (EXT_VEE pin 197 tied to +5V), connect a 0.47µF capacitor between this pin and the NCP pin. PCP swings between GND and VCC.  If an external VEE supply is used (EXT_VEE pin 197 tied to either GND or AGND), leave PCP open                     |

| 190                                                                                                                                                                                | NCP            | Output                      | Charge Pump<br>Flying<br>Capacitor<br>inverting      | Flying capacitor negative node for the internal VEE inverting charge pump. If the internal VEE charge pump is used (EXT_VEE pin 197 tied to +5V), connect a 0.47µF capacitor between this pin and the PCP pin. NCP swings between GND and VEE.  If an external VEE supply is used (EXT_VEE pin 197 tied to either GND or AGND), leave NCP open                     |

| 191                                                                                                                                                                                | VEE            | Power                       | -10V to -16V<br>Supply                               | If the internal inverting charge pump is used to generate VEE (EXT_VEE pin 197 tied to +5V), bypass close to the pin with a 2.2µF capacitor to GND (not AGND)  If an external VEE supply is used (EXT_VEE pin 197 tied to GND), connect to an external voltage in the range -10V to -16V, and bypass close to the pin with a 2.2µF capacitor to either GND or AGND |

| 192                                                                                                                                                                                | -2V            | Power                       | Internal -2V<br>Supply                               | Bypass close to the pin with a 1µF capacitor to GND                                                                                                                                                                                                                                                                                                                |

| 197                                                                                                                                                                                | EXT_VEE        | Logic Input<br>(1MΩ to +5V) | VEE Select                                           | To use the internal inverting charge pump to generate VEE, tie EXT_VEE to +5V.  To use an external negative supply on VEE pin 191, tie EXT_VEE to either GND or AGND                                                                                                                                                                                               |

| 199                                                                                                                                                                                | EXT_REF        | Logic Input<br>(1MΩ to +5V) | VREF Select                                          | To use the internal +5V ±1% reference voltage, tie EXT_ REF to +5V.  To use an external reference voltage on VREF pin 58, tie EXT_ REF to either GND or AGND                                                                                                                                                                                                       |

Microsemi.

64 Analog Input Telemetry Controller for Space

| 208L | Name           | Pin Type                       | Pin Function                | Description                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------|----------------|--------------------------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 200  | TEST_<br>MODE  | Factory Use                    | Test                        | Internally bonded test node. Connect to either GND or AGND                                                                                                                                                                                                                                                                                                                                                                             |

| 202  | PROG<br>SUPPLY | Factory Use                    | Test                        | Internally bonded test node. Connect to +5V pin 11                                                                                                                                                                                                                                                                                                                                                                                     |

| 203  | SPI_A          | Logic Input<br>(1MΩ to<br>VDD) | SPI Interface A<br>Enable   | A falling edge on the SPI_A input selects the SPI channel A interface and deselects both the parallel interface and the SPI channel B interface. The SPI channel A interface remains selected while active low, or until a falling edge on the SPI_B input over-rides and selects the SPI channel B interface instead. Select the parallel interface instead of one of the SPI channels by taking both the SPI_A and SPI_B inputs high |

| 205  | SPI_B          | Logic Input<br>(1MΩ to<br>VDD) | SPI Interface B<br>Enable   | A falling edge on the SPI_B input selects the SPI channel B interface and deselects both the parallel interface and the SPI channel A interface. The SPI channel B interface remains selected while active low, or until a falling edge on the SPI_A input over-rides and selects the SPI channel A interface instead. Select the parallel interface instead of one of the SPI channels by taking both the SPI_A and SPI_B inputs high |

| 206  | GND            | Ground                         | Digital and<br>Power Ground | All GND pins 21, 186, and 206 must be used, connected together via a plane or split-plane on the PCB, and used for connection and termination of digital and power external components. Only join GND to AGND at pins 21 and 23                                                                                                                                                                                                        |

Note: Pin numbers not shown in the table above are not bonded internally.

# 6 Absolute Maximum Ratings

Note: Stresses above those listed in "ABSOLUTE MAXIMUM RATINGS", may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

| Parameter                                                                                                                                                          | Min  | Max          | Units |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------|-------|

| Main Power (VCC) to GND                                                                                                                                            | -0.5 | 20           | V     |

| Logic Supply Voltage (VDD) to GND                                                                                                                                  | -0.5 | 7            | V     |

| +5V (current internally limited)                                                                                                                                   | -0.5 | 7            | V     |

| VEE (current internally limited)                                                                                                                                   | -20  | +0.5         | V     |

| FPGA or MCU system controller interface (pins 2 - pin 32) to GND                                                                                                   | -0.5 | 7            | V     |

| Sensor Inputs (CH1 - CH64, SE_RTN) to GND (VCC = GND)                                                                                                              | -20  | 20           | V     |

| Sensor Inputs (CH1 - CH64, SE_RTN) to GND (VCC = 11.4V to 16V)                                                                                                     | -20  | VCC + 2.5V   | V     |

| Bi-Level Inputs (BLI1 to 8) to GND                                                                                                                                 | -10  | 10           | V     |

| Input clamp currents                                                                                                                                               |      | 5            | mA    |

| ADC_IN, DAC_N, DAC_P, RESET, VREF, BL_TH, IREF1 to GND                                                                                                             | -0.5 | 7            | V     |

| Operating Junction Temperature                                                                                                                                     | -55  | 150          | °C    |

| Storage Junction Temperature                                                                                                                                       | -65  | 160          | °C    |

| ESD Susceptibility (HBM, ML_STD883, Method 3015.7) Host system controller interface pins 2 to 10, 14 to 32, 126 to 128, 130, 131 Power pins 1, 11, 121 to 125, 129 |      | 1000         | V     |

| ESD Susceptibility (HBM, ML_STD883, Method 3015.7) Analog channel inputs CH1 to CH64 and BLI1 to BLI8 bi-level inputs                                              |      | 500          | V     |

| Peak Lead Solder Temperature (10 seconds)                                                                                                                          |      | 260 (+0, -5) | °C    |

### 7 Operating Ratings

Note: Performance is generally guaranteed over this range as further detailed below under Electrical Characteristics.

| Parameter                                              | Min  | Max                 | Units |

|--------------------------------------------------------|------|---------------------|-------|

| VCC                                                    | 11.4 | 16                  | V     |

| VDD                                                    | 2.25 | 5.5                 | V     |

| VEE (when externally applied)                          | -16  | -10                 | V     |

| +5V (current internally limited)                       | 4.5  | 5.5                 | V     |

| FPGA or MCU system controller Interface to GND         | 0    | 5.5                 | V     |

| Sensor Inputs (CH1 - CH64, SE_RTN) to GND              | -10  | 10                  | V     |

| Bi-Level Inputs (BLI1 to BLI8) to GND                  | 0    | 8                   | V     |

| Input Clamp Currents                                   |      | Fault condition ≤ 3 | mA    |

| ADC_IN, DAC_N, DAC_P, RESET, VREF, BL_TH, IREF1 to GND | 0    | 5.5                 | V     |

| Current from Reference Voltage (VREF pin)              | 0    | 10                  | mA    |

# 8 Thermal Properties

Note: The  $\theta_{JC}$  numbers assume no forced airflow. Junction temperature is calculated using  $T_J = T_C + (PD \times \theta_{JC})$ . In particular,  $\theta_{JC}$  is a function of the PCB construction. The stated number below is for a four-layer board in accordance with JESD-51 (JEDEC).

| Package  | Thermal Resistance | Тур | Units |

|----------|--------------------|-----|-------|

| CQFP-132 | Δ                  | 10  | °C/W  |

| QFP-208  | θјс                | 6.5 | C/VV  |

### 9 Heatsink Recommendations

The top or the base of the plastic package can be used as the heat conducting surface. It is recommended to use the base of the ceramic package as the surface for conducting heat from the package. The metal package top is attached to the package body at the top of relatively thin cavity walls, and so has a much higher thermal resistance from the die than the base of the package. The leads can be formed to mount the part upside down if necessary. It is recommended to apply a thermal interface material between either package and its heat dissipater. The heat dissipater can be copper layers within a multilayer circuit board to spread heat laterally across the board, or a direct mounted dissipation element.

### 10 Electrical Characteristics

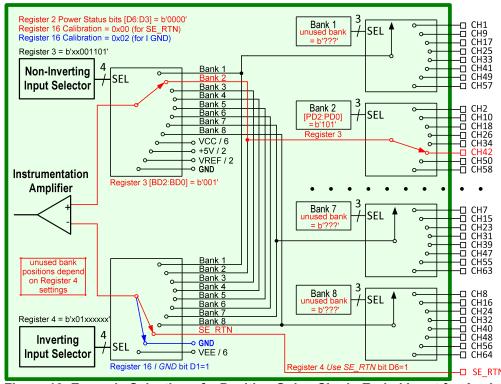

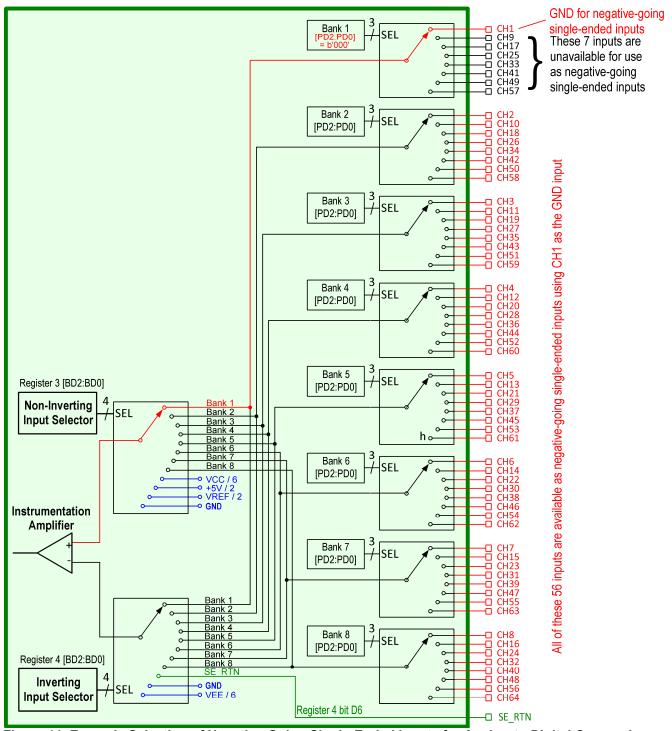

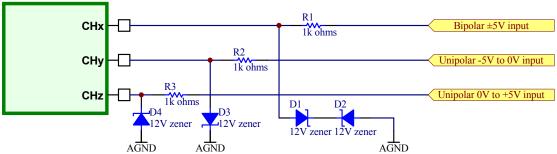

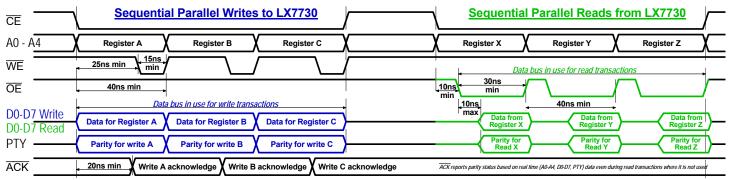

The following specifications apply over the operating ambient temperature of -55°C  $\leq$  T<sub>A</sub>  $\leq$  125°C except where otherwise noted with the following test conditions: VCC = 15V, VDD = 3.3V; R<sub>IREF</sub> = 20k $\Omega$  ±1%; RADC\_BIAS\_IN = 7.87k $\Omega$  ±0.1%; RADC\_DAC\_OUT = 158 $\Omega$  ±0.1%;  $\overline{EXT_VEE}$  open,  $\overline{EXT_REF}$  open; CH1 and CH2 are selected with CH2 grounded; CLK = 500kHz. Register 7 = b'001010xx' setting 10kHz anti-alias filtering. Typical parameters refer to T<sub>J</sub> = 25°C. Positive currents flow into pins. Specifications apply to both LX7730 and LX7730L unless otherwise stated.

| Internally Regulated  V_VEE  V+5V NOM  VREF NOM  VIREF  Analog MUX  V_CH#_DIFF  V_CH#_CLP_P  V_CH#_CLP_P  All to V_CH1  VADC_IN  I_CH#_BIAS | VEE voltage +5V voltage VREF voltage IREF pin voltage  Differential Range Common Mode Range Voltage Clamp (power applied) Voltage Clamp (VCC=VEE = 0)  CH# to CH# Isolation  Settling Time Bias Current | VCC -  VEE   R <sub>IREF</sub> = $20k\Omega$ CH# to CH#, or CH# to SE_RTN  With V <sub>CH1</sub> - V <sub>CH2</sub> = 5V  Clamp Current = 1mA (into pin) (1)  Clamp Current = 1mA (out of pin)  CH1 and SE_RTN selected; CH2 to CH64 each with series $2k\Omega$ to a 10kHz common source, CH1 with $2k\Omega$ to GND. SE_RTN to GND  Including dead time | 1.5<br>4.75<br>4.95<br>1.568<br>0<br>5<br>VCC<br>23<br>16<br>23 | 2.6<br>5.00<br>5.00<br>1.600<br>1.600           | 3<br>5.25<br>5.05<br>1.632<br>5<br>5<br>17<br>-16<br>23<br>-16 | V             |