# *F1977 Datasheet*

5 to 3000 MHz

## 7-Bit, 75 Ω, Digital Step Attenuator

## **GENERAL DESCRIPTION**

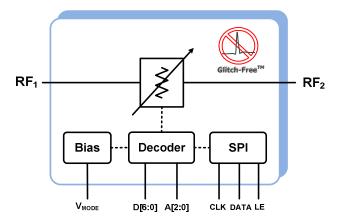

This document describes the specification for the F1977 Digital Step Attenuator. The F1977 is part of a family of *Glitch-Free*<sup>TM</sup> DSAs optimized for the demanding requirements of CATV and Satellite systems. These devices are offered in a compact 5 mm x 5 mm 32 pin QFN package with 75  $\Omega$  impedances for ease of integration.

## **COMPETITIVE ADVANTAGE**

Digital step attenuators are used in Receivers and Transmitters to provide gain control. The F1977 is a 7-bit step attenuator optimized for these demanding applications. The silicon design has very low insertion loss, low distortion (+64 dBm IIP3) and pinpoint attenuation accuracy. Most importantly, the F1977 includes IDT's *Glitch-Free*<sup>TM</sup> technology which results in low overshoot & ringing during MSB transitions.

- ✓ Lowest insertion loss for best SNR

- ✓ Extremely accurate attenuation levels.

- ✓ Ultra low distortion.

- ✓ Glitch-Free<sup>™</sup> technology to protect PA or ADC during transitions between attenuation states.

## **APPLICATIONS**

- CATV Infrastructure

- CATV Set-Top Boxes

- CATV Satellite Modems

- Data Network Equipment

- Fiber Networks

## **Ordering Information**

## FEATURES

- Serial & 7 bit Parallel Interface

- 31.75 dB Control Range

- 0.25 dB step

- *Glitch-Free<sup>†M</sup>* for low transient overshoot

- Low Insertion Loss: 1.4 dB @ 1 GHz

- Ultra linear IIP3: +64 dBm

- Attenuation Error: -0.1 dB @ 1 GHz

- Stable Attenuator Accuracy over temperature

- Bi-directional RF use

- 3.00 V to 5.25 V supply

- 1.8 V or 3.3 V control logic

- Low Current Consumption: 325 µA typical

- -40 °C to +105 °C operating temperature

- 5 mm x 5 mm Thin QFN 32 pin package

### **FUNCTIONAL BLOCK DIAGRAM**

## ABSOLUTE MAXIMUM RATINGS

| Parameter                                                 | Symbol              | Min  | Max                                     | Units |

|-----------------------------------------------------------|---------------------|------|-----------------------------------------|-------|

| V <sub>DD</sub> to GND                                    | $V_{DD}$            | -0.3 | +5.5                                    | V     |

| D[6:0], DATA, CLK, LE, A0, A1, A2, V <sub>MODE</sub>      | V <sub>CNTL</sub>   | -0.3 | Minimum<br>(V <sub>DD</sub> + 0.3, 3.9) | V     |

| DC Voltage RF1, RF2                                       | $V_{RF}$            | -0.3 | +0.3                                    | V     |

| Maximum Input Power applied<br>to RF1 or RF2 (>100 MHz)   | $P_{RF}$            |      | +34                                     | dBm   |

| Maximum Junction Temperature                              | $T_{Jmax}$          |      | +150                                    | °C    |

| Storage Temperature Range                                 | T <sub>ST</sub>     | -65  | +150                                    | °C    |

| Lead Temperature (soldering, 10 s)                        | T <sub>LEAD</sub>   |      | +260                                    | °C    |

| Electrostatic Discharge – HBM<br>(JEDEC/ESDA JS-001-2012) | V <sub>ESDHBM</sub> |      | 1000<br>(Class 1C)                      | V     |

| ESD Voltage – CDM<br>(Per JESD22-C101F)                   | V <sub>ESDCDM</sub> |      | 500<br>(Class C2)                       | V     |

Stresses above those listed above may cause permanent damage to the device. Functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## ESD CAUTION

This product features proprietary protection circuitry. However, it may be damaged if subjected to high energy ESD. Please use proper ESD precautions when handling to avoid damage or loss of performance.

## **PACKAGE THERMAL AND MOISTURE CHARACTERISTICS**

| $\theta_{JA}$ (Junction – Ambient)                                          | 40 °C/W |

|-----------------------------------------------------------------------------|---------|

| $\theta_{JC}$ (Junction – Case) [The Case is defined as the exposed paddle] | 4 °C/W  |

| Moisture Sensitivity Rating (Per J-STD-02                                   | MSL1    |

| Parameter                   | Symbol            | Conditions     | Min | Тур | Max             | Units |

|-----------------------------|-------------------|----------------|-----|-----|-----------------|-------|

| Supply Voltage              | V <sub>DD</sub>   |                | 3   |     | 5.25            | V     |

| Frequency Range             | F <sub>RF</sub>   |                | 5   |     | 3000            | MHz   |

| Operating Temperature Range | T <sub>CASE</sub> | Exposed Paddle | -40 |     | 105             | °C    |

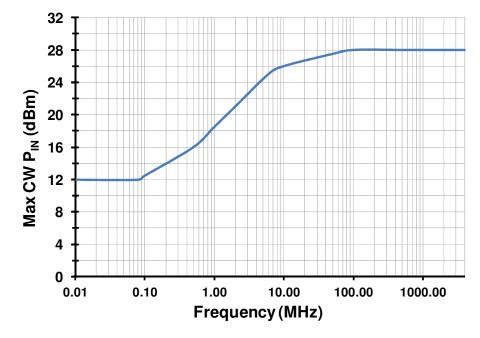

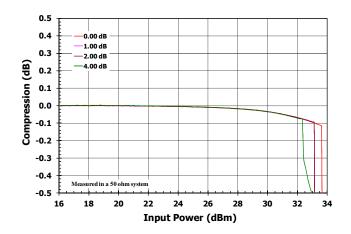

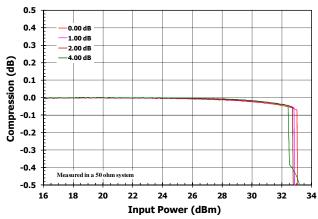

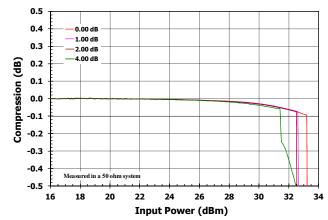

| RF CW Input Power           | P <sub>cw</sub>   | RF1 or RF2     |     |     | See<br>Figure 1 | dBm   |

| RF1 Impedance               | Z <sub>RF1</sub>  | Single Ended   |     | 75  |                 | Ω     |

| RF2 Impedance               | Z <sub>RF2</sub>  | Single Ended   |     | 75  |                 | Ω     |

## F1977 RECOMMENDED OPERATING CONDITIONS

Figure 1 - Maximum Continuous Operating RF input power versus Input Frequency

## **F1977 SPECIFICATION**

Specifications apply at  $V_{DD}$  = +3.3 V,  $T_{CASE}$  = +25°C,  $F_{RF}$  = 1 GHz, Pin = -10 dBm unless otherwise noted. Serial Mode.  $Z_{RF1} = Z_{RF2} = 75 \Omega$ . EVkit losses are de-embedded unless otherwise noted.

| Parameter                                  | Symbol             | Conditions                                                | Min               | Тур   | Max             | Units |

|--------------------------------------------|--------------------|-----------------------------------------------------------|-------------------|-------|-----------------|-------|

|                                            |                    | CLK, LE, DATA, D[6:0],<br>A0, A1, A2, V <sub>MODE</sub>   |                   |       |                 |       |

| Logic Input High                           | $V_{IH}$           | V <sub>DD</sub> > 3.6 V                                   | 1.17 <sup>1</sup> |       | 3.6             | v     |

|                                            |                    | $3.0 \le V_{DD} \le 3.6$                                  | 1.17              |       | $V_{\text{DD}}$ | v     |

| Logic Input Low                            | V <sub>IL</sub>    | CLK, LE, DATA, D[6:0],<br>A0, A1, A2, V <sub>MODE</sub>   |                   |       | 0.63            | V     |

| Logic Current                              | $I_{IH,} I_{IL}$   | Individual Pins                                           | -40               |       | +40             | μA    |

| Supply Current                             | т                  | V <sub>DD</sub> = 3.3 V                                   |                   | 322   | 365             |       |

| Supply Current                             | $I_{DD}$           | $V_{DD} = 5.0 V$                                          |                   | 375   |                 | μA    |

| Attenuation Range                          | ATT <sub>RNG</sub> |                                                           |                   | 31.75 |                 | dB    |

| Minimum Gain Step                          | LSB                | Monotonic for $F_{RF} \leq 3 \text{ GHz}$                 |                   | 0.25  |                 | dB    |

| Incortion Loss                             | TI                 | $F_{RF} = 1 \text{ GHz}$                                  |                   | 1.4   | 1.9             | ٩D    |

| Insertion Loss                             | IL                 | $F_{RF} = 2 \text{ GHz to } 3 \text{ GHz}$                |                   | 2.2   |                 | dB    |

| Relative Insertion Phase                   | <b>•</b>           | $F_{RF} = 1 \text{ GHz}$                                  |                   | 18    |                 | dog   |

| (A <sub>min</sub> vs. A <sub>max</sub> )   | $\Phi_{\Delta}$    | $F_{RF} = 2 \text{ GHz}$                                  |                   | 36    |                 | deg   |

| Step Error<br>(Differential Non-Linearity) | DNL                | Max error between adjacent steps                          |                   | 0.10  |                 | dB    |

| Absolute Attenuation Error                 | INL                | Max Error for state 19.75 dB,<br>$F_{RF} = 1 \text{ GHz}$ | -0.4              | 0.1   | +0.5            | dP    |

| (Integral Non-Linearity)                   | INL                | Max Error, over all states $F_{RF} = 1 \text{ GHz}$       | -0.8              |       | +0.5            | – dB  |

| Tana di Dahara di sas                      | C11                | $5 \text{ MHz} \le F_{RF} \le 1.5 \text{ GHz}$            |                   | 18    |                 | -ID   |

| Input Return Loss                          | S11                | $1.5 \text{ GHz} < F_{\text{RF}} \le 3.0 \text{ GHz}$     |                   | 15    |                 | dB    |

|                                            | C22                | 5 MHz $\leq$ F <sub>RF</sub> $\leq$ 1.5 GHz               |                   | 17    |                 | م ا   |

| Output Return Loss                         | S22                | $1.5 \text{ GHz} < F_{\text{RF}} \le 3.0 \text{ GHz}$     |                   | 15    |                 | dB    |

Specification Notes:

Note 1: Items in min/max columns in *bold italics* are Guaranteed by Test.

Note 2: Items in min/max columns that are not bold/italics are Guaranteed by Design Characterization.

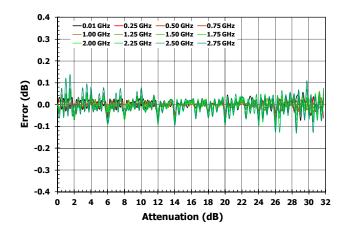

Note 3. The input 0.1dB compression point is used as a linearity figure of merit. The recommended maximum input power is specified as the lesser of the two values from Figure 1 and Figure 2 above.

Note 4: Spurious due to on-chip negative voltage generator. Typical generator fundamental frequency is 2.2 MHz.

Note 5: Minimum time required between switching of attenuations states = 1 / (Maximum Switching Rate).

## RENESAS

## **F1977 SPECIFICATION**

Specifications apply at  $V_{DD}$  = +3.3 V,  $T_{CASE}$  = +25°C,  $F_{RF}$  = 1 GHz, Pin = -10 dBm unless otherwise noted. Serial Mode.  $Z_{RF1} = Z_{RF2} = 75 \Omega$ . EVkit losses are de-embedded unless otherwise noted.

| Parameter                                          | Symbol              | Conditions                                                                | Min | Тур  | Max | Units            |  |

|----------------------------------------------------|---------------------|---------------------------------------------------------------------------|-----|------|-----|------------------|--|

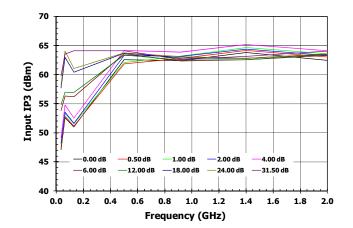

|                                                    |                     | $P_{IN} = +10 \text{ dBm per tone}$<br>50 MHz Tone Separation             |     |      |     |                  |  |

| Input IP3                                          | IIP3                | Attn State = 0.00 dB                                                      |     | 64   |     |                  |  |

|                                                    |                     | Attn State = 15.75 dB                                                     |     | 64   |     | dBm              |  |

|                                                    |                     | Attn State = 31.75 dB                                                     |     | 64   |     |                  |  |

| Input 0.1dB Compression <sup>3</sup>               | P <sub>0.1dB</sub>  | $F_{RF} = 1 \text{ GHz}$<br>Attn = 10 dB<br>Measured in 50 ohms           |     | 32   |     | dBm              |  |

| DCA Cottling Time                                  |                     | Max to Min Attenuation to settle to within 0.5 dB of final value          |     | 0.9  |     |                  |  |

| DSA Settling Time                                  | τ <sub>set</sub>    | Min to Max Attenuation to<br>settle to within 0.5 dB of<br>final value    |     | 1.8  |     | — μs             |  |

| Video Feedthrough<br>RF1, RF2 ports                | VID <sub>FT</sub>   | Measured at RF ports with<br>2.5 ns risetime, 0 to 3.3 V<br>control pulse |     | 10   |     | mV <sub>pp</sub> |  |

| Maximum spurious level on any RF port <sup>4</sup> | Spur <sub>MAX</sub> | Spur Freq ~ 2.2 MHz                                                       |     | -119 |     | dBm              |  |

| Serial Clock Speed                                 | F <sub>CLK</sub>    | SPI 3 wire bus                                                            |     |      | 25  | MHz              |  |

| Parallel to Serial Setup                           | А                   | SPI 3 wire bus                                                            | 100 |      |     | ns               |  |

| Serial Data Hold Time                              | В                   | SPI 3 wire bus                                                            | 10  |      |     | ns               |  |

| LE Delay                                           | С                   | SPI 3 wire bus<br>Time from final serial clock<br>rising edge             | 10  |      |     | ns               |  |

| Maximum Switching Rate <sup>5</sup>                | SW <sub>RATE</sub>  |                                                                           |     | 25   |     | kHz              |  |

Specification Notes:

Note 1: Items in min/max columns in *bold italics* are Guaranteed by Test.

Note 2: Items in min/max columns that are not bold/italics are Guaranteed by Design Characterization.

Note 3. The input 0.1dB compression point is used as a linearity figure of merit. The recommended maximum input power is specified as the lesser of the two values from Figure 1 and Figure 2 above.

Note 4: Spurious due to on-chip negative voltage generator. Typical generator fundamental frequency is 2.2 MHz.

Note 5: Minimum time required between switching of attenuations states = 1 / (Maximum Switching Rate).

## RENESAS

### **PROGRAMMING OPTIONS**

F1977 can be programmed using either the parallel or serial interface; selectable via  $V_{\text{MODE}}$  (pin 3). Serial mode is selected by floating  $V_{\text{MODE}}$  or pulling  $V_{\text{MODE}}$  to a logic high and parallel mode is selected by setting  $V_{\text{MODE}}$  to logic low.

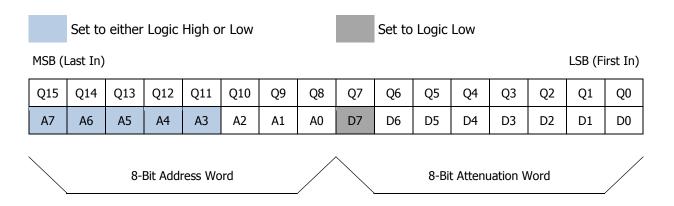

### SERIAL CONTROL MODE

F1977 Serial mode is selected by floating  $V_{\text{MODE}}$  (pin 3) or pulling it to logic high. The serial interface is a 16-bit shift register made up of two words. The first 8-bit word is the Attenuation word, which controls the DSA state. The second word is the address word, which uses only 3 of 8-bits that must match the hard wired A0-A2 programming in order to change the DSA state. If no external connections are made to A0 – A2 then internally they will default to 000 due to internal pull down resistors. If these 3 external preset address bits are not matched with the SPI loaded address bits then the current attenuator state will remain unchanged. This allows up to 8 serial-controlled devices to be used on a single board, which share a common DATA, CLK and LE.

When serial programming is used, all the parallel control input pins 26 - 32 can be left open or grounded. If a pin is grounded than an additional  $25 \ \mu$ A will be drawn from the voltage supply per pin.

### Figure 2 - Two 8-bit words are comprised of 16-bit serial in, parallel out shift register

| A7<br>(MSB) | <b>A6</b> | A5 | A4 | А3 | A2 | A1 | AO | Address<br>Setting |

|-------------|-----------|----|----|----|----|----|----|--------------------|

| Х           | Х         | Х  | Х  | Х  | 0  | 0  | 0  | 000                |

| Х           | Х         | Х  | Х  | Х  | 0  | 0  | 1  | 001                |

| Х           | Х         | Х  | Х  | Х  | 0  | 1  | 0  | 010                |

| Х           | Х         | Х  | Х  | Х  | 0  | 1  | 1  | 011                |

| Х           | Х         | Х  | Х  | Х  | 1  | 0  | 0  | 100                |

| Х           | Х         | Х  | Х  | Х  | 1  | 0  | 1  | 101                |

| Х           | Х         | Х  | Х  | Х  | 1  | 1  | 0  | 110                |

| Х           | Х         | Х  | Х  | Х  | 1  | 1  | 1  | 111                |

### Table 1 - Truth Table for the Serial Address Word

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0<br>(LSB) | Attenuation<br>State<br>(dB) |

|----|----|----|----|----|----|----|-------------|------------------------------|

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0           | 0                            |

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1           | 0.25                         |

| 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0           | 0.5                          |

| 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0           | 1                            |

| 0  | 0  | 0  | 0  | 1  | 0  | 0  | 0           | 2                            |

| 0  | 0  | 0  | 1  | 0  | 0  | 0  | 0           | 4                            |

| 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0           | 8                            |

| 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0           | 16                           |

| 0  | 1  | 1  | 1  | 1  | 1  | 1  | 1           | 31.75                        |

## SERIAL MODE DEFAULT CONDITION

When the device is first powered up it will default to the **Maximum Attenuation** setting as described below: Note that for the F1977 in all cases logic high (1) = Attenuation Stepped IN, while logic Low (0) = Attenuation Stepped OUT.

MSB (Last In)

LSB (First In)

| Q | 215 | Q14 | Q13 | Q12      | Q11     | Q10 | Q9 | Q8 | Q7 | Q6 | Q5    | Q4       | Q3       | Q2   | Q1 | Q0 |

|---|-----|-----|-----|----------|---------|-----|----|----|----|----|-------|----------|----------|------|----|----|

| A | 47  | A6  | A5  | A4       | A3      | A2  | A1 | A0 | D7 | D6 | D5    | D4       | D3       | D2   | D1 | D0 |

|   | Х   | Х   | Х   | Х        | Х       | 0   | 0  | 0  | 0  | 1  | 1     | 1        | 1        | 1    | 1  | 1  |

|   |     |     | 8-  | Bit Addı | ress Wo | ord |    |    |    |    | 8-Bit | t Attenı | iation V | Vord |    |    |

## Figure 3 -Default register settings set for Max Attenuation and 000 Address Word

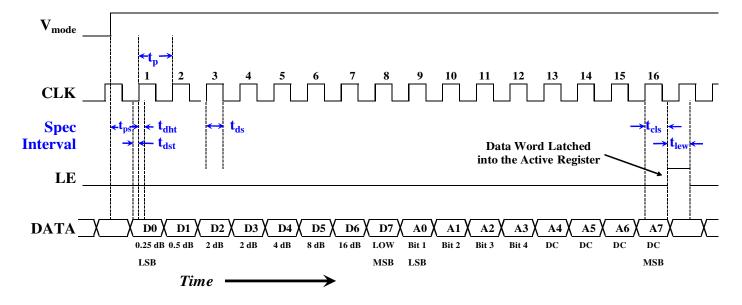

## **REGISTER TIMING DIAGRAM: (NOTE THE TIMING SPEC INTERVALS IN BLUE)**

With serial control, the F1977 can be programmed via the serial port on the rising edge of Latch Enable (LE) which loads the last 8 DATA line bits [formatted LSB (D0) first] resident in the SHIFT register followed by the Address Word into the ACTIVE register.

Figure 4 - Serial Timing Diagram

Note - When Latch Enable (LE) is high, the shift register is disabled and DATA is NOT continuously clocked into the shift register which minimizes noise. It is recommended that Latch enable be left high when the device is not being programmed.

| Interval<br>Symbol | Description                                                                                             | Min<br>Spec | Max<br>Spec | Units |

|--------------------|---------------------------------------------------------------------------------------------------------|-------------|-------------|-------|

| t <sub>ps</sub>    | Parallel to Serial Setup Time - From rising edge<br>of Vmode to rising edge of CLK for D5               | 100         |             | ns    |

| tp                 | Clock high pulse width                                                                                  | 10          |             | ns    |

| t <sub>cls</sub>   | LE Setup Time - From the rising edge of CLK pulse for D0 to LE rising edge minus half the clock period. | 10          |             | ns    |

| t <sub>lew</sub>   | LE pulse width                                                                                          | 30          |             | ns    |

| t <sub>dst</sub>   | Data Setup Time - From the starting edge of Data bit to rising edge of CLK                              | 10          |             | ns    |

| t <sub>dht</sub>   | Data Hold Time - From rising edge of CLK to falling edge of the Data bit.                               | 10          |             | ns    |

| Table 3 · | - Serial | Mode | Timing | Table |

|-----------|----------|------|--------|-------|

|-----------|----------|------|--------|-------|

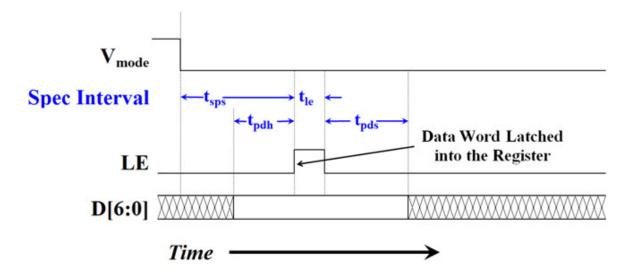

## PARALLEL CONTROL MODE

For the F1977 the user has the option of running in one of two parallel modes. Direct Parallel Mode or Latched Parallel Mode.

### **Direct Parallel Mode:**

Direct Parallel Mode is selected when  $V_{MODE}$  is a logic low and LE is a logic high. In this mode the device will immediately react to any voltage changes to the parallel control pins [pins 26 – 32]. Use direct parallel mode for the fastest settling time.

### **Latched Parallel Mode:**

Latched Parallel Mode is selected when  $V_{\text{MODE}}$  is logic low and LE is toggled from logic low to high. To utilize Latched Parallel Mode:

- Set  $V_{\text{MODE}}$  is logic low.

- Set LE to logic low.

- Adjust pins [26, 27, 28, 29, 30, 31, 32] to the desired attenuation setting. (While LE is set to a logic low, the attenuation state will not change.)

- Pull LE to a logic high. The device will then transition to the attenuation settings reflected by pins D6 D0.

### Latched Parallel Default Startup Condition:

Latched Parallel Mode implies a default state for when the device is first powered up with  $V_{\text{MODE}}$  set for logic low and LE logic low. In this case the default setting is MAXIMUM Attenuation.

| D6 | D5 | D4 | D3 | D2 | D1 | D0 | Attenuation<br>(dB) |  |  |  |

|----|----|----|----|----|----|----|---------------------|--|--|--|

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0                   |  |  |  |

| 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0.25                |  |  |  |

| 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0.5                 |  |  |  |

| 0  | 0  | 0  | 0  | 1  | 0  | 0  | 1                   |  |  |  |

| 0  | 0  | 0  | 1  | 0  | 0  | 0  | 2                   |  |  |  |

| 0  | 0  | 1  | 0  | 0  | 0  | 0  | 4                   |  |  |  |

| 0  | 1  | 0  | 0  | 0  | 0  | 0  | 8                   |  |  |  |

| 1  | 0  | 0  | 0  | 0  | 0  | 0  | 16                  |  |  |  |

| 1  | 1  | 1  | 1  | 1  | 1  | 1  | 31.75               |  |  |  |

Table 4 - Truth Table for the Parallel Control Word

| Interval<br>Symbol | Description                            |     | Max<br>Spec | Units |

|--------------------|----------------------------------------|-----|-------------|-------|

| t <sub>sps</sub>   | Serial to Parallel Mode Setup Time     | 100 |             | ns    |

| t <sub>pdh</sub>   | Parallel Data Hold Time                | 10  |             | ns    |

| t <sub>le</sub>    | t <sub>le</sub> LE minimum pulse width |     |             | ns    |

| t <sub>pds</sub>   | Parallel Data Setup Time               | 10  |             | ns    |

## Table 5 - Latched Parallel Mode Timing

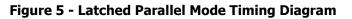

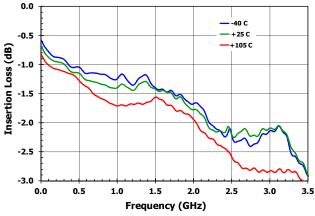

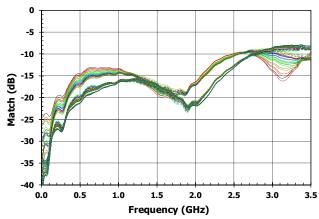

## TYPICAL OPERATING CONDITIONS (TOC)

Unless otherwise noted for the TOC graphs on the following pages, the following conditions apply.

- V<sub>DD</sub> = +3.30 V

- T<sub>CASE</sub> = +25 °C

- P<sub>IN</sub> = 0 dBm for single tone measurements

- P<sub>IN</sub> = +15 dBm/tone for multi-tone measurements

- 50 MHz Tone Space

- Serial Control

- RF1 Port is the input port

- Attenuation Setting = 0 dB

- Measured in a 75 ohm system

- EVKit losses (traces and connectors) are fully de-embedded

## TYPICAL OPERATING CONDITIONS (-1-)

### **Insertion Loss vs Frequency**

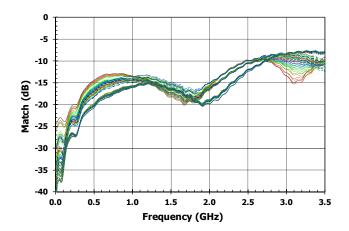

**RF1 Return Loss vs Frequency [All States]**

RF2 Return Loss vs Frequency [All States]

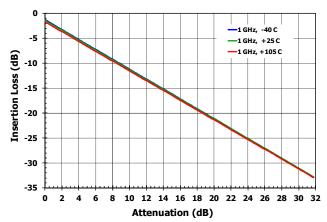

#### **Insertion Loss vs Attenuation State**

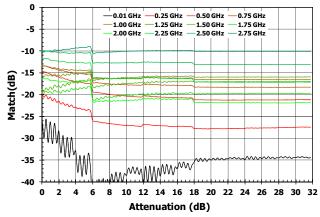

**RF1 Return Loss vs Attenuation State**

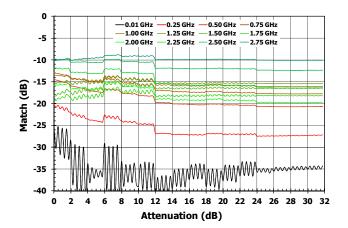

**RF2 Return Loss vs Attenuation State**

## **TYPICAL OPERATING CONDITIONS (-2-)**

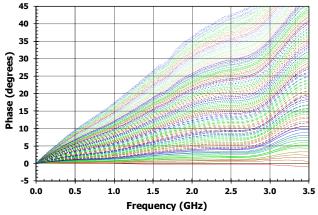

#### **Relative Insertion Phase vs Frequency**

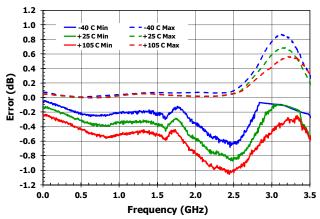

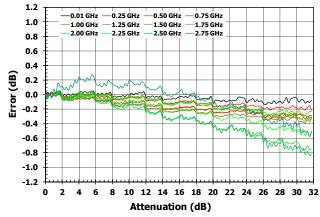

Worst Case Absolute Accuracy vs Frequency

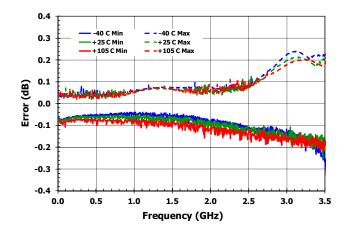

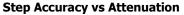

Worst Case Step Accuracy vs Frequency

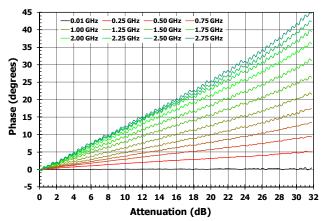

#### **Relative Insertion Phase vs Attenuation**

**Absolute Accuracy vs Attenuation**

**Input Compression at 50 MHz**

## TYPICAL OPERATING CONDITIONS (-3-)

#### 0.5 0.4 0.00 dB -1.00 dB 0.3 -2.00 dB 4.00 dB Compression (dB) 0.2 0.1 0.0 -0.1 -0.2 -0.3 -0.4 l in a 50 -0.5 16 18 20 22 24 26 28 30 32 34 Input Power (dBm)

#### **Input Compression 1.0 GHz**

**Input Compression 2.0 GHz**

#### **Input Compression 500 MHz**

**Input Compression 1.5 GHz**

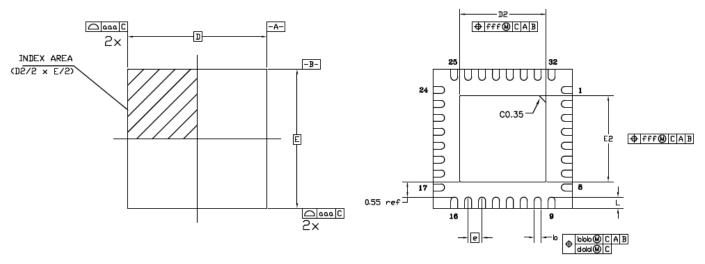

## **PACKAGE DRAWING**

(5 mm x 5 mm 32-pin TQFN), Use Exposed PAD (EPAD) Option P1

TOP VIEW

BOTTOM VIEW

SIDE VIEW

A1

SEAT ING

-C-

| SYMBOL | DIMENSION |         |      |  |

|--------|-----------|---------|------|--|

| 2      | MIN       | NOM     | MAX  |  |

| L      | 0.30      | 0.40    | 0.50 |  |

| D      | 5         | .00 BSC |      |  |

| E      | 5.00 BSC  |         |      |  |

| е      | 0.50 BSC  |         |      |  |

| А      | 0.70      | 0.75    | 0.80 |  |

| A1     | 0.00      | 0.02    | 0.05 |  |

| b      | .20       | .25     | .30  |  |

| aaa    | 0.10      |         |      |  |

| bbb    | 0.10      |         |      |  |

| CCC    | 0.10      |         |      |  |

| ddd    | 0.05      |         |      |  |

| eee    | 0.08      |         |      |  |

| fff    | 0.10      |         |      |  |

| FPAD | OPTION |  |

|------|--------|--|

⊂ eee C

// ccc C

| SYMBOL | P1   |      |      |  |

|--------|------|------|------|--|

| STMDUL | MIN  | NOM  | MAX  |  |

| E2     | 3.00 | 3.10 | 3.20 |  |

| D2     | 3.00 | 3.10 | 3.20 |  |

NOTES:

1. ALL DIMENSIONING AND TOLERANCING CONFORM TO ANSI Y14.5M-1982 2. ALL DIMENSIONS ARE IN MILLIMETERS.

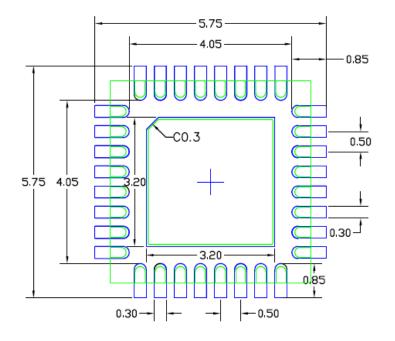

## LAND PATTERN DIMENSION

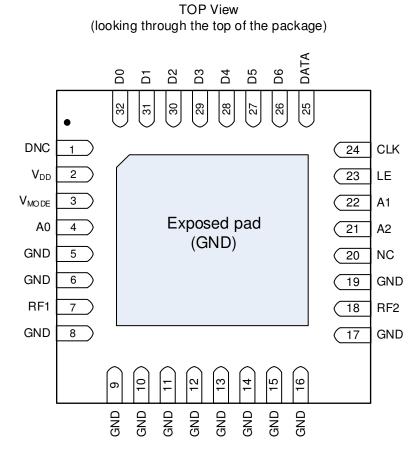

### **PIN DIAGRAM**

Rev 1, 04/21/2016

### **PIN DESCRIPTION**

| Pin    | Pin Name Function              |                                                                                                                       |  |

|--------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------|--|

| 1      | DNC                            | This pin must be left open.                                                                                           |  |

| 2      | V <sub>DD</sub>                | Main Supply. Use 3.3 V or 5 V. Bypass capacitor as close to pin as possible.                                          |  |

| 3      | V <sub>MODE</sub> <sup>1</sup> | Logic low for parallel mode. Logic high or NC for serial mode.                                                        |  |

| 4      | A0 <sup>2</sup>                | Address bit A0 connection.                                                                                            |  |

| 5      | GND                            | Connect directly to paddle ground or as close as possible to pin with thru via. This pin is not internally connected. |  |

| 6      | GND                            | Connect directly to paddle ground or as close as possible to pin with thru via.                                       |  |

| 7      | RF1 <sup>3</sup>               | Device RF input or output (bi-directional).                                                                           |  |

| 8 - 17 | GND                            | Connect each pin directly to paddle ground or as close as possible to pin with thru vias.                             |  |

| 18     | RF2 <sup>3</sup>               | Device RF input or output (bi-directional).                                                                           |  |

| 19     | GND                            | Connect directly to paddle ground or as close as possible to pin with thru via.                                       |  |

| 20     | NC                             | No internal connection. These pins can be left unconnected, voltage applied, or connected to ground (recommended).    |  |

| 21     | A2 <sup>2</sup>                | Address bit A2 connection                                                                                             |  |

| 22     | A1 <sup>2</sup>                | Address bit A1 connection.                                                                                            |  |

| 23     | LE1                            | Serial interface latch enable input.                                                                                  |  |

| 24     | CLK <sup>1</sup>               | Serial interface clock input.                                                                                         |  |

| 25     | DATA <sup>1</sup>              | Serial interface data input.                                                                                          |  |

| 26     | D6 <sup>1</sup>                | Parallel control bit, 16 dB.                                                                                          |  |

| 27     | D5 <sup>1</sup>                | Parallel control bit, 8 dB.                                                                                           |  |

| 28     | $D4^1$                         | Parallel control bit, 4 dB.                                                                                           |  |

| 29     | D3 <sup>1</sup>                | Parallel control bit, 2 dB.                                                                                           |  |

| 30     | D2 <sup>1</sup>                | Parallel control bit, 1 dB.                                                                                           |  |

| 31     | D1 <sup>1</sup>                | Parallel control bit, 0.5 dB.                                                                                         |  |

| 32     | D0 <sup>1</sup>                | Parallel control bit, 0.25 dB.                                                                                        |  |

| EP     | Exposed<br>Paddle              | Connect to Ground with multiple vias for good thermal and RF performance.                                             |  |

Pin Description Notes:

Note 1: Includes an internal 100 kΩ pullup resistor to an internal regulated 2.5V supply. If pin is grounded then there is an additional 25 µA per pin for the supply current. Includes an internal 100 k $\Omega$  pull-down resistor to GND.

Note 2:

Note 3: RF pins 7 and 18 do not require DC blocking capacitors for operation if they are at 0 V DC. If they are not at 0V DC, then they require DC blocking capacitors.

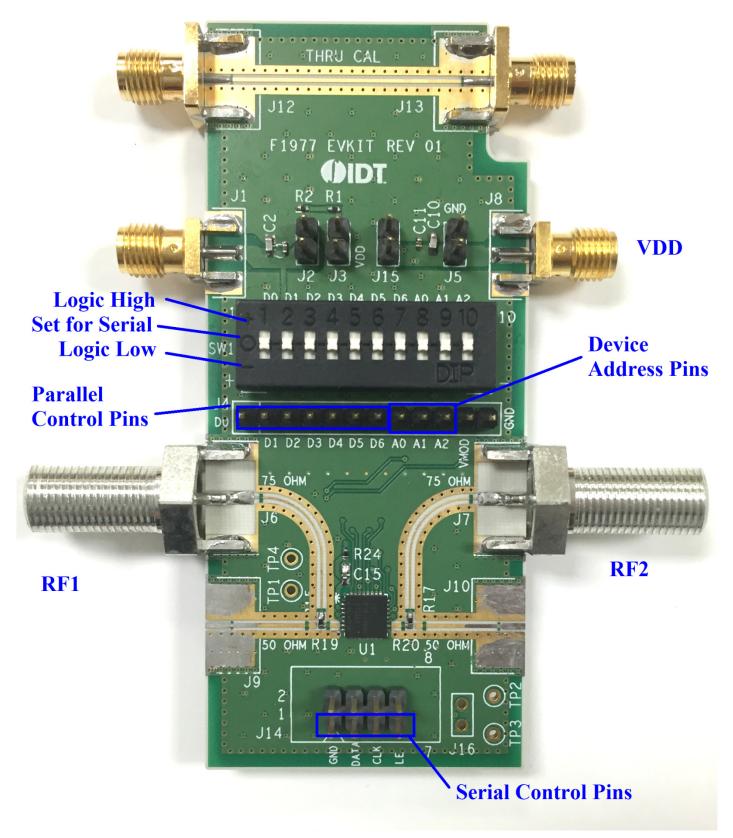

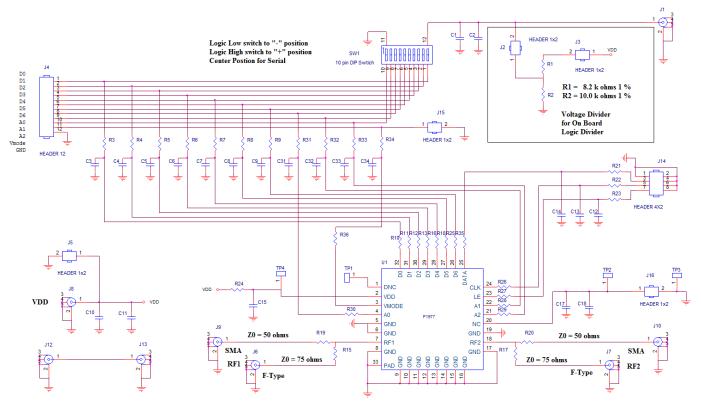

## **EVKIT PICTURE**

## **EVKIT / APPLICATIONS CIRCUIT**

## **EVKIT BOM**

| Item # | Part Reference                               | QTY | DESCRIPTION                                         | Mfr. Part #        | Mfr.            |

|--------|----------------------------------------------|-----|-----------------------------------------------------|--------------------|-----------------|

| 1      | C1, C11, C15                                 | 3   | 100 nF ±10%, 16 V, X7R Ceramic Capacitor<br>(0402)  | GRM155R71C104K     | MURATA          |

| 2      | C2, C10                                      | 2   | 10 nF ±5%, 50 V, X7R Ceramic Capacitor (0603)       | GRM188R71H103J     | MURATA          |

| 3      | C3 - C9, C12, C13,<br>C14, C31 - C34         | 14  | 100 pF ±5%, 50 V, C0G Ceramic Capacitor<br>(0402)   | GRM1555C1H101J     | MURATA          |

| 4      | R3 - R9,<br>R31 - R34                        | 11  | 100 $\Omega$ ±1%, 1/10W, Resistor (0402)            | ERJ-2RKF1000X      | PANASONIC       |

| 5      | R10-R13,<br>R15-R18,<br>R24-R30,<br>R35, R36 | 17  | 0 Ω Resistors (0402)                                | ERJ-2GE0R00X       | PANASONIC       |

| 6      | R21, R22, R23                                | 3   | 3 kΩ ±1%, 1/10W, Resistor (0402)                    | ERJ-2RKF3001X      | PANASONIC       |

| 7      | R1                                           | 1   | 8.2 kΩ ±1%, 1/10W, Resistor (0402)                  | ERJ-2RKF8201X      | PANASONIC       |

| 8      | R2                                           | 1   | 10 kΩ ±1%, 1/10W, Resistor (0402)                   | ERJ-2RKF1002X      | PANASONIC       |

| 9      | J2, J3, J5                                   | 3   | CONN HEADER VERT SGL 2 X 1 POS GOLD                 | 961102-6404-AR     | 3M              |

| 10     | J14, J15                                     | 1   | CONN HEADER VERT DBL 4 X 2 POS GOLD                 | 67997-108HLF       | FCI             |

| 11     | ]4                                           | 1   | CONN HEADER VERT SGL 12 X 1 POS GOLD                | 961112-6404-AR     | 3M              |

| 12     | J1, J8                                       | 2   | Edge Launch SMA<br>(0.250 inch pitch ground, round) | 142-0711-821       | Emerson Johnson |

| 13     | J6, J7                                       | 2   | Edge Launch F TYPE 75 ohm SMA                       | 222181             | Amphenol        |

| 14     | U2                                           | 1   | SWITCH 10 POSITION DIP SWITCH                       | KAT1110E           | E-Switch        |

| 15     | U1                                           | 1   | DSA                                                 | F1977NCGI          | IDT             |

| 16     |                                              | 1   | Printed Circuit Board                               | F1977 Evkit Rev 01 | IDT             |

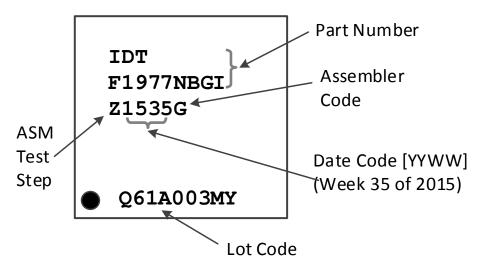

## **TOP MARKINGS**

## **APPLICATIONS INFORMATION**

### **Power Supplies**

A common VCC power supply should be used for all pins requiring DC power. All supply pins should be bypassed with external capacitors to minimize noise and fast transients. Supply noise can degrade noise figure and fast transients can trigger ESD clamps and cause them to fail. Supply voltage change or transients should have a slew rate smaller than 1 V / 20  $\mu$ S. In addition, all control pins should remain at 0 V (+/-0.3 V) while the supply voltage ramps or while it returns to zero.

### **Digital Pin Voltage & Resistance Values**

The following table provides open-circuit DC voltage referenced to ground and resistance values for each of the control pins listed.

| Pin        | Name              | Open Circuit<br>DC Voltage | Internal<br>Connection                                       |

|------------|-------------------|----------------------------|--------------------------------------------------------------|

| 3          | V <sub>MODE</sub> | 2.5 V                      | 100 k $\Omega$ pullup resistor to internally regulated 2.5 V |

| 4, 21, 22  | A0, A2, A1        | 0 V                        | 100 k $\Omega$ resistor to GND                               |

| 23, 24, 25 | LE, CLK, DATA     | 2.5 V                      | 100 k $\Omega$ pullup resistor to internally regulated 2.5 V |

| 26-32      | D[6:0]            | 2.5 V                      | 100 k $\Omega$ pullup resistor to internally regulated 2.5 V |

## **REVISION HISTORY SHEET**

| Rev | Date        | Page | Description of Change                                                          |

|-----|-------------|------|--------------------------------------------------------------------------------|

| 0   | 2016-Feb-19 |      | Initial Release                                                                |

| 1   | 2016-Apr-21 | 2    | Typo on $V_{HBM}$ rating. Voltage changed from 1.5kV to 1kV. No chng. to Class |

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only for development of an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use o any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.0 Mar 2020)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners. **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit: <u>www.renesas.com/contact/</u>