# 1.8 V PLL 1:10 Differential SDRAM **Clock Driver**

# MPC96877

## **Recommended Applications**

- **DDR II Memory Modules**

- Zero Delay Board fan-out

# Features

- 1.8 V Phase Lock Loop Clock Driver for (DDR II) Applications •

- Spread Spectrum Clock Compatible

- Operating Frequency: 100 MHz to 340 MHz

- 1 to 10 differential clock distribution (SSTL 18)

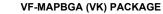

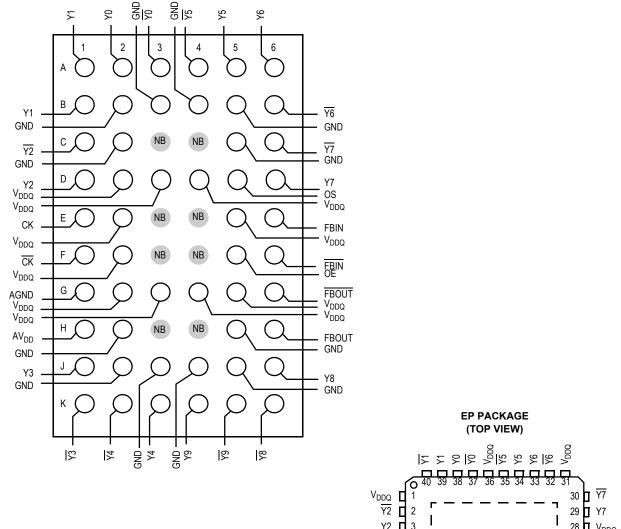

- 52-Ball VF-BGA (FP-MAPBGA 0.65-mm pitch) and 40-Pin MLF (QFN)

- 52-lead Pb-free Package Available

- External Feedback Pins (FBIN, FBIN) are used to synchronize the Outputs to the Input Clocks

- Single-Ended Input and Single-Ended Output Modes

- Meets or Exceeds JESD82-8 PLL Standard for PC2-3200/4300

- Auto Power Down detect logic

# **Switching Characteristics**

- Cycle-to-Cycle Jitter (>165 Mhz): 40 ps max.

- Output-to-Output Skew: 40 ps max.

# **Functional Description**

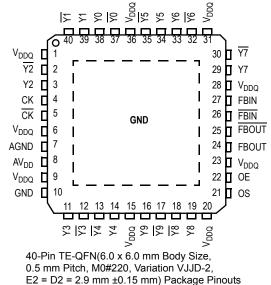

The MPC96877 is a high-performance, low-jitter, low-skew, zero-delay buffer that distributes a differential clock input pair (CK, CK) to ten differential pairs of clock outputs (Yn, Yn) and to one differential pair of feedback clock outputs (FBOUT, FBOUT). The clock outputs are controlled by the input clocks (CK. CK), the feedback clocks (FBIN, FBIN), the LVCMOS control pins (OE, OS),

and the analog power input (AV<sub>DD</sub>). When OE is low, the clock outputs, except

FBOUT/FBOUT, are disabled while the internal PLL continues to maintain its locked-in frequency. OS (output select) is a program pin that must be tied to GND or VDD. When OS is high, OE functions as previously described. When OS and OE are both low, OE has no affect on Y7/Y7, they are free running. When AV<sub>DD</sub> is grounded, the PLL is turned off and bypassed for test purposes. When both clock inputs (CK, CK) are logic low, the device enters in a low power mode. An input logic detection circuit on the differential inputs, independent from input buffers, detects the logic low level and performs in a low power state where all outputs, the feedback, and the PLL are off. When the clock inputs transition from being logic low to being differential signals, the PLL turns back on, the inputs and the outputs are enabled, and the PLL obtains phase lock between the feedback clock pair (FBIN, FBIN) and the clock input pair (CK, CK) within the specified stabilization time.

The MPC96877 is able to track spread spectrum clocking (SSC) for reduced EMI. This device operates from 0°C to 70°C.

#### **AVAILABLE ORDERING OPTIONS**

| Τ <sub>Α</sub> | 52-Ball BGA             | 40-Pin QFN              |

|----------------|-------------------------|-------------------------|

| 0°C to 70°C    | MPC96877VK<br>(Pb-Free) | MPC96877EP<br>(Pb-Free) |

Figure 1. MPC96877 Logic Diagram

# Table 1. Pin Configuration

| Pin              | BGA                                               | MLF                                         | I/O    | Function                                                         |

|------------------|---------------------------------------------------|---------------------------------------------|--------|------------------------------------------------------------------|

| AGND             | G1                                                | 7                                           |        | Analog ground                                                    |

| AV <sub>DD</sub> | H1                                                | 8                                           |        | Analog power                                                     |

| СК               | E1                                                | 4                                           | Input  | Clock input with a (10k to 100k) pulldown resistor               |

| СК               | E6                                                | 5                                           | Input  | Complimentary clock input with a (10k to 100k) pulldown resistor |

| FBIN             | F6                                                | 27                                          | Input  | Feedback clock input                                             |

| FBIN             |                                                   | 26                                          | Input  | Complimentary Feedback clock input                               |

| FBOUT            | H6                                                | 24                                          | Output | Feedback clock output                                            |

| FBOUT            | G6                                                | 25                                          | Output | Complimentary feeback clock output                               |

| OE               | F5                                                | 22                                          | Input  | Output Enable (asynchronous)                                     |

| OS               | D5                                                | 21                                          | Input  | Output Select (tied to GND or V <sub>DD</sub> )                  |

| GND              | B2, B3, B4, B5,<br>C2,C5,H2,H5,<br>J2, J3, J4, J5 | 10                                          |        | Ground                                                           |

| V <sub>DDQ</sub> | D2, D3, D4, E2, E5,<br>F2, G2, G3, G4, G5         | 1, 6, 9, 15, 20,<br>23, 28, 31, 36          |        | Logic and output power                                           |

| Y[0:9]           | A2, A1, D1, J1, K3,<br>A5, A6, D6, J6, K4         | 38, 39, 3, 11, 14,<br>34, 33, 29,19, 16     | Output | Clock outputs                                                    |

| Y[0:9]           | A3, B1, C1, K1, K2,<br>A4, B6, C6, K6, K5         | 37, 40, 2, 12, 13,<br>35, 32, 30, 18,<br>17 | Output | Complimentary clock outputs                                      |

## Table 2. Function Table

|                  | Inputs |    |    |    |                                          | Outputs                                  |                             | DI I                        |                |  |

|------------------|--------|----|----|----|------------------------------------------|------------------------------------------|-----------------------------|-----------------------------|----------------|--|

| AV <sub>DD</sub> | OE     | OS | СК | СК | Y                                        | Y                                        | FBOUT                       | FBOUT                       | PLL            |  |

| GND              | Н      | Х  | L  | Н  | L                                        | н                                        | L                           | Н                           | Bypassed / OFF |  |

| GND              | Н      | Х  | Н  | L  | Н                                        | L                                        | Н                           | L                           | Bypassed / OFF |  |

| GND              | L      | Н  | L  | Н  | LZ                                       | LZ                                       | L                           | Н                           | Bypassed / OFF |  |

| GND              | L      | L  | Н  | L  | L <sub>Z</sub> <sup>1</sup><br>Y7 Active | L <sub>Z</sub> <sup>1</sup><br>Y7 Active | Н                           | L                           | Bypassed / OFF |  |

| 1.8 V Nominal    | L      | Н  | L  | Н  | L <sub>Z</sub> <sup>1</sup>              | L <sub>Z</sub> <sup>1</sup>              | L                           | Н                           | ON             |  |

| 1.8 V Nominal    | L      | L  | Н  | L  | L <sub>Z</sub> <sup>1</sup><br>Y7 Active | L <sub>Z</sub> <sup>1</sup><br>Y7 Active | Н                           | L                           | ON             |  |

| 1.8 V Nominal    | Н      | Х  | L  | Н  | L                                        | Н                                        | L                           | Н                           | ON             |  |

| 1.8 V Nominal    | Н      | Х  | Н  | L  | Н                                        | L                                        | Н                           | L                           | ON             |  |

| 1.8 V Nominal    | Х      | Х  | L  | L  | L <sub>Z</sub> <sup>1</sup>              | L <sub>Z</sub> <sup>1</sup>              | L <sub>Z</sub> <sup>1</sup> | L <sub>Z</sub> <sup>1</sup> | OFF            |  |

| Х                | Х      | Х  | Н  | Н  |                                          | RESERVED                                 |                             |                             |                |  |

1.  $L_{(Z)}$  means the outputs are disabled to a low state meeting the  $I_{ODL}$  limit in Table 5.

#### Table 3. Absolute Maximum Ratings Over Free-Air Operating Range<sup>1</sup>

| Parameter                                                                                 | Value                              |

|-------------------------------------------------------------------------------------------|------------------------------------|

| Supply voltage range, $V_{DDQ}$ or $AV_{DD}$                                              | –0.5 V to 2.5 V                    |

| Input voltage range, VI <sup>2, 3</sup>                                                   | –0.5 V to V <sub>DDQ</sub> + 0.5 V |

| Output voltage range, V <sub>O</sub> <sup>1, 2</sup>                                      | –0.5 V to V <sub>DDQ</sub> + 0.5 V |

| Input clamp current, $I_{IK}$ (V <sub>I</sub> < 0 or V <sub>I</sub> > V <sub>DDQ</sub> )  | ±50 mA                             |

| Output clamp voltage, $I_{OK}$ (V <sub>O</sub> < 0 or V <sub>O</sub> > V <sub>DDQ</sub> ) | ±50 mA                             |

| Continuous output current, IO ( $V_O = 0$ to $V_{DDQ}$ )                                  | ±50 mA                             |

| Continuous current through each V <sub>DDQ</sub> or GND                                   | ±100 mA                            |

| Storage temperature range, T <sub>STG</sub>                                               | –65°C to 150°C                     |

1. Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

2. The input and output voltage ratings may be exceeded if the input and output clamp-current ratings are observed.

3. This value is limited to 2.5 V maximum.

#### **Table 4. Recommended Operating Conditions**

| Rating                                       | Parameter        | Affected Pins  | Min                         | Nom              | Max                         | Unit |

|----------------------------------------------|------------------|----------------|-----------------------------|------------------|-----------------------------|------|

| Output supply voltage                        | V <sub>DDQ</sub> |                | 1.7                         | 1.8              | 1.9                         | V    |

| Supply voltage <sup>1</sup>                  | AV <sub>DD</sub> |                |                             | V <sub>DDQ</sub> |                             |      |

| Low-level input voltage <sup>2</sup>         | V <sub>IL</sub>  | OE, OS, CK, CK |                             |                  | 0.35 x V <sub>DDQ</sub>     | V    |

| High-level input voltage <sup>2</sup>        | V <sub>IH</sub>  | OE, OS, CK, CK | 0.65 x V <sub>DDQ</sub>     |                  |                             |      |

| High-level output current                    | I <sub>ОН</sub>  |                |                             |                  | -9                          | mA   |

| Low-level output current                     | I <sub>OL</sub>  |                |                             |                  | 9                           | mA   |

| Input differential-pair cross voltage        | V <sub>IX</sub>  |                | (V <sub>DDQ</sub> /2) -0.15 |                  | (V <sub>DDQ</sub> /2) +0.15 | V    |

| Input voltage level                          | V <sub>IN</sub>  |                | -0.3                        |                  | V <sub>DDQ</sub> +0.3       |      |

| Input differential-pair voltage <sup>2</sup> | V <sub>ID</sub>  | DC             | 0.3                         |                  | V <sub>DDQ</sub> +0.4       |      |

| (see Figure 9. Half-Period Jitter)           |                  | AC             | 0.6                         |                  | V <sub>DDQ</sub> +0.4       |      |

| Operating free-air temperature               |                  |                | 0                           |                  | 70                          | °C   |

1. The PLL is turned off and bypassed for test purposes when AV<sub>DD</sub> is grounded. During this test mode, V<sub>DDQ</sub> remains within the recommended operating conditions and not timing parameters are guaranteed.

2. V<sub>ID</sub> is the magnitude of the difference between the input level on CK and the input level on CK, see Figure 12. Time Delay between OE and Clock Output for definition. For CK and CK the V<sub>IH</sub> and V<sub>IL</sub> limits are used to define the DC low and high levels for the logic detect state.

| Description                                                                                      | Parameter         | Affected Pins      | Test Conditions                                             | $AV_{DD}, V_{DDQ}$ | Min                   | Max   | Unit |

|--------------------------------------------------------------------------------------------------|-------------------|--------------------|-------------------------------------------------------------|--------------------|-----------------------|-------|------|

| All inputs                                                                                       | V <sub>IK</sub>   |                    | I <sub>I</sub> = -18mA                                      | 1.7 V              |                       | -1.2  | V    |

| High output voltage                                                                              | V <sub>OH</sub>   |                    | I <sub>OH</sub> = –100 μA                                   | 1.7 to 1.9 V       | V <sub>DDQ</sub> -0.2 |       | V    |

|                                                                                                  |                   |                    | I <sub>OH</sub> = –9 mA                                     | 1.7 V              | 1.1                   |       |      |

| Low output voltage                                                                               | V <sub>OL</sub>   |                    | I <sub>OL</sub> = 100 μA                                    | 1.7 to 1.9 V       |                       | 0.1   | V    |

|                                                                                                  |                   |                    | I <sub>OL</sub> = 9 mA                                      | 1.7 V              |                       | 0.6   |      |

| Output disable current                                                                           | I <sub>ODL</sub>  |                    | OE = L, V <sub>ODL</sub> = 100 mV                           | 1.7 V              | 100                   |       | μΑ   |

| Output differential voltage                                                                      | V <sub>OD</sub>   |                    |                                                             | 1.7 V              | 0.5                   |       | V    |

| Input leakage current                                                                            | lı                | СК, <u>СК</u>      | $V_{I} = V_{DDQ}$ or GND                                    | 1.9 V              |                       | ± 250 | μΑ   |

|                                                                                                  |                   | OE, OS, FBIN, FBIN | $V_{I} = V_{DDQ}$ or GND                                    | 1.9 V              |                       | ± 10  |      |

| Static supply current I <sub>DDQ</sub> + I <sub>ADD</sub>                                        | I <sub>DDLD</sub> |                    | CK and $\overline{CK} = L$                                  | 1.9 V              |                       | 500   | μΑ   |

| Dynamic Supply current<br>I <sub>DDQ</sub> + I <sub>ADD,</sub> see Note 1 for CPD<br>calculation | I <sub>DD</sub>   |                    | CK and $\overline{\text{CK}}$ = 270 MHz<br>all outputs open | 1.9 V              |                       | 300   | mA   |

#### Table 5. Electrical Characteristics Over Recommended Free-Air Operating Temperature Range

1. Total  $I_{DD} = I_{DDQ} + I_{ADD} = F_{CK} * C_{PD} * V_{DDQ}$ , solving for  $C_{PD} = (I_{DDQ} + I_{ADD})/(F_{CK} * V_{DDQ})$  where  $F_{CK}$  is the input Frequency,  $V_{DDQ}$  is the power supply and  $C_{PD}$  is the Power Dissipation Capacitance.

#### Table 6. Timing Requirements Over Recommended Free-Air Operating Temperature Range

| Timing Requirements                         | AV <sub>DD</sub> , V <sub>DDQ</sub> = | Unit |      |  |

|---------------------------------------------|---------------------------------------|------|------|--|

|                                             | Min                                   | Мах  | onit |  |

| Operating clock frequency <sup>1, 2</sup>   | 125                                   | 340  | MHz  |  |

| Application clock frequency <sup>1, 3</sup> | 160                                   | 340  | MHz  |  |

| Input clock duty cycle                      | 40                                    | 60   | %    |  |

| Stabilization time <sup>4</sup>             |                                       | 15   | μS   |  |

1. The PLL must be able to handle spread spectrum induced skew.

2. Operating clock frequency indicates a range over which the PLL must be able to lock, but in which it is not required to meet the other timing parameters. (Used for low speed system debug.)

3. Application clock frequency indicates a range over which the PLL must meet all timing parameters.

4. Stabilization time is the time required for the integrated PLL circuit to obtain phase lock of its feedback signal to its reference signal after power up. During normal operation, the stabilization time is also the time required for the integrated PLL circuit to obtain phase lock of its feedback signal to its reference signal when CK and CK go to a logic low state, enter the power-down mode and later return to active operation. CK and CK may be left floating after they have been driven low for one complete clock cycle.

| Table 7. Switching Characteristics over Recommended Free-Air Operating Temperature Range Unless Otherwise Note | эd |

|----------------------------------------------------------------------------------------------------------------|----|

| (see Notes)                                                                                                    |    |

| Description                                   | Parameter       | Diagram                      | AV <sub>DD,</sub> V         | ± 0.1 V | 1114                        |      |

|-----------------------------------------------|-----------------|------------------------------|-----------------------------|---------|-----------------------------|------|

| Description                                   |                 |                              | Min                         | Nom     | Max                         | Unit |

| OE to any Y/Y                                 | ten             | see Figure 11                |                             |         | 8                           | ns   |

| OE to any $Y/\overline{Y}$                    | tdis            | see Figure 11                |                             |         | 8                           | ns   |

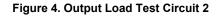

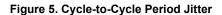

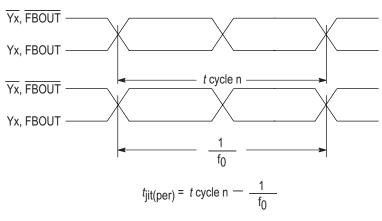

| Cycle-to-Cycle period jitter                  | tjit(cc+)       | see Figure 4                 | 0                           |         | 40                          | ps   |

|                                               | tjit(cc-)       |                              | 0                           |         | -40                         | ps   |

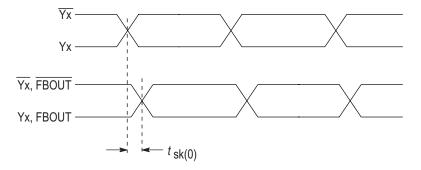

| Static phase offset                           | t(φ)            | see Figure 5                 | -50                         |         | 50                          | ps   |

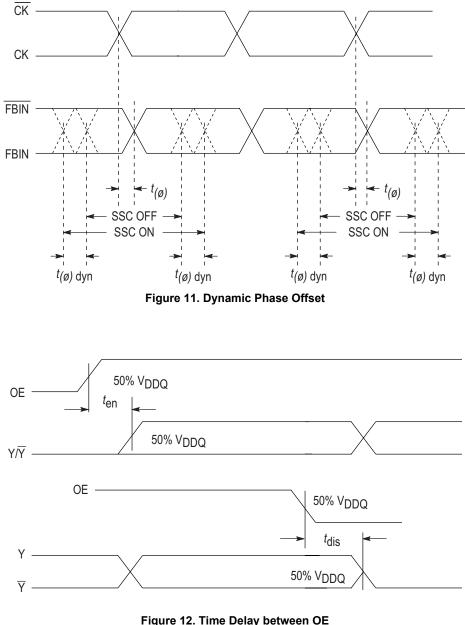

| Dynamic phase offset                          | t(φ)dyn         | see Figure 10                | -50                         |         | 50                          | ps   |

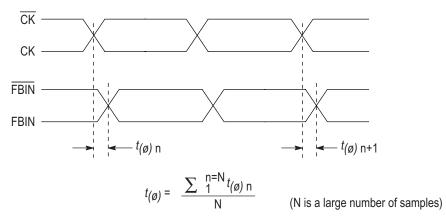

| Output clock skew                             | tsk(o)          | see Figure 6                 |                             |         | 40                          | ps   |

| Period Jitter                                 | tjit(per)       | see Figure 7                 | -40                         |         | 40                          | ps   |

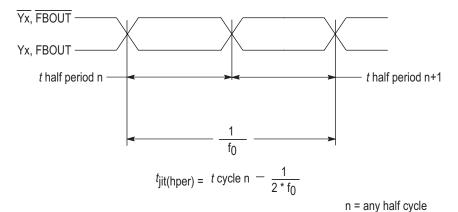

| Half -period jitter                           | tjit(hper)      | see Figure 8                 | -75                         |         | 75                          | ps   |

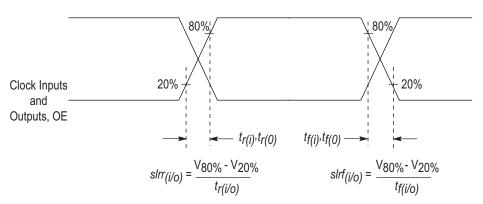

| Output Enable                                 | slr(i)          | see Figure 3<br>and Figure 9 | 0.5                         |         |                             | V/ns |

| Input clock slew rate, measured single ended  |                 |                              | 1                           | 2.5     | 4                           |      |

| Output clock slew rate, measured single ended | slr(o)          | see Figure 3<br>and Figure 9 | 1.5                         | 2.5     | 3                           | V/ns |

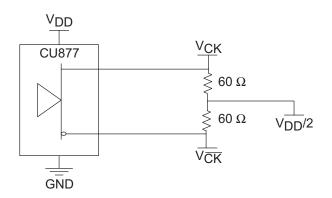

| Output differential-pair cross voltage        | V <sub>OX</sub> | see Figure 2                 | (V <sub>DDQ</sub> /2) – 0.1 |         | (V <sub>DDQ</sub> /2) + 0.1 | V    |

| SSC modulation frequency                      |                 |                              | 30                          |         | 33                          | kHz  |

| SSC clock input frequency deviation           |                 |                              | 0.0                         |         | -0.5                        |      |

| PLL Loop bandwidth (–3dB from unity gain)     |                 |                              | 2.0                         |         |                             | MHz  |

NOTES:

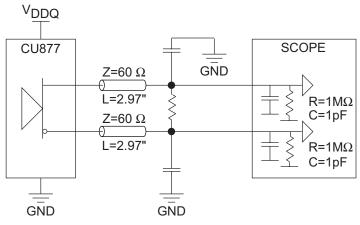

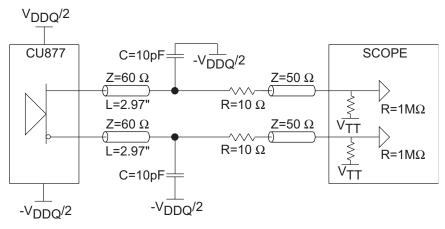

1. There are two different terminations that are used with the following tests. The loadboard in Figure 2. IBIS Model Output Load is used to measure the input and output differential-pair cross voltage only. The loadboard in Figure 3. Output Load Test Circuit 1 is used to measure all other tests. For consistency, equal length cables must be used.

2. Static Phase offset does not include Jitter.

3. Period Jitter and Half-Period Jitter specifications are separate specifications that must be met independently of each other.

4. The Output Slew Rate is determined form the IBIS model into the load shown in Figure 4. Output Load Test Circuit 2. It is measured single ended.

5. To eliminate the impact of input slew rates on static phase offset, the input slew rates of Reference Clock Input CK, CK and Feedback Clock Input FBIN, FBIN are recommended to be nearly equal. The 2.5 V/ns slew rates are shown as a recommended target. Compliance with these Nom values is not mandatory if it can be adequately demonstrated that alternative characteristics meet the requirements of the registered DDR2 DIMM application.

# TEST CIRCUIT AND SWITCHING WAVEFORMS

Figure 3. Output Load Test Circuit 1

Note: V<sub>TT</sub> = GND

tjit(cc) = t cycle n - t cycle n+1

Figure 6. Static Phase Offset

# TEST CIRCUIT AND SWITCHING WAVEFORMS (Continued)

# TEST CIRCUIT AND SWITCHING WAVEFORMS (Continued)

Figure 12. Time Delay between OE and Clock Output

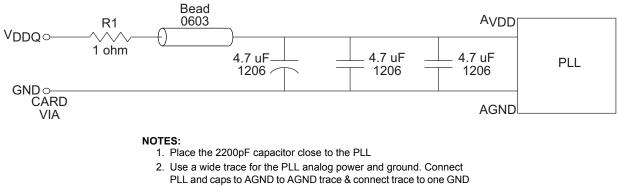

# RECOMMENDED FILTERING FOR THE ANALOG POWER SUPPLY (AV<sub>DD</sub>)

via (farthest from PLL).

3. Recommended bead: Fair Rite P/N 2506036017Y0 or equivalent (0.8 Ohm DC max, 600 Ohms @ 100 MHz)

Figure 13. AV<sub>DD</sub> Filtering

# IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only for development of an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use o any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.0 Mar 2020)

## **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners. **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit: <u>www.renesas.com/contact/</u>