## Li-lon linear battery charger with LDO, load switches and reset generator

### Maturity status link

STBC02

### **Features**

- Charges single-cell Li-Ion batteries with CC/CV algorithm and charge termination

- Fast charge current up to 450 mA

- Pre-charge current from 1 mA to 450 mA

- Adjustable floating voltage up to 4.45 V

- Integrated low quiescent LDO regulator

- · Automatic power path management

- Auto-recharge function

- Embedded protection circuit module (PCM) featuring battery overcharge, battery over-discharge and battery overcurrent protections

- Charging timeout to terminate the charging process for safety reasons

- Shipping mode feature allows battery low leakage when over-discharged

- Very low battery leakage in over-discharge and shutdown mode

- Charge/fault status output

- Battery voltage pin to allow external gauging

- Two 3 Ω SPDT load switches

- Reset generator triggered by USB detection

- SWIRE allows the STBC02 functions to be controlled

- Available in Flip Chip 30, 0.4 mm pitch package

- Rugged ±4 kV HBM, ESD protection on the most critical pins

### **Applications**

- Smart watches and wearable devices

- · Fitness and medical accessories

- · Li-Ion and other Li-Poly battery rechargeable equipment

### **Description**

The STBC02 is a highly integrated power management, embedding a linear battery charger, a 150 mA LDO, 2 SPDT load switches, a smart reset/watchdog block and a protection circuit module (PCM) to prevent the battery from being damaged under fault conditions.

The STBC02 uses a CC/CV algorithm to charge the battery; the fast charge and the pre-charge current can be both independently programmed using dedicated resistors. The termination current is set by default, being 5% of the programmed fast charge current, but it can also be fixed to different values. Likewise, the battery floating voltage value is programmable and can be set to a value up to 4.45 V.

The STBC02 also features a charger enable input to stop the charging process anytime.

The STBC02 is automatically powered off from the connected battery when the IN pin is not connected to a valid power source (battery mode).

A battery under/overtemperature condition can be detected by using an external circuitry (NTC thermistor).

The STBC02 draws less than 10 nA from the connected battery in shipping mode conditions, so to maximize the battery life during end product shelf life. The device is available in the Flip Chip 30 package.

DS11617 - Rev 5 page 2/35

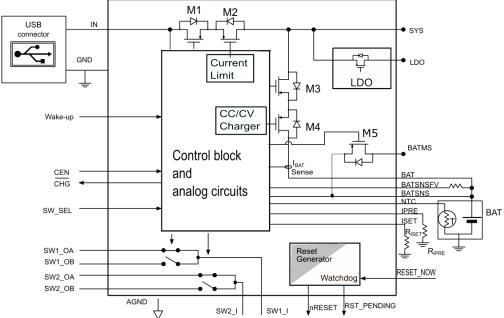

# Application schematic

LDO LOAD V<sub>BUS</sub> GND System Alternative CHG SYS load CEN RESET\_NOW RST\_PENDING nRESET SW\_SEL LDO; BATMS SW2\_I ADC SW2\_OA ◀ SW2\_OB ◀ NTC BATSNS ISET BATSNSFV Battery IPRE pack WAKE-UP

Figure 1. STBC02 application schematic

Table 1. Typical bill of material (BOM)

| Symbol             | Value                     | Description                             | Note         |

|--------------------|---------------------------|-----------------------------------------|--------------|

| C <sub>IN</sub>    | 10 μF (16 V)              | Input supply voltage capacitor          | Ceramic type |

| C <sub>SYS</sub>   | 1 μF (10 V)               | System output capacitor                 | Ceramic type |

| R <sub>ISET</sub>  | Refer to I <sub>SET</sub> | Charge current programming resistor     | Film type    |

| R <sub>IPRE</sub>  | Refer to I <sub>PRE</sub> | Pre-charge current programming resistor | Film type    |

| C <sub>BAT</sub>   | 4.7 μF (6.3 V)            | Battery positive terminal capacitor     | Ceramic type |

| R <sub>FLOAT</sub> | BATSNSFV                  | Floating voltage programming resistor   | Film type    |

| R <sub>PUP</sub>   | 10-100 kΩ                 | nRESET pull-up resistor (1)             | Film type    |

| R <sub>CHG</sub>   | 10 kΩ                     | Charging/fault pull-up resistor (2)     | Film type    |

| C <sub>LDO</sub>   | 1.0 μF (10 V)             | LDO output capacitor                    | Ceramic type |

<sup>1.</sup> R<sub>PUP</sub> is tied to LDO pin or to a higher voltage.

DS11617 - Rev 5 page 3/35

<sup>2.</sup>  $R_{CHG}$  must be calculated according to the external LED electrical characteristics.

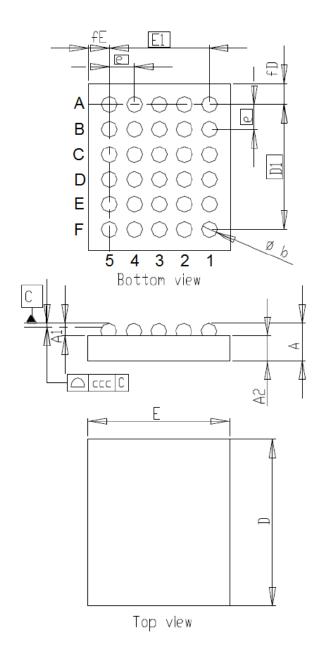

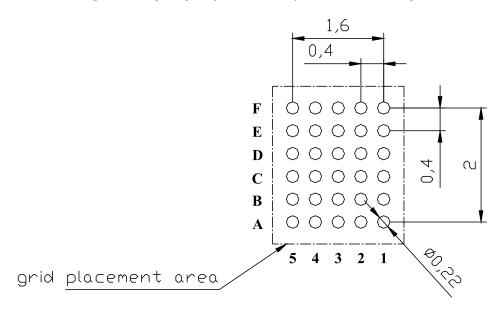

# 2 Pin configuration (top through view)

Figure 2. Pin configuration top through view

| A1        | A2          | A3     | A4     | A5  |

|-----------|-------------|--------|--------|-----|

| RESET_NOW | BATSNSFV    | GND    | ISET   | BAT |

| B1        | B2          | B3     | B4     | B5  |

| CEN       | RST_PENDING | BATSNS | AGND   | BAT |

| C1        | C2          | C3     | C4     | C5  |

| SW_SEL    | NRESET      | NC     | BATMS  | SYS |

| D1        | D2          | D3     | D4     | D5  |

| NTC       | WAKE_UP     | NC     | IPRE   | SYS |

| E1        | E2          | E3     | E4     | E5  |

| CHG       | SW2_I       | SW1_OB | SW1_OA | IN  |

| F1        | F2          | F3     | F4     | F5  |

| SW2_OB    | SW2_OA      | SW1_I  | LDO    | IN  |

Table 2. Pin description

| В            | ump         | Bump<br>name | Description                                                                                                                             |                                                 |  |

|--------------|-------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|--|

|              | IN          | E5-F5        | Input supply voltage. Bypass this                                                                                                       | pin to ground with a 10 μF capacitor            |  |

|              | BAT         | A5-B5        | Battery positive terminal. Bypass                                                                                                       | this pin to GND with a 4.7 µF ceramic capacitor |  |

|              | SYS         | C5-D5        | System output. Bypass this pin to                                                                                                       | ground with 1 μF ceramic capacitor              |  |

| Power        | LDO         | F4           | LDO output. Bypass this pin to gi                                                                                                       | round with 1 μF ceramic capacitor               |  |

|              | NTC         | D1           | Battery temperature monitor pin                                                                                                         |                                                 |  |

|              | AGND        | B4           | Analog ground                                                                                                                           | Connect together with the same ground layer     |  |

|              | GND         | A3           | GROUND                                                                                                                                  | Connect together with the same ground layer     |  |

| Drogramming  | ISET        | A4           | Fast charge current programming resistor                                                                                                |                                                 |  |

| Programming  | IPRE        | D4           | Pre-charge current programming resistor                                                                                                 |                                                 |  |

|              | BATMS       | C4           | Battery voltage measurement pin                                                                                                         |                                                 |  |

| Sensing      | BATSNS      | В3           | Battery voltage sensing. Connect as close as possible to the battery positive terminal                                                  |                                                 |  |

|              | BATSNSFV    | A2           | Floating voltage sensing. Connecterminal                                                                                                | ct as close as possible to the battery positive |  |

|              | CEN         | B1           | Charger enable pin. Active high.                                                                                                        | 500 kΩ internal pull-up (to LDO)                |  |

| Digital I/Os | CHG         | E1           | Charging/fault flag. Active low (or                                                                                                     | pen drain output)                               |  |

| Digital I/Os | WAKE-UP     | D2           | Shipping mode exit input pin. Act                                                                                                       | ive high. 50 kΩ internal pull-down              |  |

|              | SW_SEL      | C1           | Load switch selection input (refer                                                                                                      | to LDO level)                                   |  |

|              | nRESET      | C2           | Smart reset output signal (open drain output). A pull-up resistor (10 – 100 k $\Omega$ ) is connected to LDO pin or to a higher voltage |                                                 |  |

| Digital I/Os | RST_PENDING | B2           | Reset output signal (totem pole of                                                                                                      | output)                                         |  |

|              | RESET_NOW   | A1           | Smart reset input signal (referred is enabled                                                                                           | to LDO level); RESET_CLEAR when watchdog        |  |

DS11617 - Rev 5 page 4/35

| Bump          |                                                                                      | Bump<br>name                                           | Description                                                                  |                                                                                                                              |  |

|---------------|--------------------------------------------------------------------------------------|--------------------------------------------------------|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--|

|               | SW1_I                                                                                | F3                                                     | Load switch SPDT1 input (1.8 V to 5 V range)                                 |                                                                                                                              |  |

|               | SW1_OA                                                                               | E4                                                     | Load switch SPDT1 output A (enabled/disabled by SWIRE)                       |                                                                                                                              |  |

| Switch matrix | SW1_OB                                                                               | E3                                                     | Load switch SPDT1 output B (enabled/disabled by SWIRE)                       | If SPDT switches are used, decoupling capacitors are recommended on input and output. Capacitor values depend on application |  |

| Switch matrix | SW2_I E2 Load switch SPDT2 input ( to 5 V range)  SW2_OA F2 Load switch SPDT2 output | Load switch SPDT2 input (1.8 V to 5 V range)           | conditions and requirements.  If not used, connect inputs and outputs to GND |                                                                                                                              |  |

|               |                                                                                      | Load switch SPDT2 output A (enabled/disabled by SWIRE) |                                                                              |                                                                                                                              |  |

|               | SW2_OB                                                                               | F1                                                     | Load switch SPDT2 output B (enabled/disabled by SWIRE)                       |                                                                                                                              |  |

| -             | NC                                                                                   | C3-D3                                                  | Not connected                                                                | Leave floating                                                                                                               |  |

DS11617 - Rev 5 page 5/35

# 3 Maximum ratings

Table 3. Absolute maximum ratings

| Symbol                                                            | Parameter                                                                 | Test conditions                      | Value                         | Unit |

|-------------------------------------------------------------------|---------------------------------------------------------------------------|--------------------------------------|-------------------------------|------|

| V <sub>IN</sub>                                                   | Input supply voltage pin                                                  | DC voltage                           | -0.3 to +16.0                 | V    |

| $V_{LDO}$                                                         | LDO output pin voltage                                                    | DC voltage                           | -0.3 to +4.0                  | V    |

| V <sub>SYS</sub>                                                  | SYS pin voltage                                                           | DC voltage                           | -0.3 to +6.5                  | V    |

| $V_{SW}$                                                          | Switch pin voltage (SW1_I, SW2_I, SW1_OA,SW1_OB, SW2_OA, SW2_OB)          | DC voltage                           | -0.3 to +6.5                  | V    |

| V <sub>CHG</sub>                                                  | CHG pin voltage                                                           | DC voltage                           | -0.3 to +6.5                  | V    |

| V <sub>Wake-up</sub>                                              | WAKE-UP pin voltage                                                       | DC voltage                           | -0.3 to +4.6                  | V    |

| $V_{LGC}$                                                         | Voltage on logic pins (CEN,<br>SW_SEL, RESET_NOW, nRESET,<br>RST_PENDING) | DC voltage                           | -0.3 to +4.0                  | V    |

| V <sub>ISET</sub> , V <sub>IPRE</sub>                             | Voltage on ISET, IPRE pins                                                | DC voltage                           | -0.3 to +2                    | V    |

| V <sub>NTC</sub>                                                  | Voltage on NTC pin                                                        | DC voltage                           | -0.3 to V <sub>LDO</sub>      | V    |

| V <sub>BAT</sub> , V <sub>BATSNS</sub> ,<br>V <sub>BATSNSFV</sub> | Voltage on BAT, BATSNS and<br>BATSNSFV pins                               | DC voltage                           | -0.3 to +5.5                  | V    |

| V <sub>BATMS</sub>                                                | Voltage on BATMS pin                                                      | DC voltage                           | -0.3 to V <sub>BAT</sub> +0.3 | V    |

| ESD                                                               | Human body model (IN, SYS, WAKE-UP, LDO, BAT, BATSNS, BATSNSFV)           | JS-001-2012 vs. AGND<br>PGND and GND | ±4000                         | V    |

|                                                                   | Human body model (all the others)                                         | JS-001-2012                          | ±2000                         | V    |

| T <sub>AMB</sub>                                                  | Operating ambient temperature                                             |                                      | -40 to +85                    | °C   |

| TJ                                                                | Maximum junction temperature                                              |                                      | +125                          | °C   |

| T <sub>STG</sub>                                                  | Storage temperature                                                       |                                      | -65 to +150                   | °C   |

Note:

Absolute maximum ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied.

Table 4. Thermal data

| Symbol                           | Parameter                                | Flip Chip 30 (2.25 x 2.59 mm) | Unit |

|----------------------------------|------------------------------------------|-------------------------------|------|

| R <sub>THJB</sub> <sup>(1)</sup> | Junction-to-pcb board thermal resistance | 50                            | °C/W |

1. Standard FR4 pcb board.

DS11617 - Rev 5 page 6/35

## 4 Electrical characteristics

$V_{IN}$  = 5 V,  $V_{BAT}$  = 3.6 V,  $C_{LDO}$  = 1 μF,  $C_{BATT}$  = 4.7 μF,  $C_{IN}$  = 10 μF,  $C_{SYS}$  = 1 μF,  $R_{ISET}$  = 1 kΩ, SD = low, CEN = high,  $R_{IPRE}$  = 4.7 kΩ,  $T_A$  = 25 °C, SW\_SEL = GND or LDO, RESET\_NOW = GND or LDO, WAKE-UP floating unless otherwise specified.

**Table 5. Electrical characteristics**

| Symbol              | Parameter                                           | Test conditions                                                                                        | Min.  | Тур.                                                                  | Max.                     | Unit               |    |    |

|---------------------|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------|-------|-----------------------------------------------------------------------|--------------------------|--------------------|----|----|

|                     |                                                     | V <sub>FLOAT</sub> set 4.2 V, I <sub>FAST</sub> < 250 mA                                               | 4.55  |                                                                       | 5.4                      | V                  |    |    |

| $V_{IN}$            | Operating input voltage                             | V <sub>FLOAT</sub> set 4.45 V, I <sub>FAST</sub> < 450 mA,<br>I <sub>SYS</sub> =I <sub>LDO</sub> =0 mA | 4.75  |                                                                       | 5.4 <sup>(1)</sup>       | V                  |    |    |

| V <sub>INOVP</sub>  | Input overvoltage protection                        | V <sub>IN</sub> rising                                                                                 | 5.6   | 6.0                                                                   | 6.4                      | V                  |    |    |

| V <sub>INOVPH</sub> | Input overvoltage protection hysteresis             | V <sub>IN</sub> falling                                                                                |       | 200                                                                   |                          | mV                 |    |    |

| V <sub>UVLO</sub>   | Undervoltage lock-out                               | V <sub>IN</sub> falling                                                                                |       | 3.9                                                                   |                          | V                  |    |    |

| V <sub>UVLOH</sub>  | Undervoltage lock-out hysteresis                    | V <sub>IN</sub> rising                                                                                 |       | 300                                                                   |                          | mV                 |    |    |

| 1                   | IN complete company                                 | Charger disabled mode (CEN = low),<br>I <sub>SYS</sub> =I <sub>LDO</sub> =0 A                          |       | 600                                                                   |                          | μA                 |    |    |

| I <sub>IN</sub>     | IN supply current                                   | Charging, $V_{HOT} < V_{NTC} < V_{COLD}$ , including $R_{ISET}$ current                                |       | 1.4                                                                   |                          | mA                 |    |    |

| V <sub>FLOAT</sub>  | Battery floating voltage                            | IBAT=1 mA, BATSNS and BATSNSFV short to battery terminal                                               | 4.179 | 4.2                                                                   | 4.221                    | V                  |    |    |

|                     |                                                     | Battery-powered mode (V <sub>IN</sub> <v<sub>UVLO), I<sub>LDO</sub>=0 A</v<sub>                        |       | 4                                                                     | 8                        | μA                 |    |    |

| l=                  | DAT nin augusty augrent                             | Charge terminated                                                                                      |       | 9                                                                     | 12                       | μA                 |    |    |

| I <sub>BAT</sub>    | BAT pin supply current                              | Shutdown mode (by SWIRE)                                                                               |       | 10                                                                    | 50                       |                    |    |    |

|                     |                                                     |                                                                                                        |       | Over-discharge mode ( $V_{BAT}$ < $V_{ODC}$ , $V_{IN}$ < $V_{UVLO}$ ) |                          | 10                 | 50 | nA |

| I <sub>FAST</sub>   | Fast charge current                                 | $R_{ISET}$ =430 $\Omega$ , constant-current mode $I_{LDO}$ + $I_{SYS}$ <150 mA                         |       | 450                                                                   | 500                      | mA                 |    |    |

|                     |                                                     | R <sub>ISET</sub> =1 kΩ, constant-current mode                                                         |       | 200                                                                   |                          |                    |    |    |

| I <sub>PRE</sub>    | Pre-charge current                                  | R <sub>IPRE</sub> =10 kΩ, constant-current mode                                                        |       | 20                                                                    |                          | mA                 |    |    |

| V <sub>ISET</sub>   | I <sub>SET</sub> regulated voltage                  |                                                                                                        |       | 1                                                                     |                          | V                  |    |    |

| V <sub>IPRE</sub>   | I <sub>PRE</sub> regulated voltage                  |                                                                                                        |       | 1                                                                     |                          | V                  |    |    |

| V <sub>PRE</sub>    | Pre-charge to fast charge battery voltage threshold | Charger active                                                                                         |       | 3                                                                     |                          | V                  |    |    |

| 1                   | End of the control of                               | Charging in CV mode for 20 mA <i<sub>FAST</i<sub>                                                      |       | 5                                                                     |                          | %I <sub>FAST</sub> |    |    |

| I <sub>END</sub>    | End-of-charge current                               | Charging in CV mode for I <sub>FAST</sub> <20 mA                                                       | ;     | See Table 10. I <sub>F</sub>                                          | AST and I <sub>END</sub> |                    |    |    |

|                     | Datha market                                        | V <sub>BAT</sub> rising, BATSNSFV short to battery terminal                                            | 4.245 | 4.275                                                                 | 4.305                    | V                  |    |    |

| V <sub>OCHG</sub>   | Battery voltage overcharge threshold                | V <sub>BAT</sub> rising, BATSNSFV short to battery terminal with floating voltage adjustment enabled   |       | V <sub>FLOAT</sub> +75                                                |                          | mV                 |    |    |

DS11617 - Rev 5 page 7/35

| Symbol                  | Parameter                                                                  | Test conditions                                                                                                                        | Min.    | Тур.                   | Max.   | Unit |

|-------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|---------|------------------------|--------|------|

| V <sub>OCHG</sub>       | Battery voltage overcharge threshold                                       | V <sub>BAT</sub> rising, external resistor between BATSNSFV and battery terminal                                                       |         | V <sub>FLOAT</sub> +75 |        | mV   |

| V <sub>ODC</sub>        | Battery voltage over-discharge threshold                                   | V <sub>IN</sub> <v<sub>UVLO, I<sub>LDO</sub>=150 mA,<br/>BATSNSFV and BATSNS short to<br/>battery terminal</v<sub>                     | 2.750   | 2.8                    | 2.850  | V    |

| V <sub>ODCR</sub>       | Battery voltage over-discharge release threshold                           | V <sub>UVLO</sub> <v<sub>IN<v<sub>OVP, I<sub>LDO</sub> = 150 mA,<br/>BATSNSFV and BATSNS short to<br/>battery terminal</v<sub></v<sub> | 3.0     |                        |        | V    |

| V <sub>WAKE-UP</sub>    | Wake-up voltage threshold                                                  | V <sub>BAT</sub> >3 V rising, I <sub>LDO</sub> =150 mA                                                                                 | VBAT    |                        |        | V    |

| R <sub>ON-IS</sub>      | Input to SYS on-resistance                                                 |                                                                                                                                        |         | 0.25                   | 0.35   | Ω    |

| R <sub>ON-BS</sub>      | Battery to SYS on-resistance                                               |                                                                                                                                        |         | 0.35                   | 0.4    | Ω    |

| R <sub>ON-BATMS</sub>   | BATSNS to BATMS on-<br>resistance                                          | I <sub>SINK</sub> =500 μA                                                                                                              | 290     |                        | 550    | Ω    |

| R <sub>ON-LOADSW1</sub> | Input to output load switch 1 resistance                                   | V <sub>SW1_l</sub> =1.8 V to 5 V SW1_OA or<br>SW1_OB test current=50 mA                                                                | 2.0     |                        | 3.8    | Ω    |

| R <sub>ON-LOADSW2</sub> | Input to output load switch 2 resistance                                   | V <sub>SW2_I</sub> =1.8 V to 5 V<br>SW2_OA or SW2_OB test<br>current=50 mA                                                             | 2.0     |                        | 3.4    | Ω    |

| V <sub>OL</sub>         | Output low level (CHG, nRESET, RST_PENDING)                                | I <sub>SINK</sub> =5 mA                                                                                                                |         |                        | 0.4    | V    |

| V <sub>OH</sub>         | Output high level (RST_PENDING)                                            | I <sub>OH</sub> =5 mA (referred to LDO output)                                                                                         | LDO-200 |                        |        | mV   |

| I <sub>OHZ</sub>        | High level open drain output current (CHG, nRESET)                         | V <sub>OH</sub> =5 V                                                                                                                   |         |                        | 1      | μA   |

| V <sub>IL</sub>         | Logic low input level (CEN, SW_SEL, RESET_NOW)                             | All versions with LDO 3 V, 3.1 V or                                                                                                    |         |                        | 0.4    | V    |

| V <sub>IH</sub>         | Logic high input level (CEN, SW_SEL, RESET_NOW)                            | 3.3 V                                                                                                                                  | 1.6     |                        |        | V    |

| R <sub>UP</sub>         | CEN pull-up resistor                                                       |                                                                                                                                        | 375     | 500                    | 625    | kΩ   |

| $V_{LDO}$               | LDO output voltage                                                         | I <sub>LDO</sub> =1 mA                                                                                                                 | -3      | V <sub>LDO</sub> (2)   | +3     | %    |

| ΔV <sub>OUT-LOAD</sub>  | LDO static load regulation                                                 | I <sub>LDO</sub> =1 mA to 150 mA                                                                                                       |         | ±0.002                 | ±0.003 | %/mA |

| I <sub>SC</sub>         | LDO short-circuit current                                                  | R <sub>LOAD</sub> =0 Ω                                                                                                                 | 250     | 350                    |        | mA   |

| t <sub>ON</sub>         | LDO turn-on time                                                           | 0 to 95% V <sub>LDO</sub> , I <sub>OUT</sub> =150 mA                                                                                   |         | 210                    |        | μs   |

| Іватоср                 | Battery discharge overcurrent protection                                   | V <sub>IN</sub> <v<sub>UVLO (powered from BAT), it can be set by 4 SWIRE steps</v<sub>                                                 |         | 900                    |        | mA   |

| I <sub>INLIM</sub>      | Input current limitation                                                   | V <sub>SYS</sub> > V <sub>ILIMSCTH</sub> ; V <sub>UVLO</sub> <v<sub>IN &lt;<br/>V<sub>INOVP</sub> (powered from IN)</v<sub>            |         | 1.7                    |        | А    |

| V <sub>ILIMSCTH</sub>   | SYS voltage threshold for input current limitation short-circuit detection | V <sub>UVLO</sub> <v<sub>IN<v<sub>INOVP</v<sub></v<sub>                                                                                |         | 2                      |        | V    |

| V <sub>SCSYS</sub>      | SYS short-circuit protection threshold                                     | $V_{IN}$ < $V_{UVLO}$ or $V_{IN}$ > $V_{INOVP}$ (powered from BAT)                                                                     |         | V <sub>BAT</sub> -0.8  |        | V    |

| I <sub>NTCB</sub>       | NTC pin bias current                                                       | V <sub>NTC</sub> =0.25 V                                                                                                               | 45      | 50                     | 55     | μA   |

| V <sub>HOT</sub>        | Thermal hot threshold                                                      | Increasing NTC temperature                                                                                                             | 0.234   | 0.246                  | 0.258  | V    |

| V <sub>COLD</sub>       | Thermal cold threshold                                                     | Decreasing NTC temperature                                                                                                             | 1.28    | 1.355                  | 1.43   | V    |

| T <sub>HYST</sub>       | Hot/cold temperature thresholds hysteresis                                 | 10 kΩ NTC, ß=3370                                                                                                                      |         | 3                      |        | °C   |

DS11617 - Rev 5 page 8/35

| Symbol              | Parameter                                                        | Test conditions                                                                                                          | Min.  | Тур.  | Max.  | Unit |

|---------------------|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|------|

| T <sub>SD</sub>     | Thermal shutdown die temperature                                 |                                                                                                                          |       | 155   |       | °C   |

| T <sub>WRN</sub>    | Thermal warning die temperature                                  |                                                                                                                          |       | 135   |       | °C   |

| t <sub>PW-VIN</sub> | Minimum input voltage connection time to exit from shutdown mode | V <sub>BAT</sub> =3.5 V, R <sub>NTC</sub> =10 kΩ                                                                         |       | 350   |       | ms   |

| toco                | Overcharge detection delay                                       | V <sub>BAT</sub> > V <sub>OCHG</sub> , V <sub>UVLO</sub> <v<sub>IN<v<sub>INOVP</v<sub></v<sub>                           |       | 1.2   |       | S    |

| t <sub>ODD</sub>    | over-discharge detection delay                                   | $V_{BAT}$ < $V_{ODC}$ and $V_{IN}$ < $V_{UVLO}$ or $V_{IN}$ >                                                            |       | 60    |       | ms   |

| t <sub>DOD</sub>    | Discharge overcurrent detection delay                            | I <sub>BAT</sub> > I <sub>BATOCP</sub> , V <sub>IN</sub> <v<sub>UVLO or V<sub>IN</sub>&gt;<br/>V<sub>INOVP</sub></v<sub> |       | 10    |       | ms   |

| t <sub>PFD</sub>    | Pre-charge to fast charge transition deglitch time               | Rising                                                                                                                   |       | 100   |       | ms   |

| t <sub>FPD</sub>    | Fast charge to pre-charge fault deglitch time                    |                                                                                                                          |       | 10    |       | ms   |

| $t_{END}$           | End-of-charge deglitch time                                      |                                                                                                                          |       | 100   |       | ms   |

| t <sub>PRE</sub>    | Pre-charge timeout                                               | V <sub>BAT</sub> =2 V, charging                                                                                          |       | 1800  |       | S    |

| t <sub>FAST</sub>   | Fast charge timeout                                              |                                                                                                                          | 14000 | 18000 | 22000 | s    |

| t <sub>CRDD</sub>   | Charger restart deglitch time                                    | After end-of-charge, V <sub>BAT</sub> <3.9 V restart enabled                                                             |       | 1200  |       | ms   |

| V <sub>REC</sub>    | Charger restart threshold                                        | After end-of-charge, restart enabled                                                                                     |       | 3.9   |       | V    |

| t <sub>NTCD</sub>   | Battery temperature transition deglitch time                     |                                                                                                                          |       | 100   |       | ms   |

| t <sub>PW</sub>     | CEN valid input pulse width                                      |                                                                                                                          | 15    |       |       | ms   |

| t <sub>PW-WA</sub>  | WAKE-UP valid input pulse width                                  |                                                                                                                          | 1200  |       |       | ms   |

| tDbus-ires          | Internal RESET deglitch time                                     | From V <sub>BUS</sub> (V <sub>IN</sub> ) detection to internal RST_PENDING signal                                        |       | 150   |       | ms   |

| tDRST_P             | Internal RST_P delay time                                        | From RST_PENDING rising to RST pending GND                                                                               |       | 4000  |       | ms   |

| nRESETP (3)         | nRESET pulse duration                                            | V <sub>IN</sub> mode                                                                                                     |       | 25    |       | μs   |

| _IIIXEOETI (*/      | micor paloo daration                                             | Battery mode                                                                                                             |       | 50    |       | μο   |

<sup>1.</sup> If the internal thermal temperature of the STBC02 reaches  $T_{WRN}$ , then the programmed  $I_{FAST}$  is halved until the internal temperature drops below  $T_{WRN}$  - 10 °C typically. A warning is signaled via the CHG output.

DS11617 - Rev 5 page 9/35

<sup>2.</sup> Typical voltage depends on the selected order code.

<sup>3.</sup> Details can be found inside smart reset section.

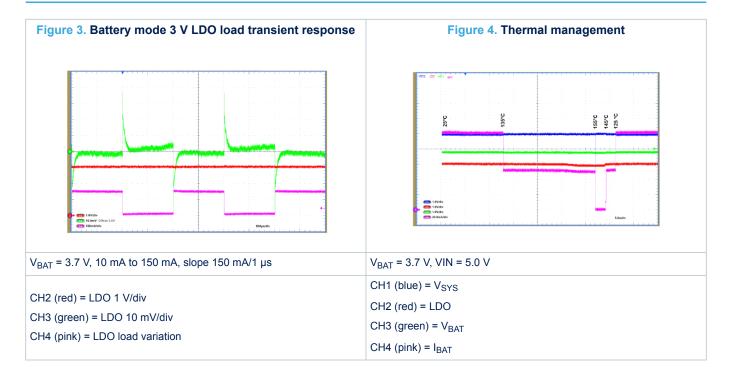

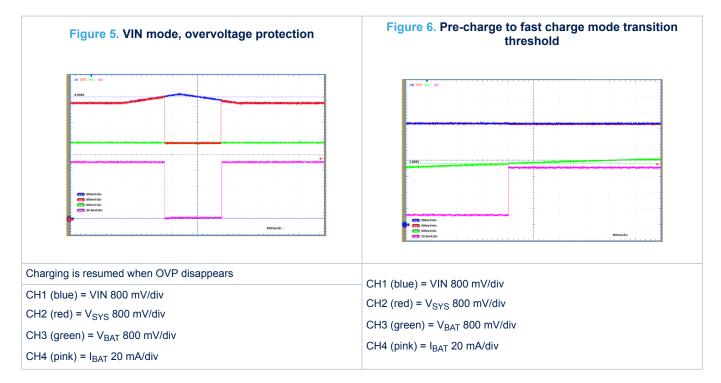

# 5 Typical performance characteristics

DS11617 - Rev 5 page 10/35

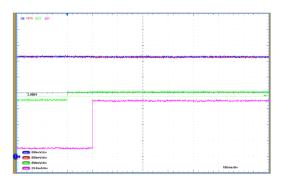

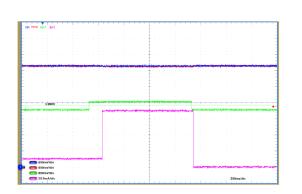

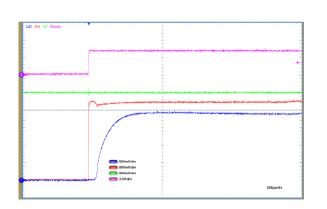

Figure 7. Pre-charge to fast charge mode transition deglitch

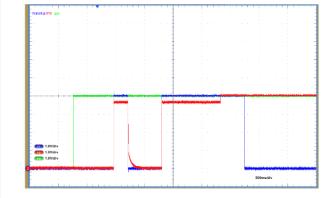

Figure 8. Pre-charge to fast charge mode to no charge mode transition

CH1 (blue) = VIN 800 mV/div

CH2 (red) =  $V_{SYS}$  800 mV/div

CH3 (green) = V<sub>BAT</sub> 800 mV/div

CH4 (pink) =  $I_{BAT}$  20 mA/div

CH1 (blue) = VIN 800 mV/div

CH2 (red) =  $V_{SYS}$  800 mV/div

CH3 (green) =  $V_{BAT}$  800 mV/div

CH4 (pink) =  $I_{BAT}$  20 mA/div

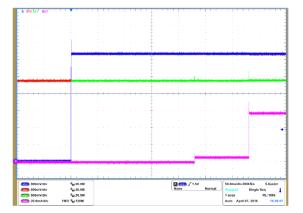

Figure 9. Wake-up pin operation

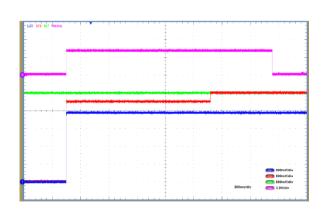

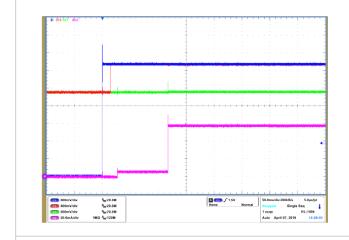

Figure 10. VIN plug, charging initialization

Shutdown mode to battery mode transition. VIN floating

CH1 (blue) = WAKE-UP pin 800 mV/div

CH2 (red) =  $V_{SYS}$  800 mV/div

CH3 (green) =  $V_{BAT}$  800 mV/div

Shutdown mode to VIN mode transition

CH1 (blue) = VIN 800 mV/div;

CH2 (red) =  $V_{SYS}$  800 mV/div

CH3 (green) = V<sub>BAT</sub> 800 mV/div

CH4 (pink) =  $I_{BAT}$  20 mA/div

DS11617 - Rev 5 page 11/35

Figure 12. Wake-up operation, VSYS and LDO rise detail

CH1 (blue) =  $V_{LDO}$  800 mV/div

CH2 (red) =  $V_{SYS}$  800 mV/div

CH3 (green) = V<sub>BAT</sub> 800 mV/div

CH4 (pink) = Wake-up 3 V/div

CH1 (blue) =  $V_{LDO}$  800 mV/div

CH2 (red) =  $V_{SYS}$  800 mV/div

CH3 (green) = V<sub>BAT</sub> 800 mV/div

CH4 (pink) = Wake-up 3 V/div

Figure 13. VIN plug, charging initialization battery mode to VIN mode transition

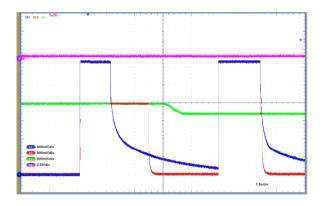

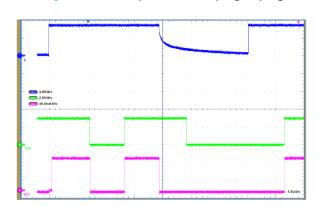

Figure 14. Shutdown mode entry and exit

CH1 (blue) = VIN 800 mV/div

CH2 (red) =  $V_{SYS}$  800 mV/div

CH3 (green) =  $V_{BAT}$  800 mV/div

CH4 (pink) =  $I_{BAT}$  20 mA/div

By SW\_SEL command, battery level over  $V_{ODC}$  and below  $V_{ODC}$

CH1 (blue) = VIN 800 mV/div

CH2 (red) =  $V_{SYS}$  800 mV/div

CH3 (green) =  $V_{BAT}$  800 mV/div

CH4 (pink) = SW\_SEL 2 V/div

DS11617 - Rev 5 page 12/35

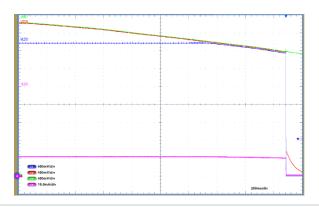

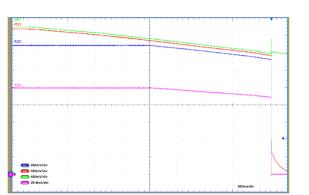

LDO loaded by 10 mA; V<sub>ODC</sub> cut-off

CH1 (blue) =  $V_{LDO}$  400 mV/div

CH2 (red) =  $V_{SYS}$  400 mV/div

CH3 (green) =  $V_{BAT}$  400 mV/div

CH4 (pink) =  $I_{LDO}$  10 mA/div

LDO loaded by 100 mA; V<sub>ODC</sub> cut-off

CH1 (blue) =  $V_{LDO}$  400 mV/div

CH2 (red) =  $V_{SYS}$  400 mV/div

CH3 (green) =  $V_{BAT}$  400 mV/div

CH4 (pink) =  $I_{LDO}$  20 mA/div

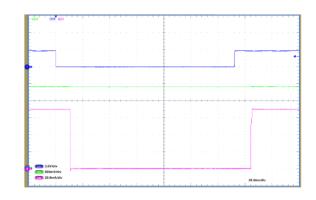

Figure 17. CEN operation

Figure 18. CEN operation, VIN plug/unplug

CH1 (blue) = CEN 3 V/div

CH3 (green) =  $V_{BAT}$  800 mV/div

CH4 (pink) = I<sub>BAT</sub> 20 mA/div

CH1 (blue) = IN pin 3.0 V/div

CH3 (green) = CEN 2.0 V/div

CH4 (pink) =  $I_{BAT}$  30 mA/div

DS11617 - Rev 5 page 13/35

## 6 Functional pin description

### 6.1 GND, AGND

The STBC02 ground pins.

### 6.2 NTC

The battery temperature monitoring pin. Connect the battery NTC thermistor to this pin. The charging cycle stops when the battery temperature is outside of the safe temperature range (0 °C to 45 °C). When the charging cycle is completed, the NTC pin goes to a high impedance state, therefore the NTC thermistor can be also used, together with an external circuitry, to monitor the battery temperature while it is discharging. If the NTC thermistor is not used, a 10 k $\Omega$  resistor must be connected to ensure proper IC operations.

### 6.3 ISET, IPRE

Fast and pre-charge current programming pins. Connect two resistors ( $R_{ISET}$ ,  $R_{IPRE}$ ) to ground to set the fast and pre-charge current ( $I_{FAST}$ ,  $I_{PRE}$ ) according to the following equation (valid for  $I_{FAST}$ ,  $I_{PRE}$  > 5 mA):

### **Equation 1:**

$$I_{PRE} = \frac{V_{IPRE}}{R_{IPRE}} *K ; \qquad I_{FAST} = \frac{V_{ISET}}{R_{ISET}} *K \tag{1}$$

Where  $V_{ISET} = V_{IPRE} = 1 \text{ V}$  and K = 200. Fast charge and pre-charge currents can be independently set from 1 mA to 450 mA. End-of-charge current value is typically 5% of the fast charging current value being set. For low charging current ( $I_{FAST}$ ,  $I_{PRE} < 5$  mA), the  $R_{ISET}$  and  $R_{IPRE}$  values in following table must be used.

| I <sub>FAST</sub> , I <sub>PRE</sub> | R <sub>ISET</sub> , R <sub>IPRE</sub> |

|--------------------------------------|---------------------------------------|

| 5 mA                                 | 40.5 k                                |

| 2 mA                                 | 110 k                                 |

| 1 mA                                 | 260 k                                 |

Table 6. Charging current setting

Both R<sub>ISET</sub> and R<sub>IPRE</sub> must be always used. Short-circuit to ground or open circuit are not allowed options.

### 6.4 BATMS

Battery voltage measurement. BATMS pin is internally shorted to the BATSNS pin during normal conditions to monitor the battery voltage using external components ( $\mu$ C and embedded ADC). The internal path from BATMS pin to the battery is opened in case any of the following conditions occur: overcurrent, battery over-discharge, shutdown mode, short-circuit on SYS or LDO. This function can be enabled / disabled by SWIRE. To minimize overall system power consumption, this function must be disabled.

## 6.5 BATSNS, BATSNSFV

Battery voltage sense pin. The BATSNS pin must be connected as close as possible to the battery positive terminal to ensure the maximum accuracy on the floating voltage and on the battery voltage protection thresholds. The BATSNSFV pin can be used to fix the  $V_{FLOAT}$  value by connecting a proper external series resistor (to BATSNSFV. The battery floating voltage can be set up to 4.45 V according to the following equation:

### **Equation 2:**

$$Vfloat_{adj} = Vfloat_{def} * \left(1 + \frac{R_{float}}{1M\Omega}\right)V = 4.2 * \left(1 + \frac{R_{float}}{1M\Omega}\right)V$$

(2)

Example: to set the battery floating voltage at 4.35 V, refer to the following equation.

#### **Equation 3:**

DS11617 - Rev 5 page 14/35

$$R_{ext} = 1M\Omega * \left( \frac{Vfloat_{adj}}{4.2V} - 1 \right) = 1M\Omega * \left( \frac{4.35V}{4.2V} - 1 \right) = 35.7K\Omega$$

(3)

If the BATSNSFV pin is connected to the battery positive terminal, the floating voltage is set at its 4.2 V default value.

### 6.6 BAT

External battery connection pin (positive terminal). A 4.7 µF ceramic bypass capacitor must be connected to GND.

#### 6.7 IN

5 V input supply voltage pin. The STBC02 is powered off from this pin when a valid voltage source is detected, meaning a voltage higher than  $V_{UVLO}$  and lower than  $V_{INOVP}$ . A 10  $\mu F$  ceramic bypass capacitor must be connected to GND.

### 6.8 SYS

The internal LDO input voltage and external unregulated supply pin. The maximum current deliverable through this pin depends on the following two conditions: LDO load and battery status. However, if none of the above loads sink current, the maximum SYS current budget is 450 mA, provided that the input voltage source can deliver that amount of current.

SYS voltage source can be either IN or BAT, depending on the operating conditions (refer to the following table). A ceramic bypass capacitor of 1 µF must be connected to GND.

| V <sub>IN</sub>                                | V <sub>BAT</sub>                  | SYS status                      | LDO status |

|------------------------------------------------|-----------------------------------|---------------------------------|------------|

| < V <sub>UVLO</sub>                            | < V <sub>ODC</sub> <sup>(1)</sup> | Not powered                     | Off        |

| < V <sub>UVLO</sub>                            | > V <sub>ODC</sub>                | V <sub>BAT</sub> <sup>(2)</sup> | On         |

| > < V <sub>UVLO</sub> and < V <sub>INOVP</sub> | X (don't care) (3)                | V <sub>IN</sub>                 | On         |

| > V <sub>INOVP</sub>                           | < V <sub>ODC</sub>                | Not powered                     | Off        |

| > V <sub>INOVP</sub>                           | > V <sub>ODC</sub>                | V <sub>BAT</sub> <sup>(2)</sup> | On         |

Table 7. SYS voltage source

- 1. V<sub>ODCR</sub> if the shutdown mode or the over-discharge protection has been previously activated.

- 2. Voltage drop over internal MOSFET is not included.

- 3. Battery disconnected (0 V) or fully discharged. Resistive short-circuit is not supported for safety reasons.

#### 6.9 LDO

LDO output voltage pin. The regulated voltage (it can be 3 V, 3.1 V, or 3.3 V) depends on the selected STBC02 order code. The maximum current capability is anyhow 150 mA. A 1  $\mu$ F ceramic bypass capacitor must be connected to GND.

## 6.10 WAKE-UP

Wake-up input pin. To restore normal operations of the STBC02, so to exit from a shutdown condition. The STBC02 is enabled to operate in normal conditions again, only if the battery voltage is higher than  $V_{ODCR}$  (3 V). A deglitch delay is implemented to prevent unwanted false operations. The above-described WAKE-UP pin functionality is disabled when a valid VIN voltage source is detected. The pin has an internal 50 k $\Omega$  pull-down resistor.

DS11617 - Rev 5 page 15/35

### 6.11 CHG

Active low, open drain charging/fault flag output pin. The CHG provides status information about VIN voltage level, battery charging status and faults by toggling at different frequencies as reported in the table below.

Table 8. CHG pin state

| Device state                                                                                 | CHG pin state                     | Note                                                                                                                                  |

|----------------------------------------------------------------------------------------------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| Not valid input ( $V_{IN} < V_{BAT}$ or $V_{IN}$<br>> $V_{INOVP}$ or $V_{IN} < V_{INUVLO}$ ) | High Z (high by external pull-up) |                                                                                                                                       |

|                                                                                              | Low                               |                                                                                                                                       |

| V <sub>BAT</sub> < 1 V                                                                       | Low                               |                                                                                                                                       |

| End of charge (EOC)                                                                          | Toggling 4.1 Hz                   | In case of synchronous alarm events, the highest                                                                                      |

| End-of-charge (EOC)                                                                          | (until USB is disconnected)       | toggling frequency has higher priority.                                                                                               |

| Charging phase (pre and fast)                                                                | Toggling 6.2 Hz                   | Example: NTC warning and EOC are concurrent events. NTC warning, signaled by toggling CHG at                                          |

| Overcharge fault                                                                             | Toggling 8.2 Hz                   | 16.2 Hz is the only signal available till the battery                                                                                 |

| Charging timeout (pre-charge, fast charge)                                                   | Toggling 10.2 Hz                  | temperature goes back to a safe range (0 °C to 45 °C). If an EOC condition is still present then a 4.1 Hz toggling signal is present. |

| Battery voltage below V <sub>PRE</sub> after the fast charge starts                          | Toggling 12.8 Hz                  |                                                                                                                                       |

| Charging thermal limitation (thermal warning)                                                | Toggling 14.2 Hz                  |                                                                                                                                       |

| Battery temperature fault (NTC warning)                                                      | Toggling 16.2 Hz                  |                                                                                                                                       |

During temporary alarms if the Input Voltage is below the UVLO threshold, to reduce power consumption (battery powered) the internal oscillator frequency is reduced and CHG status output frequency is halved.

### 6.12 CEN

Internal CC/CV charger block enable pin. A low logic level on this pin disables the internal CC/CV charger block. Transitioning CEN from high to low and then back to high, allows the CC/CV charger block to be restarted if it was stopped due to one of the following conditions:

- Charging timeout (pre-charge, fast charge)

- Battery voltage below V<sub>PRE</sub> after the fast charge has already started

- End-of-charge

CEN has no effect if the charging cycle has been stopped by a battery overcharge condition.

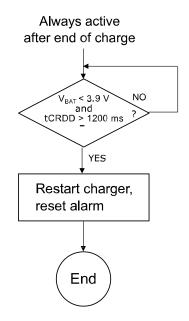

If the CC/CV charger stops the charging cycle due to an out of range battery temperature, a low logic level on the CEN pin disables the CC/CV charger and resets the charging timeout timers. If CEN is set high, the CC/CV charger restarts normal operations, assuming that no fault condition is detected. CEN is internally pulled up to LDO via a 500 k $\Omega$  resistor and must be either left floating or tied to LDO when the STBC02 is powered for the first time. Should the auto-recharge function be enabled, the CC/CV charger restarts automatically charging the battery if V<sub>BAT</sub> goes below 3.9 V; a deglitch time delay has been added to prevent unwanted charging cycle restarts.

### 6.13 RESET NOW (RESET CLEAR), nRESET, RST PENDING

The device features reset/watchdog circuits meant to be used in conjunction with the external application processor or with other embedded devices; it provides a reset signal or a watchdog expiration information. The reset signal and the watchdog timer expiration have no impact on the STBC02 operations.

DS11617 - Rev 5 page 16/35

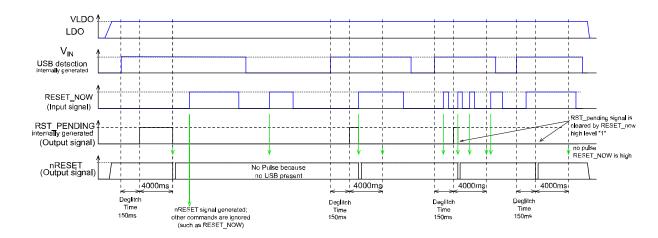

### 6.13.1 Smart reset section control pin

The smart reset circuit is active only when a valid  $V_{IN}$  is present ( $V_{UVLO} < V_{IN} < V_{INOVP}$ ). The STBC02 features a 150 ms deglitch time, starting from the valid  $V_{IN}$  detection, and it is meant to avoid false triggering due to signal bounces. After  $V_{IN}$  is considered to be valid and the deglitch time has expired, the RST\_PENDING signal goes to a high logic level. An nRESET signal is generated automatically after a 4000 ms delay, starting from the end of the deglitch time, or anytime earlier if a RESET\_NOW signal is applied. This is a sole event and no other nRESET signal is generated as long as  $V_{IN}$  is disconnected and reconnected again. The RST\_PENDING signal remains at a high logic level until when one of the two prior conditions is met. For more details refer to the following timing diagram.

Figure 19. Smart reset timing diagram

The nRESET pull-up resistor must be connected to LDO pin or to a higher voltage.

If not used, it is recommended both the nRESET and the RESET\_NOW pins are pulled down via a 100 k $\Omega$  resistor connected to GND.

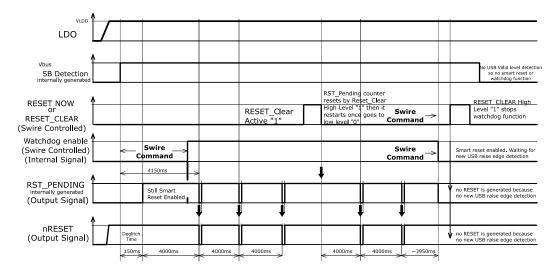

## 6.13.2 Watchdog section control pin

The watchdog functionality can be enabled or disabled by using SWIRE commands (#27 enabled, #26 disabled). If enabled by asserting the SWIRE command, the RESET\_CLEAR function, implemented using the RESET\_NOW pin, allows the nRESET pulses to be skipped when in a high logic level state.

It is recommended a proper RESET\_CLEAR signal is applied at least 100 µs before the next scheduled nReset transition to a low level (it occurs every 4000 ms).

Should the watchdog function be enabled at least after having detected a valid VIN plus a delay of 150 ms, an nRESET signal transitioning to a low level occurs after 4000 ms starting from the RST\_PENDING transitioning to a high level. To skip this nRESET pulse, a high level RESET\_CLEAR signal must be generated prior to (at least 100 µs) the expiration of the 4000 ms counter triggered by the RST\_PENDING transitioning to a high level.

The watchdog function can be disabled anytime through an SWIRE command (#26) and if so, the relevant circuit block goes back to the smart reset functionality default state. For more details refer to the following timing diagram.

The watchdog function works when the STBC02 is in battery mode too.

DS11617 - Rev 5 page 17/35

Figure 20. Watchdog timing diagram

## 6.14 SW1\_OA, SW1\_OB, SW1\_I, SW2\_OA, SW2\_OB, SW2\_I

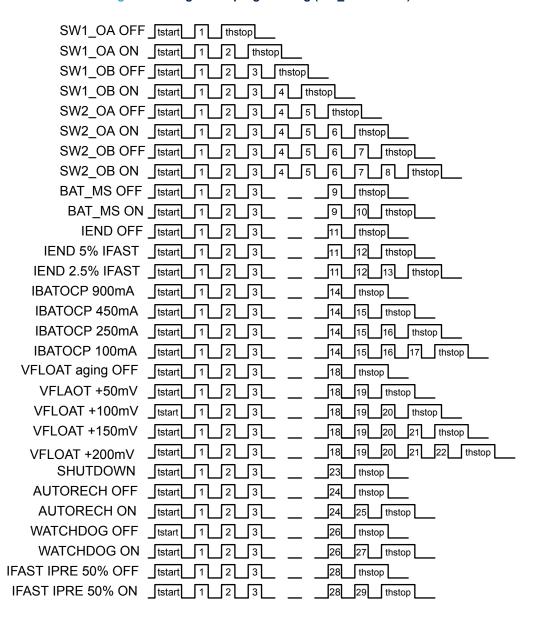

SPDT load switches pins. Both of SPDT load switches are controlled by an internal register, using the SWIRE interface. Each SPDT features a typical  $R_{DS(on)}$  of 3  $\Omega$ . SPDT load switches can be paralleled to reduce the series resistor as well as to increase the allowable flowing current.

## 6.15 SW\_SEL

SW\_SEL, serial SWIRE input pin. It is internally pulled down with a 500 k $\Omega$  resistor. In idle state the SW\_SEL pin must be held to ground. See table below for details.

| SW_SEL pulse<br>number | Function         | Status                                          | Note                                                                                                  |

|------------------------|------------------|-------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| Dower on               | SW1_OA, SW2_OA   | ON (default)                                    | SW1_I is connected with SW1_OA and SW2_I is connected with SW2_OA                                     |

| Power-on               | SW1_OB, SW2_OB   | OFF (default)                                   | SW1_OB and SW2_OB are in high impedance (Hi-Z)                                                        |

| 1                      | CIMA OA          | to OFF                                          |                                                                                                       |

| 2                      | SW1_OA           | to ON                                           |                                                                                                       |

| 3                      | SW1_OB           | to OFF                                          |                                                                                                       |

| 4                      |                  | to ON                                           |                                                                                                       |

| 5                      | SW2_OA           | to OFF                                          |                                                                                                       |

| 6                      |                  | to ON                                           |                                                                                                       |

| 7                      | SW2_OB           | to OFF                                          |                                                                                                       |

| 8                      |                  | to ON                                           |                                                                                                       |

| 9                      |                  | BATMS OFF                                       | Battery monitor switch (default value)                                                                |

| 10                     | 10 BATMS         | BATMS ON                                        | It increases battery leakage due to external resistor divider R <sub>DIV1</sub> , R <sub>DIV2</sub>   |

| 11                     |                  | I <sub>END</sub> OFF                            | It disables EOC (end-of-charge signal). Charger continues working even if I <sub>END</sub> is reached |

| 12                     | I <sub>END</sub> | I <sub>END</sub> 5% I <sub>FAST</sub> (default) | I <sub>END</sub> stops the charger phase (default)                                                    |

**Table 9. SWIRE programming**

DS11617 - Rev 5 page 18/35

| SW_SEL pulse<br>number | Function                                          | Status                                  | Note                                                                                                                                                                              |

|------------------------|---------------------------------------------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13                     | I <sub>END</sub>                                  | I <sub>END</sub> 2.5% I <sub>FAST</sub> | I <sub>END</sub> stops the charger phase                                                                                                                                          |

| 14                     |                                                   | 900 mA                                  | Overcurrent protection (battery discharge). Default value                                                                                                                         |

| 15                     | I <sub>BAT</sub> OCP                              | 450 mA                                  |                                                                                                                                                                                   |

| 16                     |                                                   | 250 mA                                  |                                                                                                                                                                                   |

| 17                     |                                                   | 100 mA                                  |                                                                                                                                                                                   |

| 18                     |                                                   | OFF                                     | Default value                                                                                                                                                                     |

| 19                     |                                                   | +50 mV                                  | V <sub>FLOAT</sub> increases 50 mV (whatever the programmed value is)                                                                                                             |

| 20                     | V <sub>FLOAT</sub> adjustment                     | +100 mV                                 | V <sub>FLOAT</sub> increases 100 mV (whatever the programmed value is)                                                                                                            |

| 21                     |                                                   | +150 mV                                 | V <sub>FLOAT</sub> increases 150 mV (whatever the programmed value is)                                                                                                            |

| 22                     |                                                   | +200 mV                                 | V <sub>FLOAT</sub> increases 200 mV (whatever the programmed value is)                                                                                                            |

| 23                     | Shipping mode                                     | ON                                      | Forces the device in shutdown (low power mode)                                                                                                                                    |

| 24                     |                                                   | OFF                                     | Default value                                                                                                                                                                     |

| 25                     | Auto-recharge                                     | ON                                      | Charger restart. After end-of-charge if battery voltage crosses V <sub>REC</sub> and t <sub>CRDD</sub> expires, another charging cycle starts automatically                       |

| 26                     |                                                   | OFF                                     | Smart reset (default)                                                                                                                                                             |

| 27                     | Watchdog                                          | ON                                      | Watchdog enabled. RESET_NOW becomes<br>RESET_CLEAR which allows recurring nRESET<br>pulses to be skipped                                                                          |

| 28                     |                                                   | OFF                                     | $I_{PRE}$ and $I_{FAST}$ current as programmed by $R_{PRE}$ and $R_{SET}$ resistors (default)                                                                                     |

| 29                     | I <sub>FAST</sub> and I <sub>PRE</sub> always 50% | ON                                      | Forces I <sub>FAST</sub> and I <sub>PRE</sub> currents to be 50% of the initial programmed value. In case of thermal warning, the internal logic temporarily forces this bit "ON" |

DS11617 - Rev 5 page 19/35

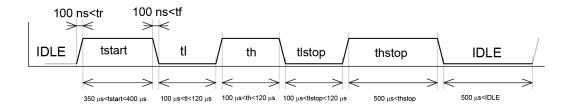

Figure 21. Single wire programming (SW\_SEL INPUT)

Figure 22. Start and stop timing bit range

Recommended SWIRE programming pulse width is 100  $\mu$ s minimum, 120  $\mu$ s maximum. Start bit timing ranges between 350  $\mu$ s and 400  $\mu$ s. Stop bit timing value  $\geq$  500  $\mu$ s.

DS11617 - Rev 5 page 20/35

# 7 Block diagram

Figure 23. STBC02 block diagram

DS11617 - Rev 5 page 21/35

## 8 Operation description

The STBC02 is a power management IC integrating a battery charger with an embedded power path function, a 150 mA low quiescent LDO, a smart reset/watchdog, two SPDT load switches and a protection circuit module (PCM) to prevent the battery from being damaged.

When powered off from a single-cell Li-lon or Li-Poly battery, and after having performed all the safety checks, the STBC02 starts charging the battery using a constant-current and constant-voltage algorithm.

The embedded power path allows simultaneously the battery to be charged and the overall system to be supplied. By contrast, when the input voltage is outside the above valid range, the battery supplies the LDO as well as every load connected to SYS.

The STBC02 also protects the battery in case of:

- Overcharge

- Over-discharge

- · Charge overcurrent

- Discharge overcurrent

If a fault condition is detected when the input voltage is valid (V<sub>UVLO</sub><V<sub>IN</sub><V<sub>INOVP</sub>), the CHG pin starts toggling, signaling the fault.

The device can also be in shutdown mode (shutdown I<sub>BAT</sub><100 nA) maximizing the battery life of the end-product during its shelf life.

### 8.1 Power-on

When the STBC02 is in shutdown mode, any load connected to LDO and to SYS is not supplied.

An applied valid input voltage ( $V_{UVLO} < V_{IN} < VI_{NOVP}$ ) for at least 250 ms, regardless the presence of a battery or if the battery is fully depleted, allows the loads connected to SYS and LDO to be supplied, thus enabling proper system operations.

The CEN pin must be left floating or tied high (LDO level) during the power-on for proper operations. The STBC02 can be also turned on when VIN is outside the valid range, below the conditions that the battery has at least a remaining charge of 3 V and the wake-up input is properly triggered. The STBC02 features an UVLO circuit that prevents oscillations if the input voltage source is unstable. The CEN pin must be left floating or tied to a high level (LDO) when the STBC02 is powered.

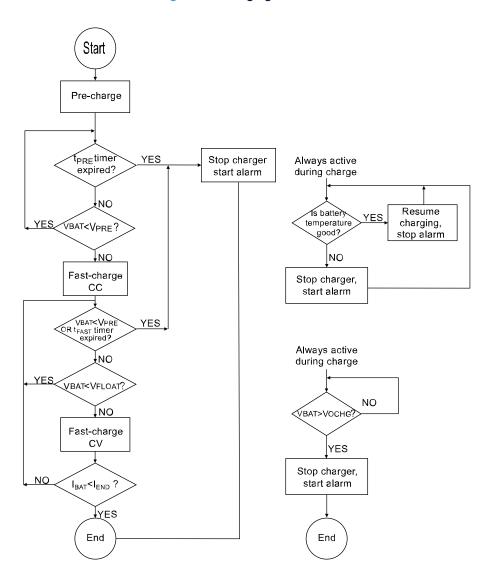

## 8.2 Battery charger

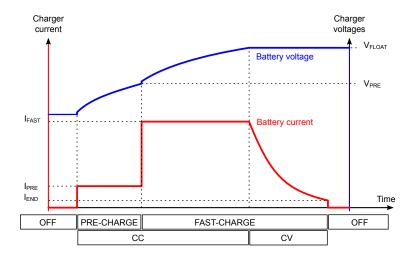

The STBC02 allows single-cell Li-Ion and Li-Poly battery chemistry to be charged up to a 4.45 V using a CC/CV charging algorithm. The charging cycle starts when a valid input voltage source ( $V_{UVLO} < V_{IN} < V_{INOVP}$ ) is detected and signaled by the CHG pin toggling from a high impedance state to a low logic level.

If the battery is deeply discharged (the battery voltage is lower than  $V_{PRE}$ ), the STBC02 charger enters the pre-charge phase and starts charging in constant-current mode with the pre-charge current ( $I_{PRE}$ ) set. In case the battery voltage does not reach the  $V_{PRE}$  threshold within the  $t_{PRE}$  time, the charging process is stopped and a fault is signaled.

By contrast, as soon as the battery voltage reaches the  $V_{PRE}$  threshold, the constant-current fast charge phase starts operating, and the relevant charging current increases to the  $I_{FAST}$  level.

Likewise, if the constant current fast charge phase is not completed within  $t_{FAST}$ , meaning that  $V_{BAT} < V_{FLOAT}$ , the charging process is stopped and a fault is signaled (CHG starts toggling at 10.2 Hz as long as a valid  $V_{IN}$  is present).

Should the battery voltage decrease below  $V_{PRE}$  during the fast charge phase, the charging process is halted and a fault is signaled. The constant-current fast charge phase lasts until the battery voltage is lower than  $V_{FLOAT}$ . After that, the charging algorithm switches to a constant-voltage (CV) mode.

During the CV mode, the battery voltage is regulated to  $V_{FLOAT}$  and the charging current starts decreasing over time. As soon as it goes below  $I_{END}$ , the charging process is considered to be completed (EOC, end-of-charge) and the relevant status is signaled via a 4.1 Hz toggling signal on the CHG pin, again as long as a there is a valid input source applied ( $V_{UVLO} < V_{IN} < V_{INOVP}$ ).

Both  $I_{PRE}$  and the  $I_{FAST}$  values can be programmed from 1 mA to 450 mA via an external resistor, as described in the ISET pin description.

DS11617 - Rev 5 page 22/35

**Battery charger**

For any  $I_{FAST}$  programmed value above 20 mA, the  $I_{END}$  value can be set either 5% or 2.5% of the IFAST level. For any  $I_{FAST}$  programmed value below 20 mA, the relevant  $I_{END}$  value is set as per the following table:

Table 10. I<sub>FAST</sub> and I<sub>END</sub>

| I <sub>FAST</sub> | I <sub>END</sub> |

|-------------------|------------------|

| 20 mA             | 1.7 mA           |

| 10 mA             | 1.1 mA           |

| 5 mA              | 0.65 mA          |

| 2 mA              | 0.4 mA           |

| 1 mA              | 0.2 mA           |

The battery temperature is monitored throughout the charging cycle for safety reasons.

Figure 24. Charging flowchart

DS11617 - Rev 5 page 23/35

### Actions:

- Pre-charge starts t<sub>PRE</sub> timer; starts charging in CC mode at I<sub>PRE</sub>

- Fast-charge CC starts t<sub>FAST</sub> timer, increases charge current to I<sub>FAST</sub>

- Fast-charge CV activates the constant-voltage control loop

- Start alarm: the CHG pin starts toggling

Figure 25. End-of-charge flowchart

Figure 26. CC/CV charging profile (not in scale)

DS11617 - Rev 5 page 24/35

## 8.3 Battery temperature monitoring

The STBC02 integrates all the needed blocks to monitor the battery temperature through an external NTC resistor. The battery temperature monitoring is enabled only during the battery charging process, in order to save power when the system is supplied from the battery.

When the battery temperature is outside the normal operating range (0-45 °C), the charging process is halted, an alarm signal is activated (the CHG pin toggles at 16.2 Hz) but the charging timeout timers are not stopped.

If the temperature goes back to the normal operating range, before the maximum charging time has elapsed, the charging process is resumed and the alarm signal is cleared.

In case of the charging timeout expires and the temperature is still outside the normal operating range, the charging process is stopped but it can be still restarted using the CEN pin.

Both temperature thresholds feature a 3 °C hysteresis. The battery temperature monitoring block is designed to work with an NTC thermistor having  $R_{25}$  = 10 k $\Omega$  and  $\Omega$  = 3370 (Mitsubishi TH05-3H103F). If an NTC thermistor is not used, 10 k $\Omega$  resistor must be connected to ensure the proper IC operation.

## 8.4 Battery overcharge protection

The battery overcharge protection is a safety feature, active when a valid input voltage is connected, preventing the battery voltage from exceeding a  $V_{OCHG}$  value. Should an overcharge condition be detected, the current path from the input to the battery is opened and a fault signal is activated (the CHG pin toggles at 8.2 Hz). When the battery voltage goes below  $V_{OCHG}$ , normal operations can only be restarted by disconnecting and connecting back again the input voltage (VIN).

### 8.5 Battery over-discharge protection

The battery over-discharge protection is a safety feature enabled only when no valid input voltage source ( $V_{UVLO} < V_{IN} < V_{INOVP}$ ) is detected. Therefore, when the STBC02 and the system are powered off from the battery, an over-discharge of the battery itself is avoided. Should the battery voltage level be below  $V_{ODC}$  for more than  $t_{ODD}$  (over-discharge state), the STBC02 turns off and current sunk from the battery is reduced to less than 50 nA. When a valid input voltage source is detected, while the battery is in an over-discharge state, the STBC02 charger, SYS and LDO outputs are enabled. This condition persists until the battery voltage has exceeded the over-discharge released threshold ( $V_{ODCR}$ ), otherwise any other disconnection of a valid input voltage source brings back the STBC02 to a battery over-discharge state.

### 8.6 Battery discharge overcurrent protection

When the STBC02 is powered off from the battery connected to the BAT pin, a discharge overcurrent protection circuit disables the STBC02 if the current sunk from the battery is in excess of  $I_{BATOCP}$  (whose value is programmable via SWIRE) for more than  $t_{DOD}$ .

The presence of a valid input voltage source or triggering the WAKE-UP input pin, allows normal operating conditions to be restored.

## 8.7 Battery fault protection

The STBC02 features a battery fault protection. The STBC02 charger is stopped if the battery voltage remains below 1 V for at least 16 seconds.

### 8.8 Floating voltage adjustment

The STBC02 features a floating voltage adjustment, controlled via SWIRE, allowing the battery floating voltage (four steps of 50 mV each) to be changed. Due to multiple battery charging processes and the aging of the battery, the floating voltage of the battery can change and be reduced. The floating voltage adjustment feature brings the floating voltage level back to the original nominal value. For safety reasons, the battery voltage overcharge threshold level ( $V_{\rm OCHG}$ ) is linked to any floating voltage set. By default this feature is disabled and moreover, as no state is stored in any memory, every shutdown or shipping mode event resets the floating voltage at the default value.

DS11617 - Rev 5 page 25/35

## 8.9 Input overcurrent protection