## Precision, 40 V, ±70 nV/°C, Rail-to-Rail Input and Output Op Amp with DigiTrim

## **FEATURES**

- ▶ Low offset voltage drift: ±70 nV/°C typical

- ▶ Low offset voltage: ±5 μV typical, ±20 μV maximum

- Low voltage noise: 1 μV p-p from 0.1 Hz to 10 Hz typical

- ▶ Low voltage noise density: 5 nV/ $\sqrt{Hz}$  typical at f = 1 kHz

- ▶ High common-mode rejection: 140 dB typical

- ▶ Low input bias current: ±10 pA maximum

- ▶ Wide gain bandwidth product: 10.4 MHz typical

- ▶ High slew rate: 19 V/µs typical

- ▶ Low THD: -134 dB at f = 1 kHz

- ▶ Low quiescent supply current: 1.45 mA per amplifier typical

- ▶ Wide supply voltage operation: 6 V to 40 V, ±3 V to ±20 V

- Integrated EMI filter

- ► Multiplexer compatible inputs

- Rail-to-rail high impedance inputs: differential and commonmode

- ▶ Fast settling time

- ▶ Rail-to-rail output

- ▶ No phase reversal

- Heavy capacitive load drive capability: 1 nF

- ▶ Wide specified temperature range: -40°C to +125°C

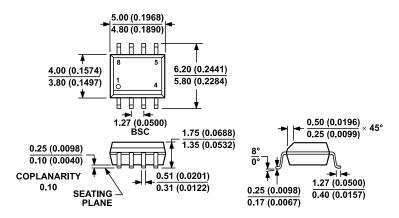

- Available in 8-lead standard small outline package (SOIC N)

#### **APPLICATIONS**

- Electronic test and measurement

- ▶ Data acquisition systems

- Automated test equipment

- Medical instruments

- Multiplexed input signal chains

- ▶ Precision current measurement

- Photodiode amplifiers

## **GENERAL DESCRIPTION**

The ADA4510-2<sup>1</sup> is a dual-channel, 40 V, high precision, low input bias current, low offset voltage, low offset voltage drift, low noise, rail-to-rail input and output operational amplifier that can be used at any point of the signal chain, including sensing, conditioning, and output drive. Through the use of Analog Devices, Inc., proprietary DigiTrim technique, the ADA4510-2 achieves best-in-class low offset drift ( $\pm 70$  nV/°C typical,  $\pm 500$  nV/°C maximum) and low offset voltage ( $\pm 5~\mu V$  typical,  $\pm 20~\mu V$  maximum), simplifying temperature calibrations in precision designs.

The ADA4510-2 delivers excellent DC precision and outstanding AC performance, making it a top choice for a wide variety of signal chain applications. By integrating a robust mux-compatible architecture, the ADA4510-2 effectively solves common system distortion and settling problems and provides the superior accuracy required in multiplexed multichannel precision signal chains. The ADA4510-2 is specified from -40°C to +85°C and -40°C to +125°C and is available in an 8-lead, SOIC N.

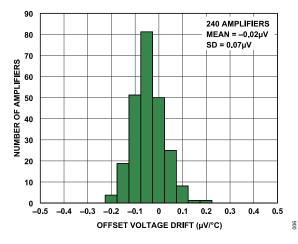

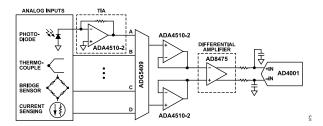

Figure 1. Ultralow Offset Voltage Drift for Precision Design

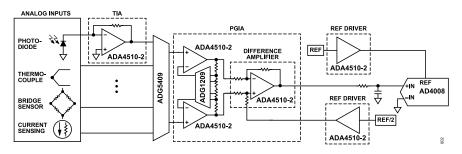

### TYPICAL APPLICATION CIRCUIT

Figure 2. Multiplexed Data Acquisition Signal Chain

Rev. A

Information furnished by Analog Devices is believed to be accurate and reliable "as is". However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

Protected by U.S. patent number 11,329,612; other patents pending.

**Data Sheet**

## **TABLE OF CONTENTS**

| Features 1                                                              | Input and Gain Stages                  | 22 |

|-------------------------------------------------------------------------|----------------------------------------|----|

| Applications1                                                           | Output Stage                           |    |

| General Description1                                                    | EMI Rejection                          |    |

| Typical Application Circuit1                                            | No Phase Inversion                     | 22 |

| Companion Products3                                                     | Capacitive Load Drive Capability       |    |

| Specifications4                                                         | Applications Information               | 24 |

| Electrical Specifications for T <sub>A</sub> = -40°C to                 | Mux-Compatible Data Acquisition System |    |

| +85°C4                                                                  | Transimpedance Amplifier               |    |

| Electrical Specifications for $T_A = -40^{\circ}C$ to                   | Active Filter                          |    |

| +125°C6                                                                 | Feedback Components                    |    |

| Absolute Maximum Ratings8                                               | Precision Buffer                       |    |

| Thermal Resistance8                                                     | Recommended Power Solution             | 28 |

| Electrostatic Discharge (ESD) Ratings8                                  | Layout Guidelines                      | 28 |

| ESD Caution8                                                            | Outline Dimensions                     |    |

| Pin Configuration and Function Descriptions 9                           | Ordering Guide                         | 29 |

| Typical Performance Characteristics10                                   | Evaluation Boards                      | 29 |

| Theory of Operation                                                     |                                        |    |

| REVISION HISTORY                                                        |                                        |    |

| 10/2023—Rev. 0 to Rev. A                                                |                                        |    |

| Changes to Data Sheet Title                                             |                                        | 1  |

| Changes to Features Section                                             |                                        | 1  |

| Changes to General Description Section                                  |                                        |    |

| Changes to Offset Voltage Drift ( $\Delta V_{OS}/\Delta T$ ) Parameter, |                                        |    |

| Changes to Figure 65                                                    |                                        | 20 |

| Change to Design Example Section                                        |                                        | 24 |

7/2023—Revision 0: Initial Version

analog.com Rev. A | 2 of 29

## **COMPANION PRODUCTS**

► ADC: AD4695/AD4696, AD4697/AD4698, AD4002/AD4006/ AD4010, AD4000/AD4004/AD4008

ADC Drivers: ADA4945-1, LTC6363, AD8475

Voltage References: LTC6655, ADR4525

Power: LT3032, ADP5070, LT3093, LT3042

analog.com Rev. A | 3 of 29

## **SPECIFICATIONS**

# ELECTRICAL SPECIFICATIONS FOR $T_A = -40^{\circ}C$ TO +85°C

Supply voltage  $(V_{SY}) = (V+) - (V-) = \pm 3 \text{ V}$  to  $\pm 20 \text{ V}$ , common-mode voltage  $(V_{CM}) = 0 \text{ V}$ , load resistor  $(R_L) = 10 \text{ k}\Omega$  to midsupply, unless otherwise noted.

Table 1. Electrical Specifications for  $T_A = -40$ °C to +85°C

| Parameter                                   | Test Conditions/Comments                                                                                          | Min        | Тур   | Max   | Unit   |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------|------------|-------|-------|--------|

| NPUT CHARACTERISTICS                        |                                                                                                                   |            |       |       |        |

| Offset Voltage (V <sub>OS</sub> )           | V <sub>CM</sub> = 0 V, T <sub>A</sub> = 25°C                                                                      |            | ±5    | ±20   | μV     |

|                                             | 0°C < T <sub>A</sub> < +85°C                                                                                      |            |       | ±40   | μV     |

|                                             | -40°C < T <sub>A</sub> < +85°C                                                                                    |            |       | ±50   | μV     |

|                                             | $V_{CM} = (V+) - 1.5 V, T_A = 25^{\circ}C$                                                                        |            | ±10   | ±40   | μV     |

|                                             | 0°C < T <sub>A</sub> < +85°C                                                                                      |            |       | ±60   | μV     |

|                                             | -40°C < T <sub>A</sub> < +85°C                                                                                    |            |       | ±120  | μV     |

|                                             | $V_{CM} = (V-) - 0.15 \text{ V}, T_A = 25^{\circ}\text{C}$                                                        |            | ±8    | ±35   | μV     |

|                                             | 0°C < T <sub>A</sub> < +85°C                                                                                      |            |       | ±90   | μV     |

|                                             | -40°C < T <sub>A</sub> < +85°C                                                                                    |            |       | ±110  | μV     |

| Offset Voltage Drift (ΔV <sub>OS</sub> /ΔT) | V <sub>CM</sub> = 0 V                                                                                             |            |       |       |        |

|                                             | $0^{\circ}\text{C} < \text{T}_{A} < +85^{\circ}\text{C}$                                                          |            | ±70   | ±500  | nV/°C  |

|                                             | -40°C < T <sub>A</sub> < +85°C                                                                                    |            | ±0.12 | ±0.5  | μV/°C  |

|                                             | $V_{CM} = (V+) - 1.5 V$                                                                                           |            |       |       |        |

|                                             | 0°C < T <sub>A</sub> < +85°C                                                                                      |            | ±0.1  | ±0.7  | μV/°C  |

|                                             | -40°C < T <sub>A</sub> < +85°C                                                                                    |            | ±0.15 | ±1    | μV/°C  |

| Input Bias Current (I <sub>B</sub> )        | T <sub>A</sub> = 25°C                                                                                             |            | ±2.5  | ±10   | pA     |

|                                             | -40°C < T <sub>A</sub> < +85°C                                                                                    |            |       | ±0.8  | nA     |

| Input Offset Current (I <sub>OS</sub> )     | T <sub>A</sub> = 25°C                                                                                             |            | ±0.5  | ±5    | pА     |

| , , , , , , , , , , , , , , , , , , , ,     | -40°C < T <sub>A</sub> < +85°C                                                                                    |            |       | ±0.15 | nA     |

| Input Voltage Range (IVR)                   | Guaranteed by CMRR                                                                                                | (V−) − 0.1 | 5     | V+    | V      |

| Common-Mode Rejection Ratio (CMRR)          | $(V-) - 0.15 V < V_{CM} < (V+) - 3 V, T_A = 25^{\circ}C$                                                          | 121        | 140   |       | dB     |

|                                             | -40°C < T <sub>A</sub> < +85°C                                                                                    | 118        |       |       | dB     |

|                                             | (V−) − 0.15 V < V <sub>CM</sub> < V+, T <sub>A</sub> = 25°C                                                       | 100        | 112   |       | dB     |

|                                             | -40°C < T <sub>A</sub> < +85°C                                                                                    | 100        |       |       | dB     |

| Open-Loop Voltage Gain (A <sub>VOL</sub> )  | $R_L = 10 \text{ k}\Omega$ , $(V-) + 0.3 \text{ V} < V_{OUT} < (V+) - 0.3 \text{ V}$ , $T_A = 25^{\circ}\text{C}$ | 126        | 140   |       | dB     |

|                                             | -40°C < T <sub>A</sub> < +85°C                                                                                    | 124        |       |       | dB     |

|                                             | $R_L = 2 k\Omega$ , $(V-) + 0.9 V < V_{OUT} < (V+) - 0.9 V$ , $T_A = 25$ °C                                       | 121        | 134   |       | dB     |

|                                             | -40°C < T <sub>A</sub> < +85°C                                                                                    | 120        |       |       | dB     |

| Input Capacitance                           |                                                                                                                   |            |       |       |        |

| Differential Mode (C <sub>INDM</sub> )      | T <sub>A</sub> = 25°C                                                                                             |            | 20    |       | pF     |

| Common Mode (C <sub>INCM</sub> )            | $T_A = 25^{\circ}C$ , $V_{SY} = \pm 5 \text{ V to } \pm 20 \text{ V}$                                             |            | 2     |       | pF     |

| Input Resistance                            |                                                                                                                   |            |       |       |        |

| Differential Mode (R <sub>INDM</sub> )      | T <sub>A</sub> = 25°C                                                                                             |            | 1     |       | ΤΩ     |

| Common Mode (R <sub>INCM</sub> )            | T <sub>A</sub> = 25°C                                                                                             |            | 10    |       | ΤΩ     |

| IOISE PERFORMANCE                           |                                                                                                                   |            |       |       |        |

| Voltage Noise (e <sub>n p-p</sub> )         | 0.1 Hz to 10 Hz, T <sub>A</sub> = 25°C                                                                            |            | 1     |       | μV p-p |

| <b>5</b> ( 11 p p)                          | 0.1 Hz to 10 Hz, V <sub>CM</sub> = (V+) - 1.5 V, T <sub>A</sub> = 25°C                                            |            | 2.7   |       | μV p-p |

| Voltage Noise Density (e <sub>n</sub> )     | f = 100 Hz, T <sub>A</sub> = 25°C                                                                                 |            | 8     |       | nV/√Hz |

| J (-11)                                     | f = 1 kHz, T <sub>A</sub> = 25°C                                                                                  |            | 5     |       | nV/√Hz |

|                                             | f = 100 Hz, V <sub>CM</sub> = (V+) - 1.5 V, T <sub>A</sub> = 25°C                                                 |            | 20    |       | nV/√Hz |

|                                             | $f = 1 \text{ kHz}, V_{CM} = (V+) - 1.5 \text{ V}, T_A = 25^{\circ}\text{C}$                                      |            | 10    |       | nV/√Hz |

| Current Noise Density (I <sub>n</sub> )     | f = 10 Hz, T <sub>A</sub> = 25°C                                                                                  |            | 4     |       | fA/√Hz |

analog.com Rev. A | 4 of 29

## **SPECIFICATIONS**

Table 1. Electrical Specifications for  $T_A = -40^{\circ}\text{C}$  to +85°C (Continued)

| Parameter                                               | Test Conditions/Comments                                                                                                           | Min | Тур     | Max  | Unit |

|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----|---------|------|------|

| OUTPUT CHARACTERISTICS                                  |                                                                                                                                    |     |         |      |      |

| Output Swing High (V <sub>OH</sub> )                    | ((V+) - V <sub>OUT</sub> )                                                                                                         |     |         |      |      |

|                                                         | $R_L = 10 \text{ k}\Omega, T_A = 25^{\circ}\text{C}$                                                                               |     | 100     | 116  | mV   |

|                                                         | -40°C < T <sub>A</sub> < +85°C                                                                                                     |     |         | 160  | mV   |

|                                                         | $R_L = 2 k\Omega$ , $T_A = 25$ °C                                                                                                  |     | 430     | 473  | mV   |

|                                                         | -40°C < T <sub>A</sub> < +85°C                                                                                                     |     |         | 655  | mV   |

| Output Swing Low (V <sub>OL</sub> )                     | (V <sub>OUT</sub> - (V-))                                                                                                          |     |         |      |      |

|                                                         | R <sub>L</sub> = 10 kΩ, T <sub>A</sub> = 25°C                                                                                      |     | 73      | 85   | mV   |

|                                                         | -40°C < T <sub>A</sub> < +85°C                                                                                                     |     |         | 120  | mV   |

|                                                         | $R_1 = 2 k\Omega, T_A = 25^{\circ}C$                                                                                               |     | 310     | 342  | mV   |

|                                                         | -40°C < T <sub>A</sub> < +85°C                                                                                                     |     |         | 487  | mV   |

| Output Current (I <sub>OUT</sub> )                      | $(V_{OH}, V_{OL}) < 1 \text{ V}, T_A = 25^{\circ}\text{C}$                                                                         |     | ±22     |      | mA   |

| Short-Circuit Current (I <sub>SC</sub> )                | Sourcing/sinking, T <sub>A</sub> = 25°C                                                                                            |     | 55/70   |      | mA   |

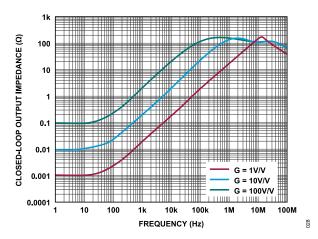

| Closed-Loop Output Impedance (Z <sub>OUT</sub> )        | f = 1 kHz , T <sub>A</sub> = 25°C                                                                                                  |     |         |      |      |

| 1 - 1 1 ( 001)                                          | Gain = 1                                                                                                                           |     | 19      |      | mΩ   |

|                                                         | Gain = 10                                                                                                                          |     | 190     |      | mΩ   |

|                                                         | Gain = 100                                                                                                                         |     | 1.9     |      | Ω    |

| Open-Loop Output Impedance (Z <sub>O</sub> )            | f = 1 kHz to 1 MHz, T <sub>A</sub> = 25°C                                                                                          |     | 190     |      | Ω    |

| POWER SUPPLY                                            | T   N   12   10   T   N   12   12   13   14   15   15   15   15   15   15   15                                                     |     | 100     |      | 32   |

| V <sub>SY</sub> ((V+) - (V-))                           | Guaranteed by PSRR                                                                                                                 | 6   |         | 40   | V    |

| Power Supply Rejection Ratio (PSRR)                     | $V_{SY} = \pm 3 \text{ V to } \pm 20 \text{ V}, T_A = 25^{\circ}\text{C}$                                                          | 121 | 140     | 40   | dB   |

| Tower ouppry rejection read (Forty)                     | -40°C < T <sub>A</sub> < +85°C                                                                                                     | 117 | 170     |      | dB   |

| Supply Current per Amplifier (I <sub>SY</sub> )         | I <sub>OUT</sub> = 0 mA, T <sub>A</sub> = 25°C                                                                                     | 117 | 1.45    | 1.55 | mA   |

| Supply Current per Ampliner (ISY)                       | -40°C < T <sub>A</sub> < +85°C                                                                                                     |     | 1.43    | 1.85 | mA   |

| DYNAMIC PERFORMANCE                                     | -40 C \ 1A \ +00 C                                                                                                                 |     |         | 1.00 | IIIA |

|                                                         | // - 15 // gain = 11 100/ to 000/ T = 25°C                                                                                         |     | 10      |      | Muo  |

| Slew Rate                                               | V <sub>OUT</sub> = ±5 V, gain = +1, 10% to 90%, T <sub>A</sub> = 25°C                                                              |     | 19      |      | V/µs |

| Gain Bandwidth Product (GBP)                            | f = 100 kHz, T <sub>A</sub> = 25°C                                                                                                 |     | 10.4    |      | MHz  |

| -3 dB Bandwidth                                         | Gain = 1, T <sub>A</sub> = 25°C                                                                                                    |     | 13.5    |      | MHz  |

| Settling Time (t <sub>S</sub> )                         | T <sub>A</sub> = 25°C                                                                                                              |     |         |      |      |

|                                                         | To 0.01%                                                                                                                           |     | 4.0     |      |      |

|                                                         | Gain = $-1$ , $V_{OUT} = 5$ V step                                                                                                 |     | 1.9     |      | μs   |

|                                                         | Gain = -1, V <sub>OUT</sub> = 10 V step                                                                                            |     | 2.2     |      | μs   |

|                                                         | To 0.001%                                                                                                                          |     |         |      |      |

|                                                         | Gain = -1, V <sub>OUT</sub> = 5 V step                                                                                             |     | 3.1     |      | μs   |

|                                                         | Gain = −1, V <sub>OUT</sub> = 10 V step                                                                                            |     | 3.5     |      | μs   |

| Output Overload Recovery Time                           | Gain = −10, T <sub>A</sub> = 25°C, positive/negative                                                                               |     | 300/100 |      | ns   |

| Total Harmonic Distortion (THD)                         | V <sub>OUT</sub> = 10 V p-p, gain = 1, T <sub>A</sub> = 25°C                                                                       |     |         |      |      |

|                                                         | f = 1 kHz                                                                                                                          |     | 0.00002 |      | %    |

|                                                         | f = 1 kHz                                                                                                                          |     | -134    |      | dB   |

|                                                         | f = 50 kHz                                                                                                                         |     | 0.0045  |      | %    |

|                                                         | f = 50 kHz                                                                                                                         |     | -87     |      | dB   |

| ELECTROMAGNETIC INTERFERENCE<br>REJECTION RATIO (EMIRR) | EMIRR = $20 \times \log_{10}(\Delta V_{IN}/\Delta V_{OS})$ , $\Delta V_{IN}$ = $200 \text{ mV p-p}$ , $T_A$ = $25^{\circ}\text{C}$ |     |         |      |      |

|                                                         | f = 1000 MHz                                                                                                                       |     | 71      |      | dB   |

|                                                         | f = 2400 MHz                                                                                                                       |     | 81      |      | dB   |

| CROSSTALK                                               | V <sub>IN</sub> = 4 V p-p, T <sub>A</sub> = 25°C                                                                                   |     |         |      |      |

|                                                         | DC                                                                                                                                 |     | 165     |      | dB   |

|                                                         | f = 1 kHz                                                                                                                          |     | 164     |      | dB   |

|                                                         | f = 100 kHz                                                                                                                        |     | 130     |      | dB   |

analog.com Rev. A | 5 of 29

## **SPECIFICATIONS**

# ELECTRICAL SPECIFICATIONS FOR $T_A = -40^{\circ}C$ TO +125°C

Supply voltage  $(V_{SY}) = (V+) - (V-) = \pm 3 \text{ V}$  to  $\pm 20 \text{ V}$ , common-mode voltage  $(V_{CM}) = 0 \text{ V}$ , load resistor  $(R_L) = 10 \text{ k}\Omega$  to midsupply, unless otherwise noted.

Table 2. Electrical Specifications for  $T_A = -40$ °C to +125°C

| Parameter                                   | Test Conditions/Comments                                                                                          | Min | Тур   | Max  | Unit   |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-----|-------|------|--------|

| INPUT CHARACTERISTICS                       |                                                                                                                   |     |       |      |        |

| Offset Voltage (V <sub>OS</sub> )           | V <sub>CM</sub> = 0 V, T <sub>A</sub> = 25°C                                                                      |     | ±5    | ±20  | μV     |

|                                             | -40°C < T <sub>A</sub> < +125°C                                                                                   |     |       | ±100 | μV     |

|                                             | $V_{CM} = (V+) - 1.5 \text{ V}, T_A = 25^{\circ}\text{C}$                                                         |     | ±10   | ±40  | μV     |

|                                             | -40°C < T <sub>A</sub> < +125°C                                                                                   |     |       | ±380 | μV     |

|                                             | V <sub>CM</sub> = V-, T <sub>A</sub> = 25°C                                                                       |     | ±9    | ±35  | μV     |

|                                             | -40°C < T <sub>A</sub> < +125°C                                                                                   |     |       | ±160 | μV     |

| Offset Voltage Drift (ΔV <sub>OS</sub> /ΔT) | V <sub>CM</sub> = 0 V                                                                                             |     |       |      |        |

|                                             | -40°C < T <sub>A</sub> < +125°C                                                                                   |     | ±0.12 | ±0.7 | μV/°C  |

|                                             | V <sub>CM</sub> = (V+) - 1.5 V                                                                                    |     |       |      |        |

|                                             | -40°C < T <sub>A</sub> < +125°C                                                                                   |     | ±0.5  | ±2.4 | μV/°C  |

| Input Bias Current (I <sub>B</sub> )        | T <sub>A</sub> = 25°C                                                                                             |     | ±2.5  | ±10  | pA     |

| . (5)                                       | -40°C < T <sub>A</sub> < +125°C                                                                                   |     |       | ±18  | nA     |

| Input Offset Current (I <sub>OS</sub> )     | T <sub>A</sub> = 25°C                                                                                             |     | ±0.5  | ±5   | pA     |

| ( 00)                                       | -40°C < T <sub>A</sub> < +125°C                                                                                   |     |       | ±5   | nA     |

| Input Voltage Range (IVR)                   | Guaranteed by CMRR                                                                                                | V-  |       | V+   | V      |

| Common-Mode Rejection Ratio (CMRR)          | $V- < V_{CM} < (V+) - 3 V, T_A = 25^{\circ}C$                                                                     | 121 | 140   |      | dB     |

| ,                                           | -40°C < T <sub>A</sub> < +125°C                                                                                   | 109 |       |      | dB     |

|                                             | V- < V <sub>CM</sub> < V+, T <sub>A</sub> = 25°C                                                                  | 100 | 112   |      | dB     |

|                                             | -40°C < T <sub>A</sub> < +125°C                                                                                   | 95  |       |      | dB     |

| Open-Loop Voltage Gain (A <sub>VOL</sub> )  | $R_L = 10 \text{ k}\Omega$ , $(V-) + 0.3 \text{ V} < V_{OUT} < (V+) - 0.3 \text{ V}$ , $T_A = 25^{\circ}\text{C}$ | 126 | 140   |      | dB     |

|                                             | -40°C < T <sub>A</sub> < +125°C                                                                                   | 112 |       |      | dB     |

|                                             | $R_L = 2 k\Omega$ , $(V-) + 0.9 V < V_{OUT} < (V+) - 0.9 V$ , $T_A = 25 °C$                                       | 121 | 134   |      | dB     |

|                                             | -40°C < T <sub>A</sub> < +125°C                                                                                   | 106 |       |      | dB     |

| Input Capacitance                           |                                                                                                                   |     |       |      |        |

| Differential Mode (C <sub>INDM</sub> )      | T <sub>A</sub> = 25°C                                                                                             |     | 20    |      | pF     |

| Common Mode (C <sub>INCM</sub> )            | $T_A = 25^{\circ}\text{C}, V_{SY} = \pm 5 \text{ V to } \pm 20 \text{ V}$                                         |     | 2     |      | pF     |

| Input Resistance                            |                                                                                                                   |     |       |      | '      |

| Differential Mode (R <sub>INDM</sub> )      | T <sub>A</sub> = 25°C                                                                                             |     | 1     |      | ΤΩ     |

| Common Mode (R <sub>INCM</sub> )            | T <sub>A</sub> = 25°C                                                                                             |     | 10    |      | ΤΩ     |

| OISE PERFORMANCE                            |                                                                                                                   |     |       |      |        |

| Voltage Noise (e <sub>n p-p</sub> )         | 0.1 Hz to 10 Hz, T <sub>A</sub> = 25°C                                                                            |     | 1     |      | μV p-p |

| <b>5</b> ( 11 p p)                          | 0.1 Hz to 10 Hz, V <sub>CM</sub> = (V+) - 1.5 V, T <sub>A</sub> = 25°C                                            |     | 2.7   |      | μV p-p |

| Voltage Noise Density (e <sub>n</sub> )     | f = 100 Hz, T <sub>A</sub> = 25°C                                                                                 |     | 8     |      | nV/√Hz |

| 3 7 ( 11)                                   | f = 1 kHz, T <sub>A</sub> = 25°C                                                                                  |     | 5     |      | nV/√Hz |

|                                             | f = 100 Hz, V <sub>CM</sub> = (V+) - 1.5 V, T <sub>A</sub> = 25°C                                                 |     | 20    |      | nV/√Hz |

|                                             | f = 1 kHz, V <sub>CM</sub> = (V+) - 1.5 V, T <sub>A</sub> = 25°C                                                  |     | 10    |      | nV/√Hz |

| Current Noise Density (In)                  | f = 10 Hz, T <sub>A</sub> = 25°C                                                                                  |     | 4     |      | fA/√Hz |

| OUTPUT CHARACTERISTICS                      | , n                                                                                                               |     |       |      |        |

| Output Swing High (V <sub>OH</sub> )        | ((V+) - V <sub>OUT</sub> )                                                                                        |     |       |      |        |

|                                             | $R_L = 10 \text{ k}\Omega, T_A = 25^{\circ}\text{C}$                                                              |     | 100   | 116  | mV     |

|                                             | $-40^{\circ}\text{C} < T_A < +125^{\circ}\text{C}$                                                                |     | 100   | 187  | mV     |

|                                             | $R_L = 2 k\Omega, T_A = 25^{\circ}C$                                                                              |     | 430   | 473  | mV     |

|                                             | INL - 2 1/32, IA - 20 O                                                                                           |     | 730   | 713  | IIIV   |

analog.com Rev. A | 6 of 29

## **SPECIFICATIONS**

Table 2. Electrical Specifications for  $T_A = -40^{\circ}\text{C}$  to +125°C (Continued)

| Parameter                                               | Test Conditions/Comments                                                                                                                 | Min | Тур     | Max  | Unit |

|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-----|---------|------|------|

|                                                         | -40°C < T <sub>A</sub> < +125°C                                                                                                          |     |         | 765  | mV   |

| Output Swing Low (V <sub>OL</sub> )                     | (V <sub>OUT</sub> - (V-))                                                                                                                |     |         |      |      |

|                                                         | $R_L = 10 \text{ k}\Omega, T_A = 25^{\circ}\text{C}$                                                                                     |     | 73      | 85   | mV   |

|                                                         | -40°C < T <sub>A</sub> < +125°C                                                                                                          |     |         | 142  | mV   |

|                                                         | $R_L = 2 k\Omega$ , $T_A = 25$ °C                                                                                                        |     | 310     | 342  | mV   |

|                                                         | -40°C < T <sub>A</sub> < +125°C                                                                                                          |     |         | 573  | mV   |

| Output Current (I <sub>OUT</sub> )                      | $(V_{OH}, V_{OL}) < 1 \text{ V}, T_A = 25^{\circ}\text{C}$                                                                               |     | ±22     |      | mA   |

| Short-Circuit Current (I <sub>SC</sub> )                | Sourcing/sinking, T <sub>A</sub> = 25°C                                                                                                  |     | 55/70   |      | mA   |

| Closed-Loop Output Impedance (Z <sub>OUT</sub> )        | f = 1 kHz , T <sub>A</sub> = 25°C                                                                                                        |     |         |      |      |

|                                                         | Gain = 1                                                                                                                                 |     | 19      |      | mΩ   |

|                                                         | Gain = 10                                                                                                                                |     | 190     |      | mΩ   |

|                                                         | Gain = 100                                                                                                                               |     | 1.9     |      | Ω    |

| Open-Loop Output Impedance (Z <sub>O</sub> )            | f = 1 kHz to 1 MHz, T <sub>A</sub> = 25°C                                                                                                |     | 190     |      | Ω    |

| POWER SUPPLY                                            |                                                                                                                                          |     |         |      |      |

| V <sub>SY</sub> ((V+) - (V-))                           | Guaranteed by PSRR                                                                                                                       | 6   |         | 40   | V    |

| Power Supply Rejection Ratio (PSRR)                     | $V_{SY} = \pm 3 \text{ V to } \pm 20 \text{ V}, T_A = 25^{\circ}\text{C}$                                                                | 121 | 140     |      | dB   |

|                                                         | -40°C < T <sub>A</sub> < +125°C                                                                                                          | 116 |         |      | dB   |

| Supply Current per Amplifier (I <sub>SY</sub> )         | $I_{OUT} = 0 \text{ mA}, T_A = 25^{\circ}\text{C}$                                                                                       |     | 1.45    | 1.55 | mA   |

|                                                         | -40°C < T <sub>A</sub> < +125°C                                                                                                          |     |         | 2    | mA   |

| DYNAMIC PERFORMANCE                                     |                                                                                                                                          |     |         |      |      |

| Slew Rate                                               | V <sub>OUT</sub> = ±5 V, gain = 1, 10% to 90%, T <sub>A</sub> = 25°C                                                                     |     | 19      |      | V/µs |

| Gain Bandwidth Product (GBP)                            | f = 100 kHz, T <sub>A</sub> = 25°C                                                                                                       |     | 10.4    |      | MHz  |

| -3 dB Bandwidth                                         | Gain = 1, T <sub>A</sub> = 25°C                                                                                                          |     | 13.5    |      | MHz  |

| Settling Time (t <sub>S</sub> )                         | T <sub>A</sub> = 25°C                                                                                                                    |     |         |      |      |

|                                                         | To 0.01%                                                                                                                                 |     |         |      |      |

|                                                         | Gain = −1, V <sub>OUT</sub> = 5 V step                                                                                                   |     | 1.9     |      | μs   |

|                                                         | Gain = −1, V <sub>OUT</sub> = 10 V step                                                                                                  |     | 2.2     |      | μs   |

|                                                         | To 0.001%                                                                                                                                |     |         |      |      |

|                                                         | Gain = −1, V <sub>OUT</sub> = 5 V step                                                                                                   |     | 3.1     |      | μs   |

|                                                         | Gain = −1, V <sub>OUT</sub> = 10 V step                                                                                                  |     | 3.5     |      | μs   |

| Output Overload Recovery Time                           | Gain = −10, T <sub>A</sub> = 25°C, positive/negative                                                                                     |     | 300/100 |      | ns   |

| Total Harmonic Distortion (THD)                         | V <sub>OUT</sub> = 10 V p-p, gain = 1, T <sub>A</sub> = 25°C                                                                             |     |         |      |      |

|                                                         | f = 1 kHz                                                                                                                                |     | 0.00002 |      | %    |

|                                                         | f = 1 kHz                                                                                                                                |     | -134    |      | dB   |

|                                                         | f = 50 kHz                                                                                                                               |     | 0.00445 |      | %    |

|                                                         | f = 50 kHz                                                                                                                               |     | -87     |      | dB   |

| ELECTROMAGNETIC INTERFERENCE<br>REJECTION RATIO (EMIRR) | EMIRR = $20 \times \log_{10}(\Delta V_{\rm IN}/\Delta V_{\rm OS})$ , $\Delta V_{\rm IN}$ = $200$ mV p-p, T <sub>A</sub> = $25^{\circ}$ C |     |         |      |      |

|                                                         | f = 1000 MHz                                                                                                                             |     | 71      |      | dB   |

|                                                         | f = 2400 MHz                                                                                                                             |     | 81      |      | dB   |

| CROSSTALK                                               | V <sub>IN</sub> = 4 V p-p, T <sub>A</sub> = 25°C                                                                                         |     |         |      |      |

|                                                         | DC                                                                                                                                       |     | 165     |      | dB   |

|                                                         | f = 1 kHz                                                                                                                                |     | 164     |      | dB   |

|                                                         | f = 100 kHz                                                                                                                              |     | 130     |      | dB   |

analog.com Rev. A | 7 of 29

## **ABSOLUTE MAXIMUM RATINGS**

Table 3. Absolute Maximum Ratings

| Parameter                                  | Rating            |

|--------------------------------------------|-------------------|

| V <sub>SY</sub> ((V+) - (V-))              | -0.3 V to +45 V   |

| Input V <sub>CM</sub>                      |                   |

| (+IN A, $-IN$ A, $+IN$ B, $-IN$ B) to V-   | -0.3 V to +45 V   |

| (+IN A, $-IN$ A, $+IN$ B, $-IN$ B) to V+   | +0.3 V to -45 V   |

| Differential Input Voltage                 |                   |

| +IN A to -IN A, +IN B to -IN B             | ±45 V             |

| Input Current                              | ±10 mA            |

| Output Short-Circuit Duration <sup>1</sup> | Thermally limited |

| Temperature Range                          |                   |

| Storage                                    | -65°C to +150°C   |

| Operating                                  | -40°C to +125°C   |

| $T_J$                                      | 150°C             |

| Lead (soldering, 10 seconds)               | 300°C             |

| T <sub>C</sub>                             | 260°C             |

A heatsink may be required to keep the T<sub>J</sub> below the absolute maximum rating when the output is shorted indefinitely.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Careful attention to PCB thermal design is required.

$\theta_{JA}$  is the natural convection junction-to-ambient thermal resistance measured in a one cubic foot sealed enclosure.

$\theta_{JC}$  is the junction-to-case thermal resistance.

Table 4. Thermal Resistance

| Package Type | $\theta_{JA}$ | $\theta_{\text{JC}}$ | Unit |

|--------------|---------------|----------------------|------|

| R-8          | 108.5         | 34.12                | °C/W |

## **ELECTROSTATIC DISCHARGE (ESD) RATINGS**

The following ESD information is provided for handling of ESD-sensitive devices in an ESD-protected area only.

Human body model (HBM) per ANSI/ESDA/JEDEC JS-001-2017.

Field induced charged-device model (FICDM) per ANSI/ESDA/JE-DEC JS-002-2018.

## **ESD Ratings for ADA4510-2**

Table 5. ADA4510-2, 8-Lead SOIC N

| ESD Model | Withstand Threshold (V) | Class |

|-----------|-------------------------|-------|

| HBM       | ±1000                   | 1C    |

| FICDM     | ±400                    | C1    |

## **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

analog.com Rev. A | 8 of 29

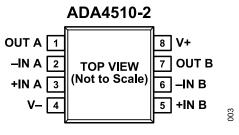

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 3. Pin Configuration

Table 6. Pin Function Descriptions, 8-Lead SOIC

| Pin No. | Mnemonic | Description                    |

|---------|----------|--------------------------------|

| 1       | OUT A    | Output, Channel A.             |

| 2       | -IN A    | Inverting Input, Channel A.    |

| 3       | +IN A    | Noninverting Input, Channel A. |

| 4       | V-       | Negative Supply Voltage.       |

| 5       | +IN B    | Noninverting Input, Channel B. |

| 6       | -IN B    | Inverting Input, Channel B.    |

| 7       | OUT B    | Output, Channel B.             |

| 8       | V+       | Positive Supply Voltage.       |

analog.com Rev. A | 9 of 29

## **TYPICAL PERFORMANCE CHARACTERISTICS**

$V_{SY}$  = ±20 V,  $V_{CM}$  = 0 V,  $R_L$  = 10 k $\Omega$  to midsupply,  $T_A$  = 25°C, unless otherwise noted.

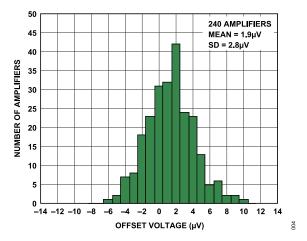

Figure 4. V<sub>OS</sub> Distribution at 25°C

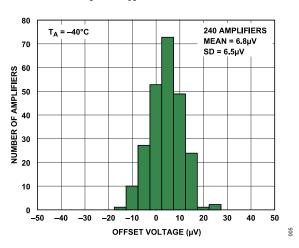

Figure 5. Vos Distribution at -40°C

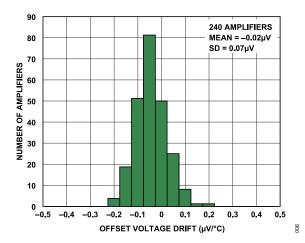

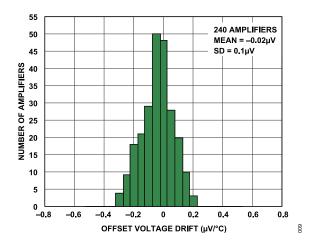

Figure 6. Input Offset Voltage Drift (TCV<sub>OS</sub>) Distribution from 0°C to +85°C

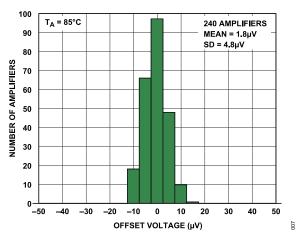

Figure 7. Vos Distribution at 85°C

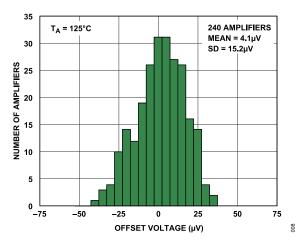

Figure 8. Vos Distribution at 125°C

Figure 9. TCV<sub>OS</sub> Distribution from -40°C to +125°C

analog.com Rev. A | 10 of 29

## **TYPICAL PERFORMANCE CHARACTERISTICS**

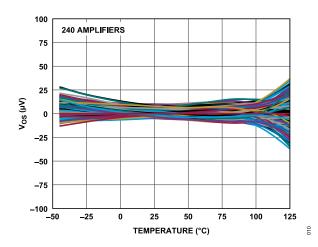

Figure 10. Vos vs. Temperature

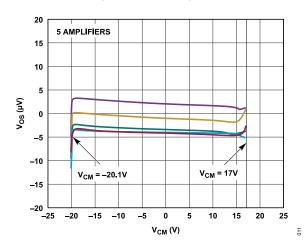

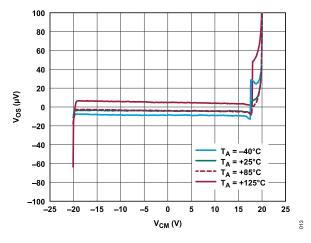

Figure 11. Vos vs. V<sub>CM</sub>

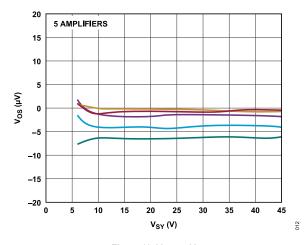

Figure 12. V<sub>OS</sub> vs. V<sub>SY</sub>

Figure 13. V<sub>OS</sub> vs. V<sub>CM</sub>, Four Temperatures

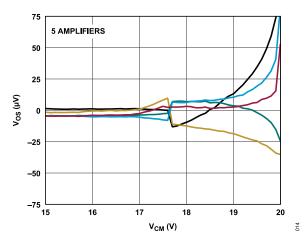

Figure 14. V<sub>OS</sub> vs. V<sub>CM</sub>, High V<sub>CM</sub> Operation

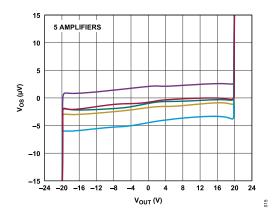

Figure 15. V<sub>OS</sub> vs. V<sub>OUT</sub>

analog.com Rev. A | 11 of 29

## TYPICAL PERFORMANCE CHARACTERISTICS

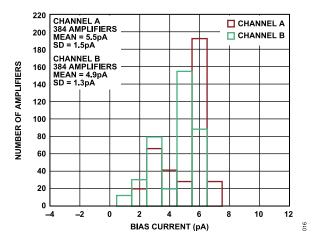

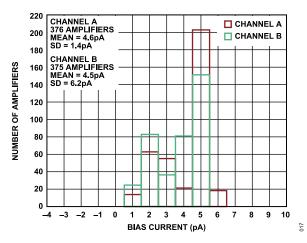

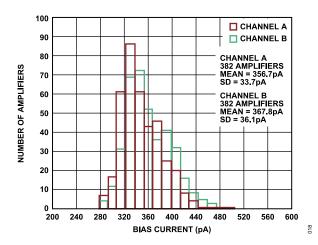

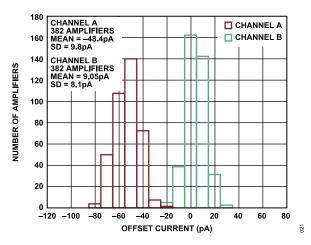

Figure 16. IB Distribution at 25°C

Figure 17. IB Distribution at -40°C

Figure 18. I<sub>B</sub> Distribution at 85°C

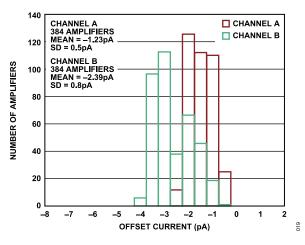

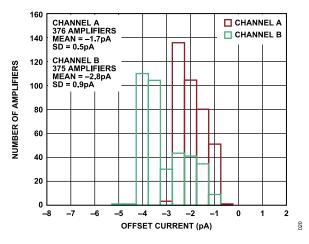

Figure 19. I<sub>OS</sub> Distribution at 25°C

Figure 20. Ios Distribution at -40°C

Figure 21. Ios Distribution at 85°C

analog.com Rev. A | 12 of 29

## **TYPICAL PERFORMANCE CHARACTERISTICS**

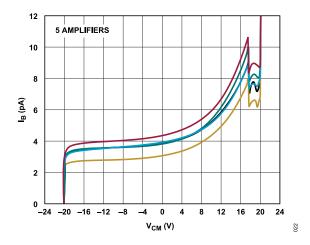

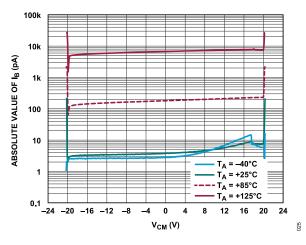

Figure 22. I<sub>B</sub> vs. V<sub>CM</sub>

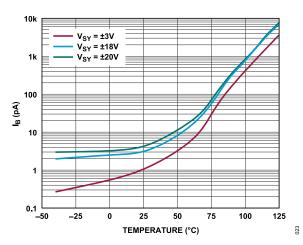

Figure 23. I<sub>B</sub> vs. Temperature

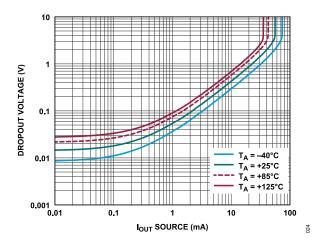

Figure 24. V<sub>DROPOUT</sub> ((V+) - V<sub>OUT</sub>) vs. I<sub>OUT</sub> Source

Figure 25. I<sub>B</sub> vs. V<sub>CM</sub>, Four Temperatures

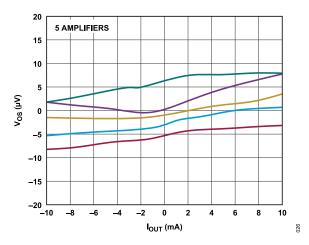

Figure 26. Vos vs. Iout

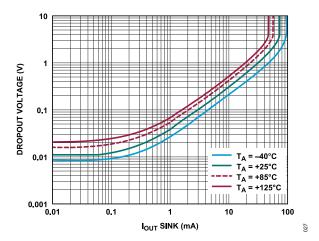

Figure 27. V<sub>DROPOUT</sub> (V<sub>OUT</sub> - (V-)) vs. I<sub>OUT</sub> Sink

analog.com Rev. A | 13 of 29

## TYPICAL PERFORMANCE CHARACTERISTICS

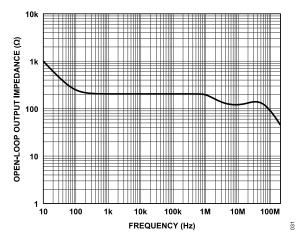

Figure 28. Z<sub>OUT</sub> vs. Frequency

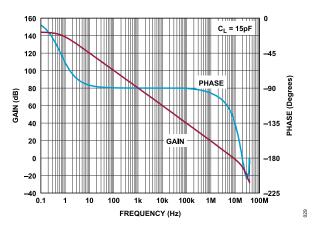

Figure 29. Open-Loop Gain and Phase vs. Frequency

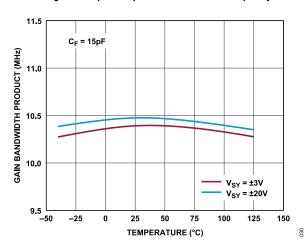

Figure 30. Gain Bandwidth Product vs. Temperature

Figure 31. Z<sub>O</sub> vs. Frequency

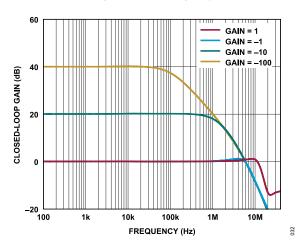

Figure 32. Closed-Loop Gain vs. Frequency

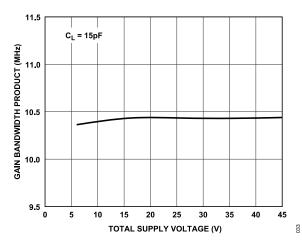

Figure 33. Gain Bandwidth Product vs. Total Supply Voltage

analog.com Rev. A | 14 of 29

## **TYPICAL PERFORMANCE CHARACTERISTICS**

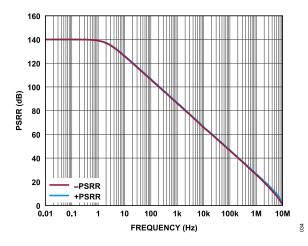

Figure 34. PSRR vs. Frequency

Figure 35. CMRR vs. Frequency

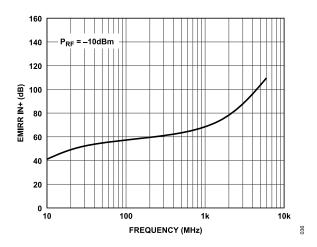

Figure 36. EMIRR IN+ vs. Frequency (P<sub>RF</sub> Is RF Power.)

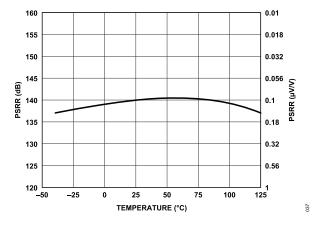

Figure 37. PSRR vs. Temperature

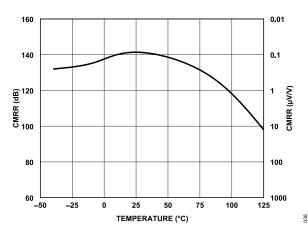

Figure 38. CMRR vs. Temperature

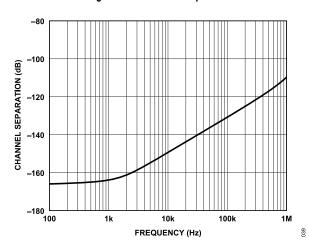

Figure 39. Channel Separation vs. Frequency

analog.com Rev. A | 15 of 29

## TYPICAL PERFORMANCE CHARACTERISTICS

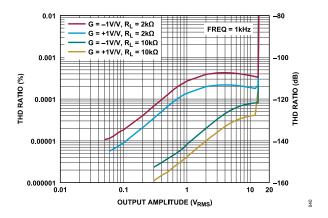

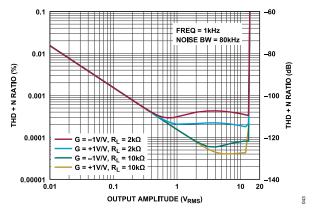

Figure 40. THD Ratio vs. Output Amplitude

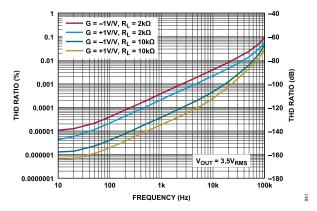

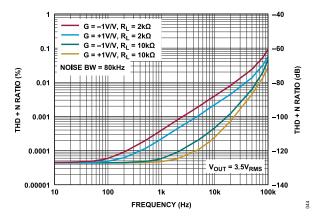

Figure 41. THD Ratio vs. Frequency

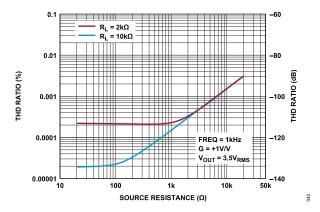

Figure 42. THD Ratio vs. Source Resistance

Figure 43. THD Plus Noise (THD + N) Ratio vs. Output Amplitude

Figure 44. THD + N vs. Frequency

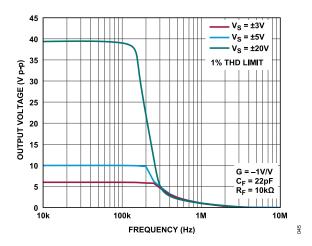

Figure 45. Maximum Undistorted Output Swing vs. Frequency

analog.com Rev. A | 16 of 29

## TYPICAL PERFORMANCE CHARACTERISTICS

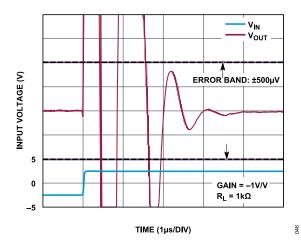

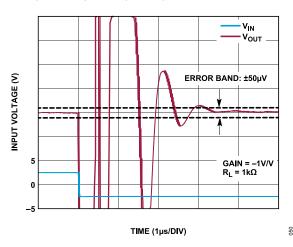

Figure 46. Positive Step Settling Time to 0.01%, V<sub>OUT</sub> = 5 V

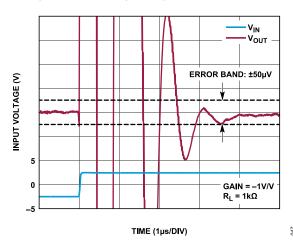

Figure 47. Positive Step Settling Time to 0.001%, V<sub>OUT</sub> = 5 V

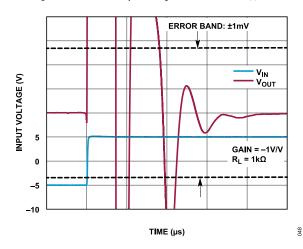

Figure 48. Positive Step Settling Time to 0.01%, V<sub>OUT</sub> = 10 V

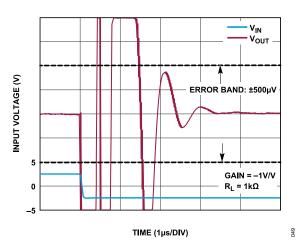

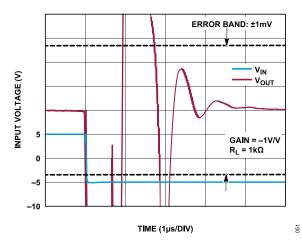

Figure 49. Negative Step Settling Time to 0.01%, V<sub>OUT</sub> = 5 V

Figure 50. Negative Step Settling Time to 0.001%, V<sub>OUT</sub> = 5 V

Figure 51. Negative Step Settling Time to 0.01%, V<sub>OUT</sub> = 10 V

analog.com Rev. A | 17 of 29

## TYPICAL PERFORMANCE CHARACTERISTICS

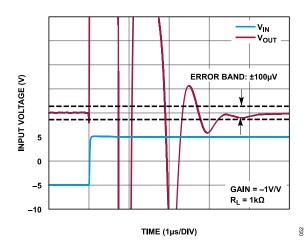

Figure 52. Positive Step Settling Time to 0.001%, V<sub>OUT</sub> = 10 V

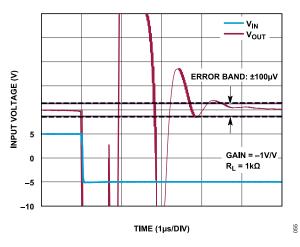

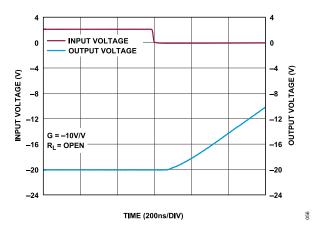

Figure 53. Positive Overload Recovery

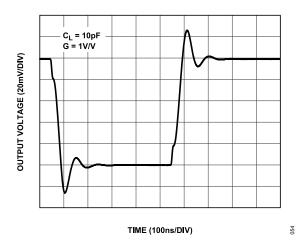

Figure 54. Small Signal Transient Response, G = 1 V/V

Figure 55. Negative Step Settling Time to 0.001%, V<sub>OUT</sub> = 10 V

Figure 56. Negative Overload Recovery

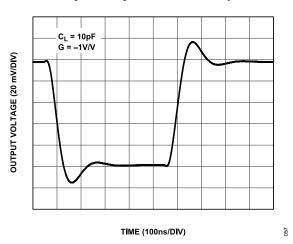

Figure 57. Small Signal Transient Response, G = −1 V/V

analog.com Rev. A | 18 of 29

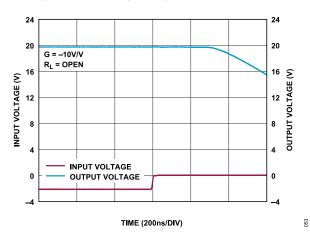

## TYPICAL PERFORMANCE CHARACTERISTICS

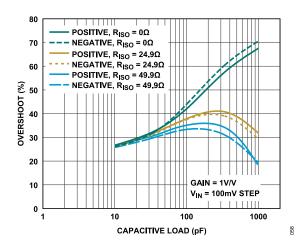

Figure 58. Overshoot vs. Capacitance Load, G = 1 V/V

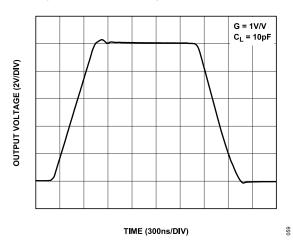

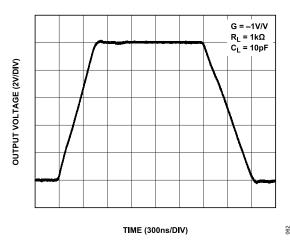

Figure 59. Large Signal Transient Response, G = 1 V/V

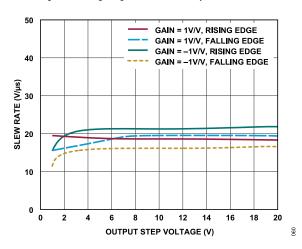

Figure 60. Slew Rate vs. Output Step Voltage

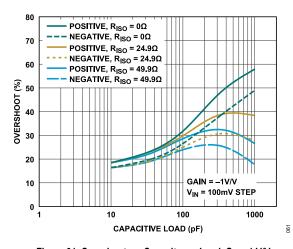

Figure 61. Overshoot vs. Capacitance Load, G = -1 V/V

Figure 62. Large Signal Transient Response, G = -1 V/V

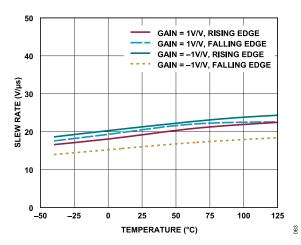

Figure 63. Slew Rate vs. Temperature

analog.com Rev. A | 19 of 29

## TYPICAL PERFORMANCE CHARACTERISTICS

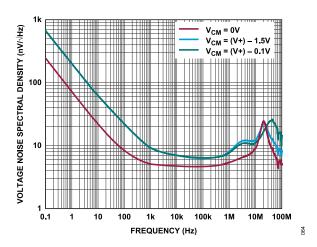

Figure 64. Input Voltage Noise Spectral Density vs. Frequency

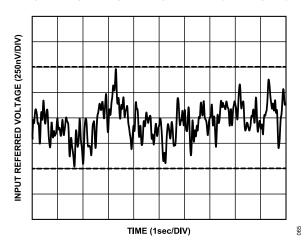

Figure 65. 0.1 Hz to 10 Hz Voltage Noise

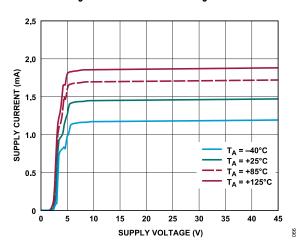

Figure 66. I<sub>S</sub> per Amplifier vs. Supply Voltage at Various Temperatures

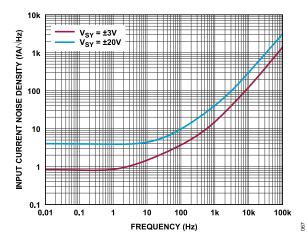

Figure 67. Current Noise Spectral Density vs. Frequency

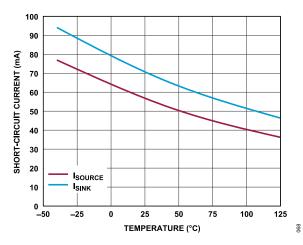

Figure 68. Short-Circuit Output Current vs. Temperature

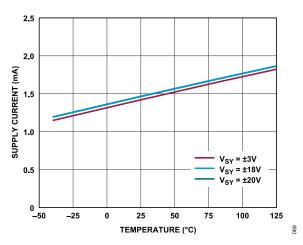

Figure 69. I<sub>S</sub> per Amplifier vs. Temperature for Various Supplies

analog.com Rev. A | 20 of 29

## **TYPICAL PERFORMANCE CHARACTERISTICS**

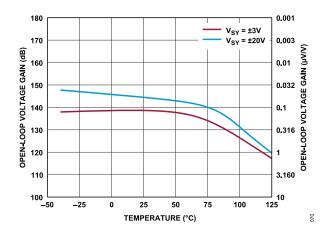

Figure 70. DC Open-Loop Gain vs. Temperature

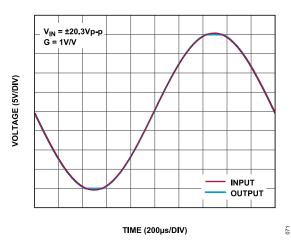

Figure 71. No Phase Reversal

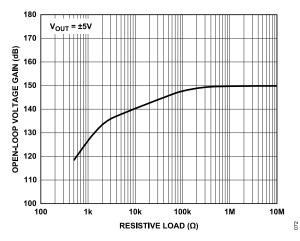

Figure 72. DC Open-Loop Gain vs. R<sub>L</sub>

analog.com Rev. A | 21 of 29

#### THEORY OF OPERATION

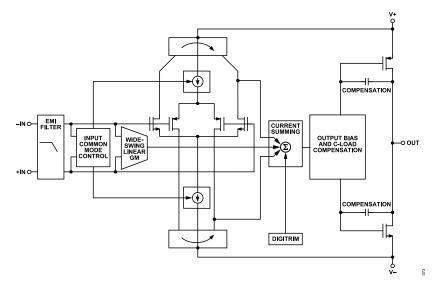

Figure 73. Simplified Schematic

The ADA4510-2 is a dual-channel, low-power, rail-to-rail input and output, precision CMOS op amp that operates over a wide supply voltage range of 6 V to 40 V. This amplifier uses the Analog Devices DigiTrim technique to achieve a higher degree of precision compared to previous CMOS amplifiers. The DigiTrim technique is a method of trimming the offset voltage and the offset voltage temperature drift of an amplifier after assembly. This technique corrects any offset voltages and drifts caused by mechanical stresses during assembly.

## **INPUT AND GAIN STAGES**

Figure 73 shows the simplified circuit diagram for the ADA4510-2. The input architecture provides high-impedance, rail-to-rail differential and common-mode input swing, low noise, low input bias current, and low offset voltage.

An integrated EMI filter increases the signal robustness and helps prevent EMI signals from coupling into the amplifier. Depending on the input common-mode voltage, either the negative channel metal-oxide semiconductor (NMOS) or the positive channel metal-oxide semiconductor (PMOS) input stage can be active at any time. The low offset voltage and low offset voltage drift specifications are possible by using the DigiTrim technique on both the NMOS and PMOS input stages.

The ADA4510-2 includes circuitry that extends the linear input range, providing higher slew rates than a traditional input differential pair and improving the THD. The wide gain bandwidth product of 10.4 MHz is achieved through internal Miller compensation.

#### **OUTPUT STAGE**

The output of the ADA4510-2 swings rail-to-rail to within 100 mV of either supply rail. A capacitive load compensation block senses the load capacitor and adds additional phase margin, if required, to drive a large capacitor (at least 1 nF) and maintain amplifier stability.

#### **EMI REJECTION**

High-frequency EMI is a threat to precision amplifier performance in an intended application. Op amps must accurately amplify input signals despite low signal strength and long transmission lines. All operational amplifier pins are susceptible to EMI signals. These high-frequency signals are coupled into an operational amplifier by various means, such as conduction, near-field radiation, or far-field radiation. For example, wires and printed circuit board (PCB) traces act as antennas to pick up high-frequency EMI signals.

Op amps do not amplify EMI or RF signals due to the relatively low bandwidth of the amplifier. However, due to the nonlinearities of the input devices, op amps can rectify these out-of-band signals, which then appear as a DC offset at the output.

The ADA4510-2 is designed with integrated EMI filters at the input stage of the op amp. The EMIRR describes the ability of the ADA4510-2 to perform as intended in the presence of electromagnetic energy. The EMIRR is specified for the noninverting pin in Table 1. A mathematical method of measuring EMIRR is defined as follows:

$EMIRR = 20 \log \times (\Delta V_{IN} PEAK / \Delta V_{OS})$

EMIRR performance of ADA4510-2 is shown in Figure 36.

## NO PHASE INVERSION

The ADA4510-2 does not suffer from output voltage phase reversal that occurs in some op amps when the specified input  $V_{CM}$  range is exceeded. Output voltage phase reversal causes the output voltage to swing to the opposite rail until the input comes back within the common-mode range. Typically, the inputs of conventional op amps fail to reach or exceed the common-mode limit toward the negative range. Phase-reversal is most often associated with junction field effect transistor (JFET) and/or bipolar field effect transistor (BiFET) amplifiers, but some bipolar single-supply amplifiers are

analog.com Rev. A | 22 of 29

#### THEORY OF OPERATION

also susceptible phase-reversal. The ADA4510-2 guarantees no phase inversion beyond the entire specified input  $V_{CM}$  range all the way to the absolute maximum input voltage limit.

## **CAPACITIVE LOAD DRIVE CAPABILITY**

The ADA4510-2 is stable with any capacitive load up to 1 nF. This is accomplished by dynamically sensing the load-induced output pole and adjusting the compensation at the internal gain node of the amplifier. As the capacitive load increases, the bandwidth will decrease. The phase margin may increase or decrease with different capacitive loads, so there may be overshoot in the transient response for some capacitive loads (see Figure 58 and Figure 61). Coaxial cable less than 1 nF can be driven directly, but, for best pulse fidelity, the cable should be properly terminated by placing a resistor of a value equal to the characteristic impedance of the cable (for example 50  $\Omega$ ) in series with the output. The other end of the cable should be terminated with the same value resistor to ground.

Figure 58 and Figure 61 show the overshoot of the ADA4510-2 with various capacitive loads in unity gain and gain of -1 configurations. To further improve the capacitive load drive of the ADA4510-2, an isolation resistor ( $R_{\rm ISO}$ ) may be used in series with the output to significantly reduce the overshoot and ringing to stabilize the amplifier.

Table 7. Capacitive Load Drive at Various R<sub>ISO</sub>

|                               |     |        | ,00    |     |         |        |  |

|-------------------------------|-----|--------|--------|-----|---------|--------|--|

| Capacitive Load               |     | 100 pF |        |     | 1000 pF | :      |  |

| R <sub>ISO</sub>              | 0 Ω | 24.9 Ω | 49.9 Ω | 0 Ω | 24.9 Ω  | 49.9 Ω |  |

| Positive Overshoot<br>Percent | 42% | 38%    | 35%    | 68% | 32%     | 18%    |  |

| Negative Overshoot<br>Percent | 43% | 38%    | 30%    | 71% | 29%     | 19%    |  |

analog.com Rev. A | 23 of 29

#### **APPLICATIONS INFORMATION**

# MUX-COMPATIBLE DATA ACQUISITION SYSTEM

Data acquisition in multichannel systems can be accomplished by multiplexing as shown in Figure 74. This technique is very popular in instrumentation, industrial process control, and automated test equipment (ATE), because it reduces the number of components needed to sense multiple sensors, saving significant power, size, and cost.

Figure 74. Multiplexed Data Acquisition System

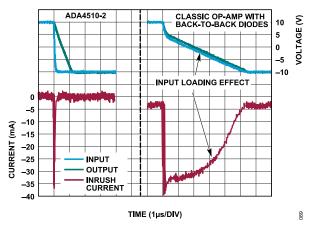

One risk in designing this system is the possibility of exposing the buffer amplifier to a large differential voltage due to the fast switching from a large positive voltage to a large negative voltage by the mux. If the buffer amplifier is not chosen properly, it may experience a large inrush current that can degrade the performance of the system or, worse, permanently damage the part.

The ADA4510-2 solves this problem using a robust mux-compatible architecture that can tolerate large differential voltages up to the supply rails without the use of differential back-to-back diodes. This significantly reduces inrush current, improves settling and distortion performance without experiencing any input loading effect compared to classic op amps with back-to-back diodes, as shown in Figure 75.

Figure 75. ADA4510-2 Inrush Current Reduction

## **Design Example**

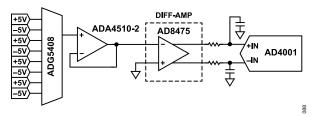

The circuit shown in Figure 76 is a classic multichannel data acquisition signal chain consisting of a mux, amplifiers, and an analog-to-digital converter (ADC). The architecture allows fast sampling of multiple channels using a single ADC, providing low cost and

excellent channel-to-channel matching. Channel-to-channel switching speed is limited by the settling time of the various components following the mux in the signal chain, because the mux can present a full-scale step  $V_{\text{OUT}}$  to the downstream amplifier and the ADC. The components in this circuit have been specifically chosen to minimize settling time and maximize channel-to-channel switching speed.

Figure 76. 16-bit, 8-Channel, Single-ended to Differential, Multiplexed Data Acquisition System

This circuit operates in continuous switching mode. The multiplexer ADG5408 switches continuously with a switching rate that is in sync with the ADC conversion cycle. The signal is buffered by the ADA4510-2 and drives to the AD8475, which attenuates, level shifts, and converts the signal from single-ended to a differential output. An RC filter is used at the input of the ADC to minimize out-of-band noise and attenuate the kickback from the switched capacitor at the ADC input.

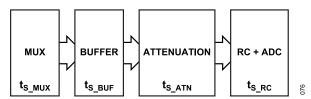

To calculate the settling time, the circuit can be divided into parts shown in Figure 77.

Figure 77. Block Diagram for Settling Time Analysis

The entire settling time is then approximated as the RSS of the settling time of each stage.

analog.com Rev. A | 24 of 29

#### **APPLICATIONS INFORMATION**

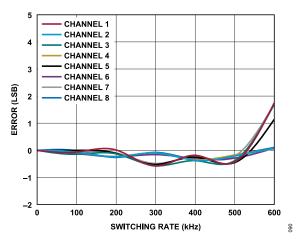

Figure 78. Error (LSB) vs. Switching Rate, 8-Channel 10 V Step

Figure 78 shows the error in LSB vs. switching rate for an 8-channel 10 V step mux data acquisition system. An LSB error <1 is achieved up to 570 kHz switching rate.

## TRANSIMPEDANCE AMPLIFIER

The ADA4510-2 is an excellent choice for low noise transimpedance amplifier (TIA) applications. The low voltage and current noise of the ADA4510-2 maximize signal-to-noise ratio (SNR), and the low  $V_{OS}$  and  $I_{B}$  of the ADA4510-2 minimize the DC error at the amplifier output.

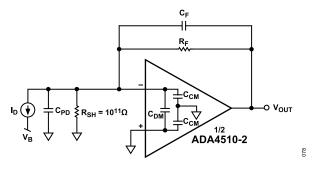

Common applications for current-to-voltage conversion include photodiode circuits where the amplifier converts a current emitted by a diode placed at the negative input terminal into an output voltage. Some photodiode applications include fiber optic controls, motion sensors, and barcode readers. The circuit shown in Figure 79 shows one channel of the ADA4510-2 as a current-to-voltage converter with an electrical model of a photodiode.

Figure 79. Equivalent TIA Circuit

Photodiodes operate in either photovoltaic mode (zero bias) or photoconductive mode (with an applied reverse-bias across the diode). Mode selection depends on the speed and dark current requirements of the application and the choice of photodiode. In photovoltaic mode, the dark current is at a minimum and is preferred for low frequency and/or low light level applications (that is, PN photodiodes). Photoconductive mode is better for applications

that require faster and linear responses (that is, PIN photodiodes); however, the tradeoffs include increases in dark and noise currents.

The following transfer function describes the transimpedance gain of Figure 79:

$$V_{OUT} = \frac{I_D R_F}{1 + sC_F R_F} \tag{1}$$

where:

$V_{OUT}$  is the desired output DC voltage of the op amp.

$I_D$  is the output current of the photodiode.

$R_{\rm F}$  is the feedback resistor.

$C_F$  is the feedback capacitor.

The parallel combination of  $R_{\text{\scriptsize F}}$  and  $C_{\text{\scriptsize F}}$  sets the signal bandwidth.

s is the complex frequency variable j $\omega$ .

i is the imaginary unit.

$\omega$  is the angular frequency.

Set  $R_F$  such that the maximum attainable  $V_{OUT}$  corresponds to the maximum diode  $I_{OUT}$ . Because signal levels increase directly with  $R_F$ , while the noise due to  $R_F$  increases with the square root of the resistor value, employing the full output swing maximizes the SNR.

It is important to distinguish between the transimpedance gain and the loop gain, because the loop gain characteristics determine the net circuit stability. The closed-loop transfer function takes the form shown in the following equation:

$$\frac{V_{OUT}}{V_{IN}} = \frac{A}{1 + A\beta} \tag{2}$$

where:

A is the open loop gain of the amplifier.

$\beta$  is the feedback network.

$A\beta$  is the loop gain.

In this application  $\beta$  is given by the following:

$$\beta = \left(\frac{R_{SH}}{R_{SH} + R_F}\right) \frac{1 + sR_FC_F}{1 + s(R_F \parallel R_{SH})(C_{IN} + C_F)} \tag{3}$$

where:

$R_{SH}$  is the diode shunt resistance.

$C_{IN}^{O}$  is the total input capacitance consisting of the sum of the diode shunt capacitance ( $C_{PD}$ ), the input capacitance of the amplifier ( $C_{DM}$  +  $C_{CM}$ ), and the external stray capacitance.

$C_{\it IN},\,R_{\it F},\,C_{\it F},\,$  and  $R_{\it SH}$  produce a zero in the 1/ $\beta$  transfer function. The zero frequency  $(f_{\it Z})$  is as in the equation that follows:

$$f_Z = \frac{1}{2\pi (R_F \parallel R_{SH})(C_{IN} + C_F)}$$

(4)

Because the photodiode shunt resistance  $R_{SH} >> R_F$ , the circuit behavior is not impacted by the effect of the junction resistance, and  $f_7$  simplifies to the following:

$$f_Z = \frac{1}{2\pi R_F (C_{IN} + C_F)} \tag{5}$$

analog.com Rev. A | 25 of 29

#### **APPLICATIONS INFORMATION**

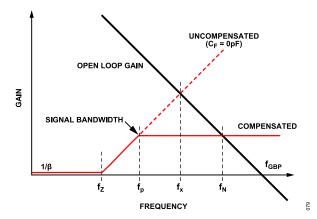

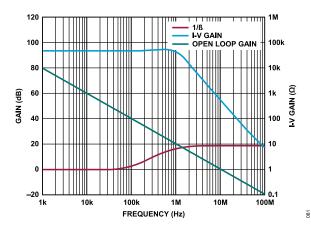

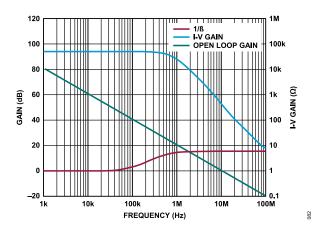

Figure 80 shows the TIA  $1/\beta$  curve superimposed upon the open loop gain of the amplifier. For the system to be stable, the  $1/\beta$  curve must have a slope of less than 20 dB/decade when it intersects with the open loop response. In Figure 80 the dotted line shows an uncompensated  $1/\beta$  response ( $C_F = 0$  pF) intersecting with the open loop gain at the frequency ( $f_X$ ) with a slope of 20 dB/decade which indicates an unstable condition.

Figure 80. Generalized TIA 1/β and Transfer Function

The instability caused by  $C_{IN}$  can be compensated by adding  $C_F$  to introduce a pole at a frequency equal to or lower than  $f_X$ . The pole frequency is as follows:

$$f_P = \frac{1}{2\pi R_F C_F} \tag{6}$$

Setting the pole at the  $f_X$  frequency maximizes the signal bandwidth with a 45° phase margin but is marginal for stability, as indicated by the dashed line. Because  $f_X$  is the geometric mean of  $f_Z$  and the gain bandwidth product frequency ( $f_{GBP}$ ) of the amplifier, calculate  $f_X$  by the following equation:

$$f_X = \sqrt{f_Z f_{GBP}} \tag{7}$$

Substituting Equation 5 and Equation 6 into Equation 7, the C<sub>F</sub> value that produces f<sub>X</sub> follows:

$$C_F = \frac{1 + \sqrt{1 + 8\pi R_F C_{IN} f_{GBP}}}{4\pi R_F f_{GBP}} \tag{8}$$

If  $8\pi \times R_F \times C_{IN} \times f_{GBP} >> 1$ , Equation 8 simplifies to the following:

$$C_F = \sqrt{\frac{c_{IN}}{2\pi R_F f_{GBP}}} \tag{9}$$

Adding  $C_F$  also sets the signal bandwidth at  $f_P$ . Substitute Equation 9 into Equation 6 and rearrange the equation for the signal bandwidth in terms of  $f_{GBP}$ ,  $R_F$ , and  $C_{IN}$  as follows:

$$f_P = \sqrt{\frac{f_{GBP}}{2\pi R_F C_{IN}}} \tag{10}$$

Notice the attainable signal bandwidth is a function of the time constant  $R_FC_{IN}$  and the  $f_{GBP}$  of the amplifier. To maximize the signal bandwidth, choose an op amp with high bandwidth and low input

capacitance, and operate the photodiode in reverse bias to reduce its junction capacitance.

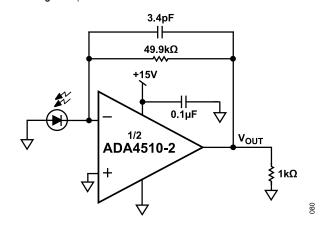

## **Design Example**

As a design example, Figure 81 shows one channel of the ADA4510-2 configured as a TIA amplifier in a photodiode preamp application. Assuming the photodiode has a  $C_D$  of 5 pF, an  $I_D$  of 2  $\mu A$ , and the desired full-scale  $V_{OUT}$  is 100 mV,  $R_F$  is 49.9  $k\Omega$  according to Equation 1.

Figure 81. Single-Supply TIA Circuit Using the ADA4510-2

The ADA4510-2 input capacitance ( $C_{CM} + C_{DM}$ ) is 22 pF, so the total input capacitance ( $C_{IN}$ ) is 27 pF. By substituting  $C_{IN}$  = 27 pF,  $R_F$  = 49.9 k $\Omega$ , and  $f_{GBP}$  = 10 MHz into Equation 8 and Equation 10, the resulting  $C_F$  value and the -3 dB signal bandwidth ( $f_P$ ) are 3.1 pF and 1.1 MHz, respectively.

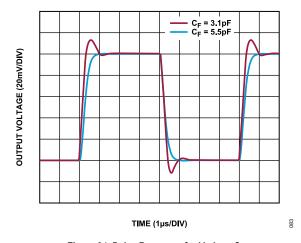

Figure 82 and Figure 83 show the compensations of the TIA circuit. The system has a bandwidth of 1.1 MHz when it is maximized for a signal bandwidth with  $C_F = 3.1$  pF. Increasing  $C_F$  to 5.5 pF reduces the bandwidth to 579 kHz. However, increasing the  $C_F$  greatly reduces the overshoot (see Figure 84). In practice, an optimum  $C_F$  value is determined experimentally by varying it slightly to optimize the output pulse response.

Use the Analog Devices Analog Photodiode Wizard to design a transimpedance amplifier circuit to interface with a photodiode.

analog.com Rev. A | 26 of 29

#### **APPLICATIONS INFORMATION**

Figure 82. Compensating the TIA,  $C_F = 3.1 pF$

Figure 83. Compensating the TIA,  $C_F = 5.5 pF$

Figure 84. Pulse Response for Various C<sub>F</sub>

#### **ACTIVE FILTER**

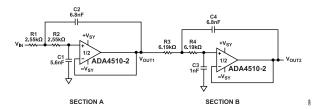

Figure 85. 4-Pole Low Pass Filter with -3dB Bandwidth of 10kHz

Active filters are used to separate signals, passing signals of interest and attenuating signals at unwanted frequencies. For example, low-pass filters are often used as antialiasing filters in data acquisition systems or as noise filters to limit high frequency noise.

The high input impedance, high bandwidth, low input bias current, and DC precision make the ADA4510-2 a good fit for active filter applications. Figure 85 shows the ADA4510-2 in a 4-pole Sallen-Key Butterworth low-pass filter configuration. The 4-pole low-pass filter has two complex conjugate pole pairs and is implemented by cascading two 2-pole low-pass filters. Section A and Section B are configured as 2-pole low-pass filters in unity gain. Table 8 shows the quality factor (Q) requirement and pole position associated with each stage of the Butterworth filter. Refer to Chapter 8, Analog Filters, in Linear Circuit Design Handbook, available at www.analog.com/AnalogDialogue, for pole locations on the s plane and Q requirements for filters of a different order.

Table 8. Q Requirements and Pole Positions

| Section | Poles             | Q      |

|---------|-------------------|--------|

| A       | −0.9239 ± j0.3827 | 0.5412 |

| В       | -0.3827 ± j0.9239 | 1.3065 |

The Sallen-Key topology is widely used due to its simple design with few circuit elements. This topology provides the user the flexibility of implementing either a low-pass or a high-pass filter by simply interchanging the resistors and capacitors. The ADA4510-2 is configured in unity gain with a corner frequency at 10 kHz. An active filter requires an op amp with a unity-gain bandwidth that is at least 100 times greater than the product of the corner frequency ( $f_C$ ) and the Q. The resistors and capacitors are also important in determining the performance over manufacturing tolerances, time, and temperature. At least 1% or better tolerance resistors and 5% or better tolerance capacitors are recommended.

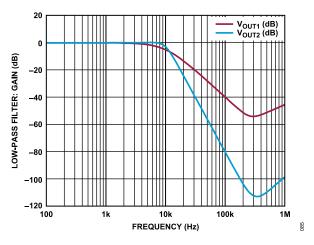

Figure 86 shows the frequency response of the low-pass Sallen-Key filter, where:

$V_{OUT1}$  is the output of the first stage.

V<sub>OUT2</sub> is the output of the second stage.

V<sub>OUT1</sub> shows a 40 dB/decade roll-off and V<sub>OUT2</sub> shows an 80 dB/decade roll-off. The transition band becomes sharper as the order of the filter increases.

analog.com Rev. A | 27 of 29

#### **APPLICATIONS INFORMATION**

Figure 86. Low-Pass Filter: Gain vs. Frequency

## **FEEDBACK COMPONENTS**

When feedback resistors are used to set up gain, care must be taken to ensure that the pole formed by the resistors and the parasitic capacitance at the inverting input does not degrade stability. If the pole formed is near the desired crossover frequency of the amplifier, the stability will be negatively impacted.

In general, if the parasitic pole lies within the closed-loop bandwidth of the amplifier, add a capacitor in parallel with the  $R_{\text{F}}$  to introduce a zero that has a frequency close to the frequency of the pole to improve stability.

For a more detailed discussion, see the Analog Dialogue article: Truth About Voltage Feedback Resistors.

#### PRECISION BUFFER

The overall precision of high-resolution systems with ADCs and digital-to-analog converters (DACs) depends on the accuracy, stability, and drive capability of the voltage reference of the system. Typically, the best performance requires a costly external reference, because on-chip references and buffers often have poor performance or insufficient drive.

With its low noise specs, the ADA4510-2 can be used to preserve the accuracy of the chosen reference for successive approximation register (SAR) ADC reference inputs. The Voltage Reference Design for Precision Successive-Approximation ADCs Analog Dialogue Article details several considerations and how to compute for noise from the reference circuit to ensure that ADC performance is not affected.

DAC outputs that drive real world sensors also depend on the accuracy of the reference voltage. The low  $V_{OS},\,\Delta V_{OS}\,/\,\Delta T,\,I_B,\,e_n$  p-p, and very high linearity, in combination with the fast settling time and slew rate, make the ADA4510-2 an ideal fit for an output DAC buffer.

#### RECOMMENDED POWER SOLUTION

Analog Devices, Inc. has a wide range of power management products that meet the requirements of most high performance signal chains. For a dual-supply application, the ADA4510-2 may need as high as ±20 V supply. Low dropout (LDO) linear regulators such as the LT3042 for the positive supply and the LT3093 for the negative supply help improve the PSRR at high frequency and generate a low noise power rail. In addition, if a negative supply is not available, the ADP5070 can generate the negative supply from a positive supply. Table 9 shows the list of the recommended Power Management Devices for ADA4510-2.