003

# 10 MHz to 20 GHz Integrated Vector Network Analyzer Front End

## **FEATURES**

- ▶ Wideband integrated bidirectional bridge

- ▶ Raw directivity: 24.1 dB at 1 GHz, 12.8 dB at 18 GHz

- ▶ Low insertion loss: 1.1 dB at 1 GHz, 1.9 dB at 18 GHz

- ▶ Return loss: >12 dB typical

- ▶ SPI configurable LO interface

- ▶ Divide by 2; multiply by 1, 2, or 4

- Offset LO interface enables drive with f<sub>RF</sub> = f<sub>LO</sub>

- Single-ended or differential drive

- ▶ SYNC function—synchronization across multiple devices

- ▶ High dynamic range wideband IF signal path

- ▶ SPI-programmable IF bandwidth from 1 MHz to 100 MHz

- ▶ SPI-programmable IF gain, 6 dB step size

- ► Externally adjustable output common-mode level

- ▶ 5-bit SPI readable temperature sensor

- ▶ Low power shutdown mode

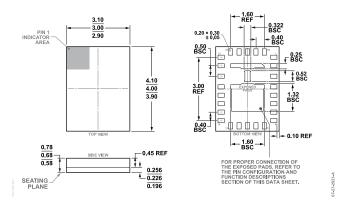

- ▶ 3 mm × 4 mm, 26-lead LGA

## **APPLICATIONS**

- ▶ Broadband, multiport vector network analyzers

- ▶ S-parameter magnitude and phase measurement

- ▶ Inline RF power measurement

- Automated test equipment

- Reflectometers

- Materials analysis

# **GENERAL DESCRIPTION**

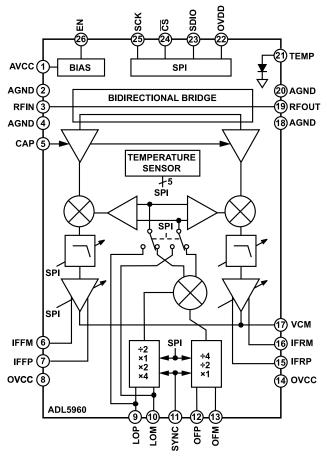

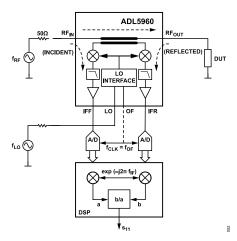

The ADL5960 is a wideband, small form factor vector network analyzer front end consisting of a resistive bidirectional bridge, downconversion mixers, programmable IF amplifiers and filters, and a highly flexible local oscillator (LO) interface. The bridge provides >14 dB of directivity up to 17 GHz. The primary transmission line from RFIN to RFOUT is wideband matched to 50  $\Omega$  with only 1.1 dB loss at low frequencies, increasing to 1.8 dB loss at 20 GHz.

The ADL5960 supports several different LO interface configurations that simplify the clocking design of a vector network analyzer (VNA) solution as well as the interfacing of the device to an analog-to-digital converter (ADC). The frequency divider and multipliers in the LO interface enable measurement sweeps beyond the operating frequency range of the LO source, enabling operation over the full 20 GHz frequency range of the ADL5960 using a 6 GHz synthesizer. The IF frequency offset mixer, driven through the offset interface formed by the OFP and OFM pins, enables further simplification by allowing the swept RF and LO interfaces to share the same

## **FUNCTIONAL BLOCK DIAGRAM**

Figure 1. Functional Block Diagram

frequency source. The frequency of the IF output signals is then determined by the low-frequency source driving the OFP/OFM interface. When this interface is driven at the ADC sample frequency with the divide by 4 enabled, it automatically centers the IF output signal in the first Nyquist zone.

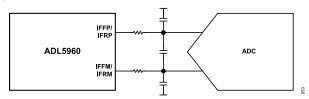

The IF filters with programmable bandwidth and IF amplifiers with individually programmable gain enable simultaneous dynamic range optimization of the IF output signals of the forward channel (IFFP, IFFM) and reverse channel (IFRP, IFRM). The IF amplifiers have an adjustable output common-mode level, sufficient drive capability, and wide output voltage swing to enable direct interfacing to a wide range of ADCs.

All configurations and functions in the ADL5960 are fully programmable through a 3-wire serial peripheral interface (SPI). The ADL5960 is offered in a 3 mm × 4 mm, 26-lead land grid array (LGA) package.

Rev. A

DOCUMENT FEEDBACK

TECHNICAL SUPPORT

Information furnished by Analog Devices is believed to be accurate and reliable "as is". However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

# **TABLE OF CONTENTS**

| Features1                                         | Multiport Vector Network Analyzer | 17 |

|---------------------------------------------------|-----------------------------------|----|

| Applications1                                     | Calibration and Error Correction  | 19 |

| Functional Block Diagram1                         | Applications Information          | 23 |

| General Description1                              | Interface Descriptions            |    |

| Specifications3                                   | LO Interface Configuration        | 25 |

| Serial Interface Timing Specifications5           | IF Signal Path Configuration      | 26 |

| Absolute Maximum Ratings6                         | Serial Peripheral Interface       | 28 |

| Thermal Resistance6                               | Protocol                          | 28 |

| ESD Caution6                                      | Register Address                  | 28 |

| Pin Configuration and Function Descriptions 7     | Read and Write Methods            | 28 |

| Typical Performance Characteristics8              | Register Details                  | 28 |

| Theory of Operation16                             | Typical Application Test Circuit  |    |

| Basic One-Port Vector Network Analyzer16          | Outline Dimensions                | 32 |

| Frequency Planning—LO Configurations16            | Ordering Guide                    | 32 |

| OF Interface17                                    | Evaluation Boards                 |    |

| IF Signal Path17                                  |                                   |    |

| REVISION HISTORY                                  |                                   |    |

| 7/2023—Rev. 0 to Rev. A Changes to Ordering Guide |                                   | 32 |

| -                                                 |                                   |    |

7/2023—Revision 0: Initial Version

analog.com Rev. A | 2 of 32

# **SPECIFICATIONS**

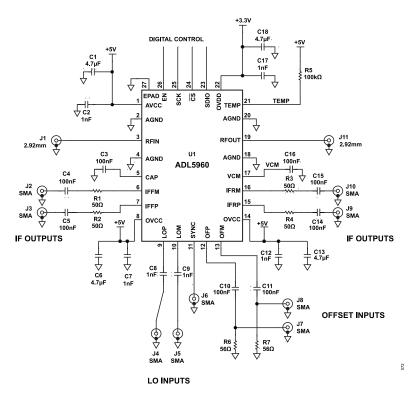

AVCC = OVCC = 5.0 V, EN = OVDD = 3.3 V, VCM = 2.5 V,  $T_A$  = 25°C, source and load impedance = 50  $\Omega$ , continuous wave (CW) input at RFIN, RF power ( $P_{RF}$ ) = 0 dBm, LO drive single-ended, LO power ( $P_{LO}$ ) = 0 dBm, RF frequency ( $f_{RF}$ ) = 1 GHz, LO frequency ( $f_{LO}$ ) =  $f_{RF}$  + 500 kHz, FGAIN (Register 0x23, Bits[6:0]) = RGAIN (Register 0x24, Bits[6:0]) = 24 (decimal), BYPASS (Register 0x20, Bit 4) = 1, default SPI register values, unless otherwise noted. Test circuit shown in Figure 72.

Table 1. Specifications

| Parameter                                        | Test Conditions/Comments                         | Min | Тур        | Max | Unit |

|--------------------------------------------------|--------------------------------------------------|-----|------------|-----|------|

| BIDIRECTIONAL BRIDGE                             | RFIN to RFOUT                                    |     |            |     |      |

| RF Frequency Range                               |                                                  |     | 0.01 to 20 |     | GHz  |

| Insertion Loss                                   | f <sub>RF</sub> = 10 MHz                         |     | 1.0        |     | dB   |

|                                                  | f <sub>RF</sub> = 1 GHz                          |     | 1.1        |     | dB   |

|                                                  | f <sub>RF</sub> = 10 GHz                         |     | 1.8        |     | dB   |

|                                                  | f <sub>RF</sub> = 15 GHz                         |     | 1.8        |     | dB   |

|                                                  | f <sub>RF</sub> = 18 GHz                         |     | 1.9        |     | dB   |

|                                                  | f <sub>RF</sub> = 20 GHz                         |     | 1.8        |     | dB   |

| Return Loss                                      | f <sub>RF</sub> < 20 GHz                         |     | >12        |     | dB   |

| Directivity <sup>1</sup>                         | f <sub>RF</sub> = 10 MHz, LOMODE = 0, BYPASS = 0 |     | 21.6       |     | dB   |

| •                                                | f <sub>RF</sub> = 1 GHz                          |     | 24.1       |     | dB   |

|                                                  | f <sub>RF</sub> = 10 GHz                         |     | 28.3       |     | dB   |

|                                                  | f <sub>RF</sub> = 15 GHz                         |     | 20.7       |     | dB   |

|                                                  | f <sub>RF</sub> = 18 GHz                         |     | 12.8       |     | dB   |

|                                                  | f <sub>RF</sub> = 20 GHz                         |     | 8.9        |     | dB   |

| Third-Order Intercept (IP3)                      | f <sub>RF</sub> = 1 GHz                          |     | 71         |     | dBm  |

| VNA CHANNELS                                     | RFIN to IFFP/IFFM, RFOUT to IFRP/IFRM            |     |            |     |      |

| RF Frequency Range                               |                                                  |     | 0.01 to 20 |     | GHz  |

| RF to IF Leakage                                 | f <sub>RF</sub> = 50 MHz, differential IF output |     | -13.5      |     | dBV  |

| Maximum Voltage Conversion Gain <sup>2</sup>     | FGAIN, RGAIN = 0x42 (66 dB)                      |     |            |     |      |

|                                                  | f <sub>RF</sub> = 10 MHz                         |     | 41.1       |     | dB   |

|                                                  | f <sub>RF</sub> = 1 GHz                          |     | 49.2       |     | dB   |

|                                                  | f <sub>RF</sub> = 10 GHz                         |     | 48.0       |     | dB   |

|                                                  | f <sub>RF</sub> = 15 GHz                         |     | 47.4       |     | dB   |

|                                                  | f <sub>RF</sub> = 18 GHz                         |     | 46.4       |     | dB   |

|                                                  | f <sub>RF</sub> = 20 GHz                         |     | 45.2       |     | dB   |

| Minimum Voltage Conversion Gain                  | FGAIN, RGAIN = 0x00 (0 dB)                       |     |            |     |      |

|                                                  | f <sub>RF</sub> = 10 MHz                         |     | -21.4      |     | dB   |

|                                                  | f <sub>RF</sub> = 1 GHz                          | -15 | -13.3      | -11 | dB   |

|                                                  | f <sub>RF</sub> = 10 GHz                         |     | -14.5      |     | dB   |

|                                                  | f <sub>RF</sub> = 15 GHz                         |     | -15.2      |     | dB   |

|                                                  | f <sub>RF</sub> = 18 GHz                         |     | -16.2      |     | dB   |

|                                                  | f <sub>RF</sub> = 20 GHz                         |     | -17.3      |     | dB   |

| Conversion Gain Step Size                        | See Table 11                                     | 4.4 | 6.0        | 6.3 | dB   |

| Input 1dB Compression Point (IP1dB)              | f <sub>RF</sub> = 1 GHz, FGAIN = RGAIN = 0       |     | 29         |     | dBm  |

| Output 1dB Compression Point (OP1dB)             | FGAIN, RGAIN ≥ 12, 100 Ω differential load       |     | 18.4       |     | dBm  |

| Input Third-Order Intercept (IIP3) <sup>3</sup>  | f <sub>RF</sub> = 1 GHz, FGAIN, RGAIN = 0        |     | 32         |     | dBm  |

| Output Third-Order Intercept (OIP3)              | FGAIN = RGAIN = 30 (decimal)                     |     | 32.3       |     | dBm  |

| Input Second-Order Intercept (IIP2) <sup>3</sup> | f <sub>RF</sub> = 1 GHz, FGAIN = RGAIN = 0       |     | 55         |     | dBm  |

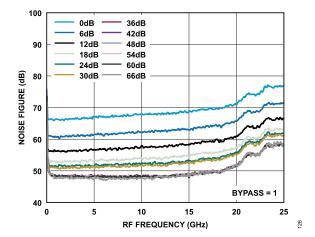

| Noise Figure                                     | FGAIN = RGAIN = 60 (decimal)                     |     |            |     |      |

| -                                                | f <sub>RF</sub> = 10 MHz                         |     | 73.5       |     | dB   |

|                                                  | f <sub>RF</sub> = 1 GHz                          |     | 48.2       |     | dB   |

|                                                  | f <sub>RF</sub> = 10 GHz                         |     | 48.1       |     | dB   |

analog.com Rev. A | 3 of 32

# **SPECIFICATIONS**

Table 1. Specifications (Continued)

| Parameter                                                | Test Conditions/Comments                                                  | Min        | Тур         | Max        | Unit    |

|----------------------------------------------------------|---------------------------------------------------------------------------|------------|-------------|------------|---------|

|                                                          | f <sub>RF</sub> = 15 GHz                                                  |            | 47.7        |            | dB      |

|                                                          | $f_{RF} = 18 \text{ GHz}$                                                 |            | 49.5        |            | dB      |

|                                                          | f <sub>RF</sub> = 20 GHz                                                  |            | 51.7        |            | dB      |

| LO INTERFACE                                             | LOP, LOM                                                                  |            |             |            |         |

| Input Frequency Range                                    | BYPASS = 1                                                                |            | 0.01 to 20  |            | GHz     |

|                                                          | BYPASS = 0, LOMODE = 0 (divide by 2)                                      |            | 0.02 to 2.4 |            | GHz     |

|                                                          | BYPASS = 0, LOMODE = 1 (1×)                                               |            | 0.01 to 20  |            | GHz     |

|                                                          | BYPASS = 0, LOMODE = 2 (2×)                                               |            | 2 to 8      |            | GHz     |

|                                                          | BYPASS= 0, LOMODE = 3 (4×)                                                |            | 4 to 8      |            | GHz     |

| Return Loss                                              | Characteristic impedance ( $Z_O$ ) = 100 $\Omega$ differential            |            | >10         |            | dB      |

| Input Power                                              |                                                                           | -6         | 0           | +6         | dBm     |

| LO to RF Leakage                                         | BYPASS = 1, f <sub>LO</sub>                                               |            | -77.3       |            | dBm     |

|                                                          | BYPASS = 0, LOMODE = 0 (divide by 2), $f_{LO}/2$                          |            | -83.4       |            | dBm     |

|                                                          | BYPASS = 0, LOMODE = 0 (divide by 2), fLO                                 |            | -72.1       |            | dBm     |

|                                                          | BYPASS = 0, LOMODE = 1 (1×), f <sub>LO</sub>                              |            | -80.4       |            | dBm     |

|                                                          | BYPASS = 0, LOMODE = 2 (2×), f <sub>LO</sub>                              |            | -86.4       |            | dBm     |

|                                                          | BYPASS = 0, LOMODE = 2 (2×), 2f <sub>LO</sub>                             |            | -81.7       |            | dBm     |

|                                                          | BYPASS = 0, LOMODE = $3 (4x)$ , $f_{LO}$                                  |            | -93.4       |            | dBm     |

|                                                          | BYPASS = 0, LOMODE = $3 (4\times), 2f_{LO}$                               |            | -102        |            | dBm     |

|                                                          | BYPASS = 0, LOMODE = 3 $(4\times)$ , $4f_{LO}$                            |            | -92.1       |            | dBm     |

| LO to IF Leakage                                         | f <sub>RF</sub> = 50 MHz, differential                                    |            | 13.6        |            | dBV     |

| OFFSET FREQUENCY (OF) INTERFACE                          | OFP, OFM                                                                  |            |             |            |         |

| Input Frequency Range                                    | ,                                                                         |            | 0.1 to 400  |            | MHz     |

| OF Induced Spurious Tone at f <sub>IF</sub> <sup>4</sup> | OFMODE = 2 (divide by 4), $3f_{IF}$ = 1.5 MHz                             |            | -3.2        |            | dBc     |

| "                                                        | 5f <sub>IF</sub> = 2.5 MHz                                                |            | -6.2        |            | dBc     |

|                                                          | 7f <sub>IF</sub> = 3.5 MHz                                                |            | -8.7        |            | dBc     |

| Input Impedance                                          | Differential                                                              |            | 10  0.5     |            | kΩ  pF  |

| Voltage Swing                                            | Differential                                                              | 0.125      | 0.5         | 2.0        | V p-p   |

| IF OUTPUT INTERFACE                                      | IFFP/IFFM and IFRP/IFRM                                                   |            |             |            |         |

| Output Frequency Range                                   |                                                                           |            | 0.1 to 100  |            | MHz     |

| Maximum Peak-to-Peak Voltage                             | Differential                                                              |            | 8           |            | V p-p   |

| Short-Circuit Output Current                             | Single-ended, sourcing, output voltage = 0 V                              | 200        |             |            | mA      |

| Output Noise Spectral Density                            | f = f <sub>IF</sub> = 500 kHz, FGAIN = RGAIN = 60 (decimal), differential |            | 207         |            | μV/√Hz  |

| VCM INTERFACE                                            | VCM                                                                       |            |             |            | μν/     |

| Input Voltage Range                                      |                                                                           | 1.0        |             | 4.0        | V       |

| Output V <sub>CM</sub> Error                             | IF output common-mode voltage (V <sub>CM</sub> )                          | -100       | 0           | +100       | mV      |

| Input Impedance                                          | in output common mode voltage (v <sub>CM</sub> )                          | 100        | 10k    4p   | . 100      | Ω    F  |

| ENABLE INTERFACE                                         | EN                                                                        |            | TOK    IP   |            | 32    1 |

| Logic Low Input Voltage                                  | LIV                                                                       |            |             | 0.8        | V       |

| Logic High Input Voltage                                 |                                                                           | 2.0        |             | 0.0        | V       |

| Current into pin                                         |                                                                           | 2.0        |             | 20         | μA      |

| SPI AND SYNC INTERFACE                                   | CS, SCK, SDIO, SYNC                                                       |            |             |            | μ/ τ    |

| Logic Low Input Voltage                                  | OO, OOK, ODIO, OTNO                                                       |            |             | 0.3 × OVDD | V       |

|                                                          |                                                                           | 0.7 × OVDD |             | 0.5 ^ 0700 | V       |

| Logic High Input Voltage                                 |                                                                           | 0.7 ^ 0000 | 200         |            |         |

| Input Voltage Hysteresis Current into Pin                | $\overline{CS}$ , SCK, SYNC                                               |            | 209         | 20         | mV      |

|                                                          |                                                                           |            |             |            | μA      |

| Logic Low Output Voltage                                 | SDIO, sinking 10 mA                                                       | 0.7 0\/DD  |             | 0.3 × OVDD | V       |

| Logic High Output Voltage                                | SDIO, sourcing 10 mA                                                      | 0.7 × OVDD |             |            | V       |

analog.com Rev. A | 4 of 32

## **SPECIFICATIONS**

Table 1. Specifications (Continued)

| Parameter                    | Test Conditions/Comments                                 | Min  | Тур | Max  | Unit |

|------------------------------|----------------------------------------------------------|------|-----|------|------|

| POWER SUPPLY INTERFACES      | AVCC, OVCC, OVDD                                         |      |     |      |      |

| Supply Voltage (AVCC, OVCC)  |                                                          | 4.75 | 5.0 | 5.25 | V    |

| Supply Current (AVCC + OVCC) | EN = AVCC, Register 0x20 = 0x0B (BYPASS = 0, LOMODE = 3) | 200  | 225 | 250  | mA   |

|                              | EN = AVCC, Register 0x20 = 0x1D (OFMODE = 3)             | 110  | 120 | 130  | mA   |

|                              | EN = 0 V (shutdown)                                      |      | 32  | 2000 | μA   |

| SPI Supply Voltage (OVDD)    |                                                          | 1.8  | 3.3 | 3.6  | V    |

| SPI Supply Current (OVDD)    |                                                          | 2    | 24  | 500  | μA   |

<sup>1</sup> Error correction coefficient (e<sub>00</sub>) obtained from measurements of the ratio of reverse and forward IF output ports for short, open, and load terminations on RFOUT. Printed circuit board (PCB) transmission line is de-embedded by splitting the measured transmission matrix of the through line on the PCB in half and incorporating one half into the ideal model of the terminations. See the Calibration and Error Correction section for details.

## **SERIAL INTERFACE TIMING SPECIFICATIONS**

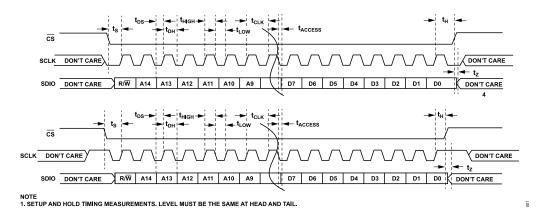

Figure 2. SPI Timing Diagram

Table 2. SPI Timing Specifications

| Parameter       | Description                                                                                          | Min | Тур | Max | Unit |

|-----------------|------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| t <sub>DS</sub> | Setup time between data and rising edge of SCLK                                                      | 15  |     |     | ns   |

| t <sub>DH</sub> | Hold time between data and rising edge of SCLK                                                       | 15  |     |     | ns   |

| CLK             | Clock period                                                                                         | 150 |     |     | ns   |

| ls              | Setup time between $\overline{\text{CS}}$ and SCLK                                                   | 40  |     |     | ns   |

| н               | Hold time between $\overline{\text{CS}}$ and SCLK                                                    | 40  |     |     | ns   |

| HIGH            | Minimum period that SCLK must be in a logic high state                                               | 75  |     |     | ns   |

| LOW             | Minimum period that SCLK must be in a logic low state                                                | 75  |     |     | ns   |

| Z               | Maximum time delay between $\overline{\text{CS}}$ deactivation and SDIO bus return to high impedance |     |     | 150 | ns   |

| ACCESS          | Maximum time delay between falling edge of SCLK and output data valid for a read operation           |     |     | 30  | ns   |

analog.com Rev. A | 5 of 32

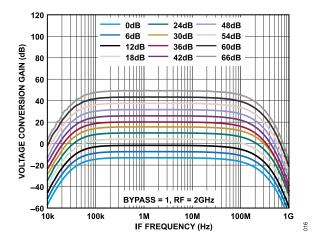

Voltage gain from RF input to differential IF output, with high-impedance IF load. Although the FGAIN and RGAIN bit fields are seven bits wide, values beyond 0x42 are of limited practical use because amplified noise starts to saturate the IF output drivers.

$<sup>^3</sup>$  Second RF tone power = 0 dBm, frequency =  $f_{RF}$  + 100 kHz.

Magnitude relative to the desired output at f<sub>IF</sub> = 500 kHz.

## **ABSOLUTE MAXIMUM RATINGS**

Table 3. Absolute Maximum Ratings

| Parameter                           | Rating                 |  |  |

|-------------------------------------|------------------------|--|--|

| Supply Voltage (AVCC and OVCC)      | 5.5 V                  |  |  |

| RFIN, RFOUT Input AC Power          |                        |  |  |

| Average <sup>1</sup>                | 30 dBm                 |  |  |

| Peak <sup>1</sup>                   | 35 dBm                 |  |  |

| DC Voltage                          |                        |  |  |

| RFIN, RFOUT to AGND <sup>1</sup>    | -5 V to +10 V          |  |  |

| OVDD                                | -0.3 V to +3.8 V       |  |  |

| SCK, <del>CS</del> , and SDIO       | -0.3 V to OVDD + 0.3 V |  |  |

| IFFP, IFFM, IFRP, IFRM <sup>2</sup> | -0.3 V to OVCC + 0.3 V |  |  |

| Any Other Pin <sup>3</sup>          | -0.3 V to AVCC + 0.3 V |  |  |

| DC Current RFIN to or from RFOUT    | 100 mA                 |  |  |

| Temperature                         |                        |  |  |

| ${\sf Maximum}\ {\sf T_J}$          | 150°C                  |  |  |

| T <sub>A</sub> Operating Range      | -40°C to +105°C        |  |  |

| Storage Range                       | -65°C to +150°C        |  |  |

- Not production tested. Guaranteed by design and correlation to production tested parameters. Peak power duty cycle is 10% maximum.

- The voltage on these pins must not exceed 5.5 V, OVCC + 0.3 V, or be less than –0.3 V.

- The voltage on these pins must not exceed 5.5 V, AVCC + 0.3 V, or be less than -0.3 V.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

Thermal performance is directly linked to PCB design and operating environment. Careful attention to PCB thermal design is required.

$\theta_{JA}$  is the junction to ambient (or die to ambient) thermal resistance measured in a one cubic foot sealed enclosure, and  $\theta_{JC}$  is the junction to case (or die to package) thermal resistance.

Table 4. Thermal Resistance

| Package<br>Type <sup>1</sup> | $\theta_{JA}$ | $\theta_{JB}^2$ | θ <sub>JCT</sub> <sup>3</sup> | θ <sub>JCB</sub> <sup>4</sup> | $\Psi_{JT}$ | $\Psi_{JB}$ | Unit |

|------------------------------|---------------|-----------------|-------------------------------|-------------------------------|-------------|-------------|------|

| CC-26-2                      | 39.32         | 13.10           | 30.09                         | 7.63                          | 1.30        | 12.95       | °C/W |

- Test Condition 1: thermal impedance simulated values are based upon use of 2S2P JEDEC PCB. See the Ordering Guide.

- $^{2}$   $\theta_{JB}$  is the junction-to-board thermal resistance.

- $^{3}$   $\theta_{JCT}$  is the junction-to-case top thermal resistance.

- $^4$   $\theta_{JCB}$  is the junction-to-case bottom thermal resistance.

#### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

analog.com Rev. A | 6 of 32

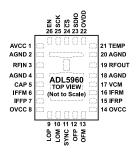

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

NOTES

1. EXPOSED PAD. THE EXPOSED PAD (EPAD) ON THE UNDERSIDE OF THE DEVICE IS ALSO INTERNALLY CONNECTED TO GROUND AND REQUIRES GOOD THERMAL AND ELECTRICAL CONNECTION TO THE GROUND OF THE PRINTED CIRCUIT BOARD (PCB).

CONNECT ALL GROUND PINS TO A LOW IMPEDANCE GROUND PLANE TOGETHER WITH THE EPAD.

Figure 3. Pin Configuration

## Table 5. Pin Function Descriptions

| Pin No.      | Mnemonic                  | Description                                                                                                                                                                                                                                                             |

|--------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1            | AVCC                      | Analog Positive Power Supply Pin. Bypass by placing 1 nF and 4.7 µF capacitors as closely as possible to the AVCC pin.                                                                                                                                                  |

| 2, 4, 18, 20 | AGND                      | Analog Ground Pins. All ground pins are internally connected. Use Pin 2 and Pin 4 as the RF return ground for the RFIN transmission line (Pin 3). Use Pin 18 and Pin 20 as the RF return ground for the RFOUT transmission line (Pin 19).                               |

| 3, 19        | RFIN, RFOUT               | RF Input/Output of the Primary Transmission Line. RFIN and RFOUT have a 50 $\Omega$ load characteristic impedance and can DC-couple to a source and load. When using open and short terminations, do not exceed the maximum power dissipation ratings.                  |

| 5            | CAP                       | Bypass Capacitor. A 100 nF capacitor is recommended for 10 MHz operation.                                                                                                                                                                                               |

| 6, 7, 15, 16 | IFFM, IFFP,<br>IFRP, IFRM | Differential IF Outputs. Pin 6 and Pin 7 are coupled to the forward power transfer (from RFIN to RFOUT). Pin 15 and Pin 16 are coupled to the reverse power transfer (from RFOUT to RFIN).                                                                              |

| 8, 14        | OVCC                      | IF Amplifier Positive Power Supply Pin. Bypass OVCC with a 1 nF and a 4.7 μF capacitor on each pin before connecting to AVCC. Place the capacitors as closely as possible to OVCC.                                                                                      |

| 9, 10        | LOP, LOM                  | Downconversion Mixer LO Inputs. LOP and LOM are internally terminated with a 100 $\Omega$ differential. A differential or single-ended signal source can drive the LOP and LOM pins. Register 0x20 configures the LO interface.                                         |

| 11           | SYNC                      | Synchronization Input. This CMOS input pin stops the dividers in the LO and IF input interfaces when driven high and initiates synchronization when driven back low. If left floating, an internal 415 kΩ pull-down resistor disables the SYNC function.                |

| 12, 13       | OFP, OFM                  | IF Offset Reference Frequency Inputs. The OFP and OFM pins set the center frequency at the IF outputs when the OFMODE bit field in Register 0x20 equals 0x0, 0x1, or 0x2. Setting OFMODE to 0x3 disables this input.                                                    |

| 17           | VCM                       | IF Output Common-Mode Voltage Control. The VCM pin sets the output common-mode voltage at IFFM, IFFP, IFRP, and IFRM. Floats to OVCC/2 if left open.                                                                                                                    |

| 21           | TEMP                      | Temperature Sensing Diode. The TEMP pin connects to the anode of an on-chip junction diode. TEMP can be used to measure the die temperature by measuring the voltage at this pin, while forcing a known current into the pin.                                           |

| 22           | OVDD                      | SPI Positive Power Supply Pin. Connect this pin to the power supply of the SPI controller to avoid the need of voltage level translators in the SPI bus connections.                                                                                                    |

| 23           | SDIO                      | SPI Data Input/Output. If the SDIO pin is floating, an internal 415 kΩ pull-down resistor pulls the pin to logic low.                                                                                                                                                   |

| 24           | CS                        | SPI Chip Select (Active Low). If the $\overline{\text{CS}}$ pin is floating, an internal 415 k $\Omega$ pull-up resistor ties the pin to OVDD.                                                                                                                          |

| 25           | SCK                       | SPI Clock Input. If SCK is left floating, an internal 415 kΩ pull-down resistor pulls the pin to logic low.                                                                                                                                                             |

| 26           | EN                        | Chip Enable. A logic high at the EN pin enables the chip. A logic low at the EN pin shuts down the ADL5960. If EN is left floating, an internal 415 kΩ pull-down resistor disables the ADL5960.                                                                         |

|              | EPAD                      | Exposed Pad. The exposed pad (EPAD) on the underside of the device is also internally connected to ground and requires good thermal and electrical connection to the ground of the PCB. Connect all ground pins to a low impedance ground plane together with the EPAD. |

analog.com Rev. A | 7 of 32

## TYPICAL PERFORMANCE CHARACTERISTICS

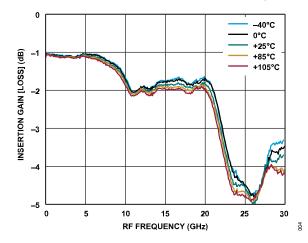

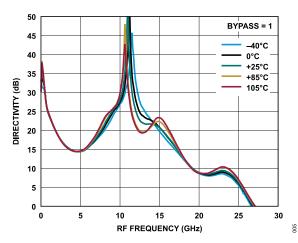

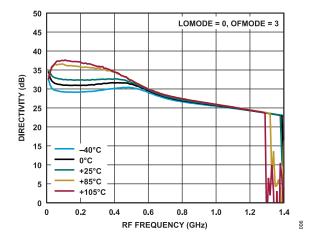

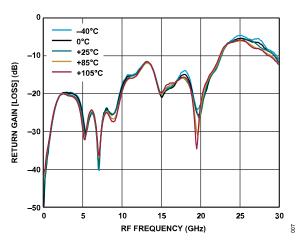

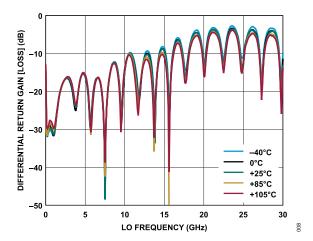

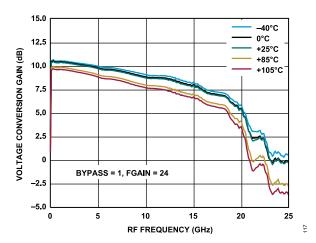

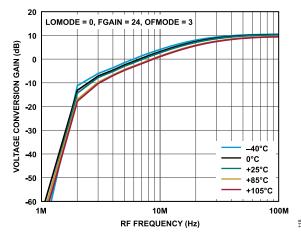

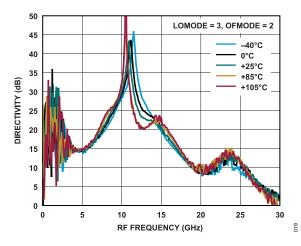

AVCC = OVCC = 5.0 V, EN = OVDD = 3.3 V, VCM = 2.5 V,  $T_A$  = 25°C, 50  $\Omega$  source and load impedance, continuous wave input at RFIN,  $Z_O$  = 50  $\Omega$ ,  $P_{RF}$  = 0 dBm, LO drive single-ended,  $P_{LO}$  = 0 dBm,  $f_{RF}$  = 1 GHz, and  $f_{LO}$  =  $f_{RF}$  + 500 kHz, unless otherwise noted. BYPASS = 1, FGAIN = RGAIN = 24, CIF1 = CIF2 = 15. Test circuit shown in Figure 72.

Figure 4. RFIN to RFOUT Insertion Gain (Loss) vs. RF Frequency at Various Temperatures

Figure 5. Directivity vs. RF Frequency at Various Temperatures, BYPASS = 1

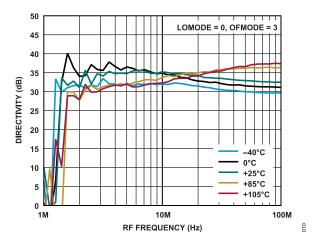

Figure 6. Directivity vs. RF Frequency at Various Temperatures, LOMODE = 0, OFMODE = 3

Figure 7. RFIN, RFOUT Return Gain (Loss) vs. RF Frequency at Various Temperatures

Figure 8. LO Differential Return Gain (Loss) vs. Frequency at Various Temperatures,  $Z_0 = 100 \ \Omega$

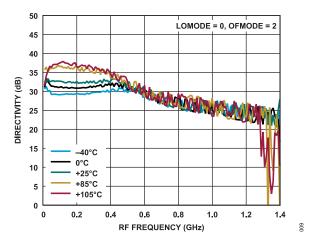

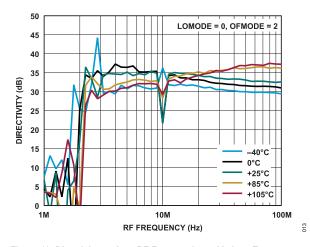

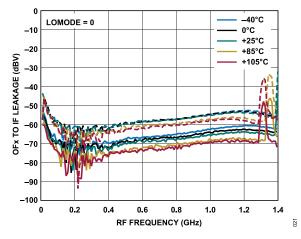

Figure 9. Directivity vs. RF Frequency at Various Temperatures, LOMODE = 0, OFMODE = 2

analog.com Rev. A | 8 of 32

## TYPICAL PERFORMANCE CHARACTERISTICS

Figure 10. Directivity vs. Low RF Frequencies at Various Temperatures, LOMODE = 0, OFMODE = 3

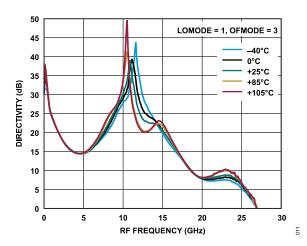

Figure 11. Directivity vs. RF Frequency at Various Temperatures, LOMODE = 1, OFMODE = 3

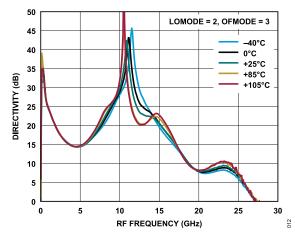

Figure 12. Directivity vs. RF Frequency at Various Temperatures, LOMODE = 2, OFMODE = 3

Figure 13. Directivity vs. Low RF Frequencies at Various Temperatures, LOMODE = 0, OFMODE = 2

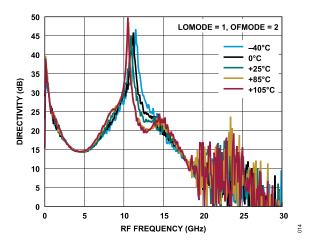

Figure 14. Directivity vs. RF Frequency at Various Temperatures, LOMODE = 1, OFMODE = 2

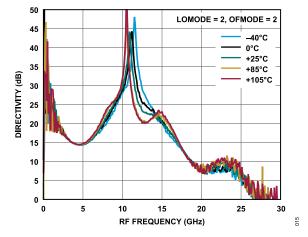

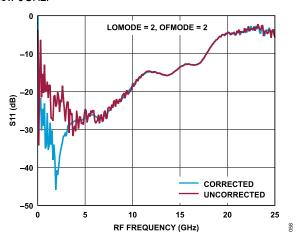

Figure 15. Directivity vs. RF Frequency at Various Temperatures, LOMODE = 2, OFMODE = 2

analog.com Rev. A | 9 of 32

## TYPICAL PERFORMANCE CHARACTERISTICS

Figure 16. Directivity vs. RF Frequency at Various Temperatures, LOMODE = 3, OFMODE = 3

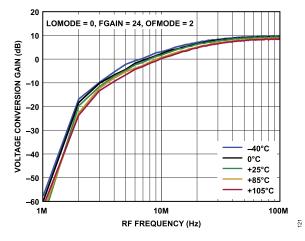

Figure 17. Voltage Conversion Gain vs. RF Frequency at Various Temperatures

Figure 18. Voltage Conversion Gain at Low RF Frequencies at Various Temperatures, LOMODE = 0, OFMODE = 3

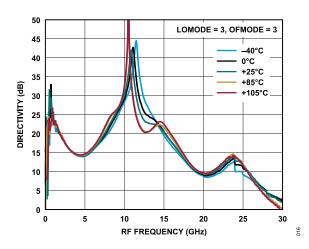

Figure 19. Directivity vs. RF Frequency at Various Temperatures, LOMODE = 3, OFMODE = 2

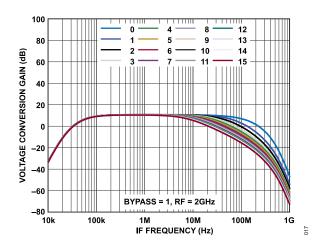

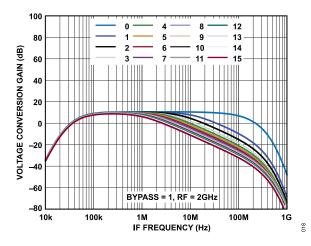

Figure 20. Voltage Conversion Gain vs. IF Frequency and FGAIN/RGAIN Settings

Figure 21. Voltage Conversion Gain at Low RF Frequencies at Various Temperatures, LOMODE = 0, OFMODE = 2

analog.com Rev. A | 10 of 32

## TYPICAL PERFORMANCE CHARACTERISTICS

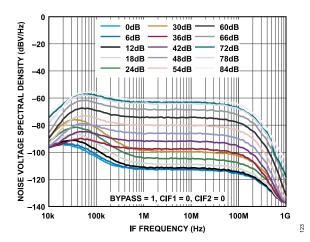

Figure 22. Voltage Conversion Gain vs. IF Frequency and CIF1 Setting, CIF2 = 0

Figure 23. Differential IF Output-Noise Voltage Spectral Density vs. IF Frequency and Gain Settings (FGAIN, RGAIN), CIF1 = CIF2 = 0

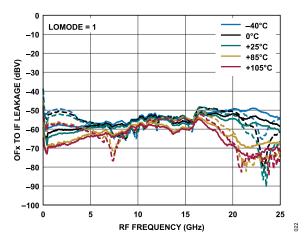

Figure 24. OFx to IF Leakage for Various Temperatures, LOMODE = 0, OFMODE = 2. Drawn: Forward Channel, Dashed: Reverse Channel

Figure 25. Voltage Conversion Gain vs. IF Frequency and CIF2 Setting, CIF1 = 0

Figure 26. Noise Figure vs. RF Frequency and IF Gain Settings

Figure 27. OFx to IF Leakage for Various Temperatures, LOMODE = 1, OFMODE = 2. Drawn: Forward Channel, Dashed: Reverse Channel

analog.com Rev. A | 11 of 32

## TYPICAL PERFORMANCE CHARACTERISTICS

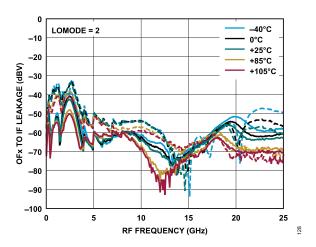

Figure 28. OFx to IF Leakage for Various Temperatures, LOMODE = 2, OFMODE = 2. Drawn: Forward Channel, Dashed: Reverse Channel

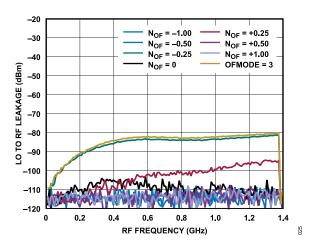

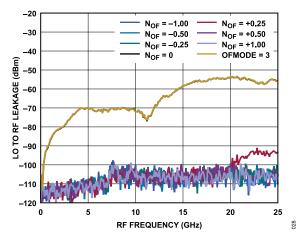

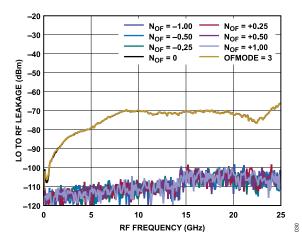

Figure 29. LO to RF Leakage for LOMODE = 0, Measurement Frequency =  $f_{RF}$  +  $N_{OF}$  ×  $f_{OF}$  for OFMODE = 2, and  $f_{RF}$  +  $f_{IF}$  for OFMODE = 3

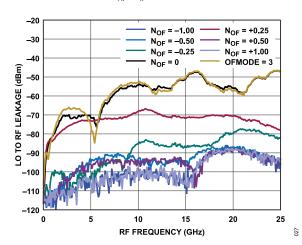

Figure 30. LO to RF Leakage for LOMODE = 1, Measurement Frequency =  $f_{RF}$  +  $N_{OF}$  ×  $f_{OF}$  for OFMODE = 2, and  $f_{RF}$  +  $f_{IF}$  for OFMODE = 3

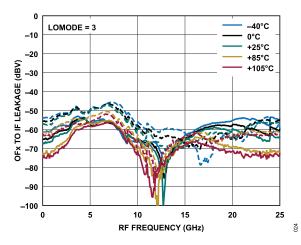

Figure 31. OFx to IF Leakage at Various Temperatures, LOMODE = 3, OFMODE = 2, Drawn: Forward Channel, Dashed: Reverse Channel

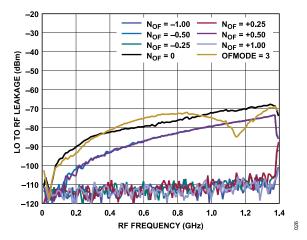

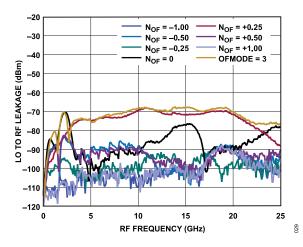

Figure 32. LO to RF Leakage for LOMODE = 0, Measurement Frequency =  $2 \times f_{RF} + N_{OF} \times f_{OF}$  for OFMODE = 2, and  $2 \times f_{RF} + f_{IF}$  for OFMODE = 3

Figure 33. LO to RF Leakage for LOMODE = 2, Measurement Frequency =  $f_{RF}/2 + N_{OF} \times f_{OF}$  for OFMODE = 2, and  $f_{RF}/2 + f_{IF}$  for OFMODE = 3

analog.com Rev. A | 12 of 32

## TYPICAL PERFORMANCE CHARACTERISTICS

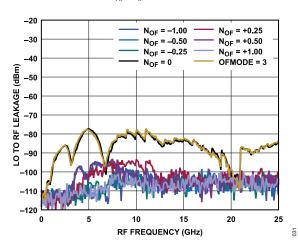

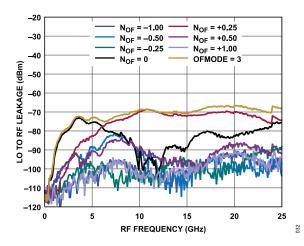

Figure 34. LO to RF Leakage for LOMODE = 2, Measurement Frequency =  $f_{RF}$  +  $N_{OF}$  ×  $f_{OF}$  for OFMODE = 2, and  $f_{RF}$  +  $f_{IF}$  for OFMODE = 3

Figure 35. LO to RF Leakage for LOMODE = 3, Measurement Frequency =  $f_{RF}/2 + N_{OF} \times f_{OF}$  for OFMODE = 2, and  $f_{RF}/2 + f_{IF}$  for OFMODE = 3

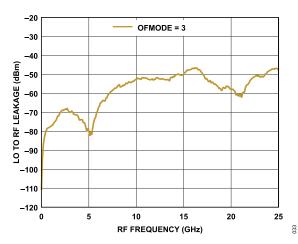

Figure 36. LO to RF Leakage for BYPASS = 1, Measurement Frequency =  $f_{RF} + f_{IF}$

Figure 37. LO to RF Leakage for LOMODE = 3, Measurement Frequency =  $f_{RF}/4 + N_{OF} \times f_{OF}$  for OFMODE = 2, and  $f_{RF}/4 + f_{IF}$  for OFMODE = 3

Figure 38. LO to RF Leakage for LOMODE = 3, Measurement Frequency =  $f_{RF}$  +  $N_{OF}$  ×  $f_{OF}$  for OFMODE = 2, and  $f_{RF}$  +  $f_{IF}$  for OFMODE = 3

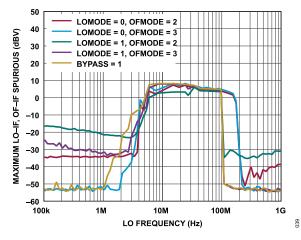

Figure 39. Maximum LO to IF, OF to IF Spurious Tone Levels vs. LO Frequency, CIF1 = CIF2 = 0

analog.com Rev. A | 13 of 32

## **TYPICAL PERFORMANCE CHARACTERISTICS**

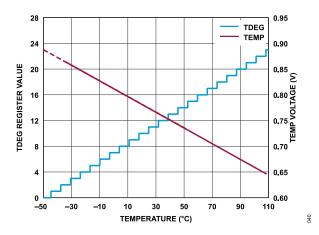

Figure 40. TDEG Register Value and TEMP Voltage vs. Temperature  $(I_{TEMP} = 42 \mu A)$

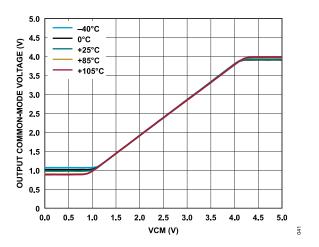

Figure 41. IF Output Common-Mode Voltage vs. Voltage at VCM Interface (VCM) at Various Temperatures

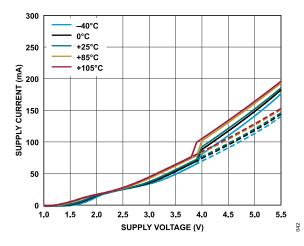

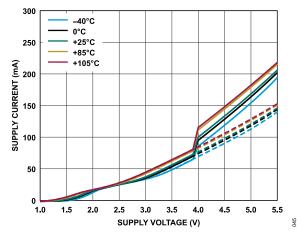

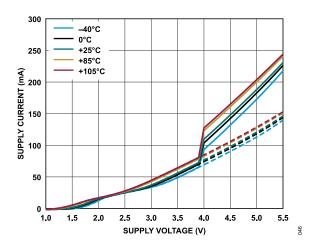

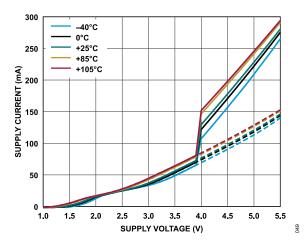

Figure 42. Supply Current vs. Supply Voltage at Various Temperatures, LOMODE = 0, Drawn: OFMODE = 2, Dashed: OFMODE = 3

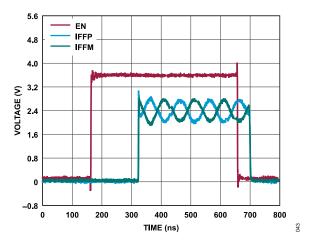

Figure 43. Turn-On/Off Time with Continuous Wave RF = 1 GHz, 10 dBm, IF = 10 MHz, 50  $\Omega$  Load at IFFP and IFFM

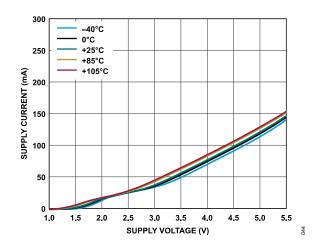

Figure 44. Supply Current vs. Supply Voltage at Various Temperatures, BYPASS = 1

Figure 45. Supply Current vs. Supply Voltage at Various Temperatures, LOMODE = 1, Drawn: OFMODE = 2, Dashed: OFMODE = 3

analog.com Rev. A | 14 of 32

## TYPICAL PERFORMANCE CHARACTERISTICS

Figure 46. Supply Current vs. Supply Voltage at Various Temperatures, LOMODE = 2, Drawn: OFMODE = 2, Dashed: OFMODE = 3

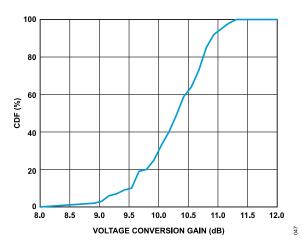

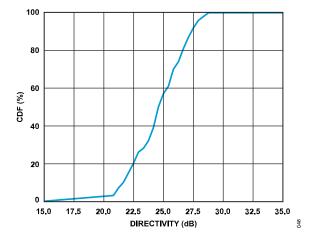

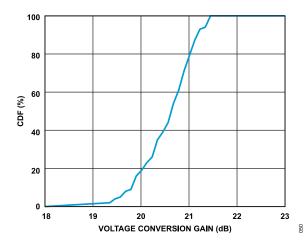

Figure 47. Conversion Gain Distribution, FGAIN = 24, Sample Size 100

Devices (CDF = Cumulative Distribution Function)

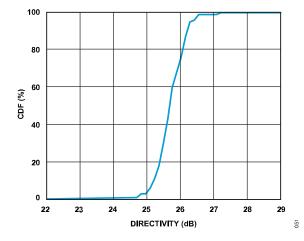

Figure 48. Directivity Distribution, RF = 1 GHz, Sample Size 100 Devices

Figure 49. Supply Current vs. Supply Voltage at Various Temperatures, LOMODE = 3, Drawn: OFMODE = 2, Dashed: OFMODE = 3

Figure 50. Conversion Gain Distribution, FGAIN = 36, Sample Size 100

Devices

Figure 51. Directivity Distribution, RF = 10 GHz, Sample Size 100 Devices

analog.com Rev. A | 15 of 32

## THEORY OF OPERATION

The ADL5960 is designed to enable broadband multiport network analyzer solutions in a small footprint.

The ADL5960 is built around an integrated broadband bidirectional resistive bridge and coupled to broadband dual downconversion mixers. The differential IF outputs of the mixers are passed through low-pass filters with SPI-programmable bandwidth and IF amplifiers with individually SPI-programmable gain.

The LO interface to the mixers supports multiple SPI-programmable configurations, and is designed to simplify the frequency plan in a vector network analyzer application. The LO interface contains frequency multipliers and dividers that enable a wider frequency range of operation than supported by the LO signal source itself. A second input to the LO interface, the offset interface formed by the OFP and OFM pins, enables a zero-offset operating mode with greatly simplified frequency plan. In this mode, only a single swept high-frequency signal source is needed, driving both the RF and LO interfaces of the ADL5960. The signal supplied to the OF interface controls the frequency of the IF output signal as it mixes with the LO signal supplied to the LOP/LOM interface before driving the downconversion mixers.

Multiple ADL5960 devices can be phase synchronized and operated simultaneously, which enables the construction of small footprint multiport network analyzers using one ADL5960 device per network analyzer port.

# BASIC ONE-PORT VECTOR NETWORK ANALYZER

A one-port vector network analyzer, or reflectometer, can be used to measure the magnitude and phase of the reflection coefficient of an unknown load vs. frequency.

Figure 52 shows the basic configuration of a one-port analyzer based on the ADL5960. The RFIN interface of the ADL5960 connects to the RF signal source (typically continuous wave), while the RFOUT interface connects to the unknown load, the device under test (DUT). Because the ADL5960 is completely symmetric, the RF source can also be connected to RFOUT and the load to RFIN. The RF source injects an incident RF signal into the directional bridge of the ADL5960, traveling from the source to the load. At the load, part of this incident power wave is reflected and travels back to the source, while the other part is absorbed by the load. The reflection coefficient to be measured (both magnitude and phase) equals the ratio of the reflected power to the incident power at the load. For proper operation of the bidirectional bridge, it is important that the RF signal source has a 50  $\Omega$  characteristic impedance. The LO interface can either be driven by a 50 Ω single-ended source or a 100  $\Omega$  differential source.

The directional bridge on the ADL5960 supplies a fraction of the incident signal to the input of the forward IF channel, and, likewise, a fraction of the reflected signal to the input of the reverse IF channel. Both these IF signals are downconverted, filtered, amplified, and made available at the differential IF channel output interfaces, IFFx

(with the IFFP and IFFM terminals) and IFRx (with the IFRP and IFRM terminals), respectively.

After analog-to-digital conversion, the IF output signals representing the incident and reflected waves are digitally quadrature (complex) downconverted, filtered, and decimated. Finally, their ratio (reflected/forward) is calculated to obtain the (complex) reflection coefficient.

Figure 52. ADL5960 Used as One-Port VNA (Reflectometer)

# FREQUENCY PLANNING—LO CONFIGURATIONS

The LO interface of the ADL5960 supports several different configurations, some of which significantly simplify the VNA configuration in exchange for slightly degraded accuracy.

The bypass mode, selected by setting Bit 4 in Register 0x20, is the most basic and highest performance mode of operation of the ADL5960. In this mode, the LO signal supplied to the LO interface (that is, the LOP and LOM pins) directly drives the downconversion mixers, bypassing the frequency multipliers, dividers, and offset mixer. To maintain a fixed IF output frequency, the LO signal must maintain a fixed frequency offset relative to the RF signal across the entire frequency sweep.

$$f_{LO} = f_{RF} \pm f_{IF} \tag{1}$$

The + sign corresponds to high-side injection, and the - sign corresponds to low-side injection. High-side injection often results in slightly improved dynamic range, because more of the mixing products calculate out at higher frequencies than the desired IF signal and can be suppressed by low-pass filtering. The ADL5960 supports IF frequencies up to 100 MHz. For high dynamic range analog-to-digital conversion, an IF frequency of a few MHz is often preferable, but an IF of 2 MHz to 3 MHz creates challenges for the signal sources, requiring an accurate, small frequency offset of a few MHz between RF and LO up to 20 GHz signal frequencies.

The frequency divider and frequency multipliers integrated into the LO interface of the ADL5960 enable measurement sweeps beyond the frequency range supported by the LO source itself, typically

analog.com Rev. A | 16 of 32

#### THEORY OF OPERATION

a frequency synthesizer. When Bit 4 in Register 0x20 is cleared (disabling bypass mode), the LOMODE bit field in Bits[1:0] can be used to program the LO multiplication factor,  $M_{LO}$  as seen in the following equation:

$$M_{LO} = 2^{\text{LOMODE} - 1} \tag{2}$$

That is, divide by 2, or multiply by 1, 2, or 4. To ensure that the desired output signal downconverts at the desired IF output frequency,  $f_{\rm IF}$ , the frequency supplied to the LO interface must meet the following condition:

$$f_{LO} = (f_{RF} \pm f_{IF})/M_{LO} \tag{3}$$

Note from Table 1 that the divide-by-two mode can only be used for LO input frequencies up to 2.4 GHz, whereas the doubler and quadrupler modes only operate from 2 GHz to 8 GHz and from 4 GHz to 8 GHz, respectively. The LO interface also contains high-frequency filters that suppress the harmonics and subharmonics in the multiplier outputs. The center frequency of these filters can be programmed through Register 0x21 and Register 0x22.

# **OF INTERFACE**

Further simplification of the VNA configuration can be achieved by employing the differential offset frequency (OF) interface. In this configuration, a single swept source can be used to drive the RF and LO interfaces at the same frequency (zero frequency offset), while the IF output frequency is set by the signal applied to the OF interface. To enable the offset mixer, clear Bit 4 in Register 0x20 and program the OFMODE bit field in Bits[3:2]. The offset frequency input interface, when enabled, contains a programmable divider with ratios of 1, 2, and 4. The multiplication factor, M<sub>OF</sub>, is as shown in Table 6.

Table 6. Offset Input Configuration

| Register 0x20 [3:2] OFMODE | Divide by    | M <sub>OF</sub> |

|----------------------------|--------------|-----------------|

| 00                         | 1            | 1               |

| 01                         | 2            | 0.5             |

| 10 (default)               | 4            | 0.25            |

| 11                         | Dividers off | Not applicable  |

The IF output signal frequency, including the offset mixer, can be represented as follows:

$$f_{IF} = f_{RF} - M_{LO} \times f_{LO} + M_{OF} \times f_{OF} \tag{4}$$

For a true zero-offset sweep the LO frequency therefore needs to satisfy the following:

$$f_{LO} = f_{RF}/M_{LO} \tag{5}$$

such that the first two terms of Equation 4 cancel out, and the IF output frequency equals the following:

$$f_{IF} = M_{OF} \times f_{OF} \tag{6}$$

The setting  $M_{OF} = 1/4$  (OFMODE = 2) is particularly useful and is the recommended OFMODE setting. When the OF interface is driven by the ADC sample clock frequency,  $f_s$ , it precisely centers the IF output signal in the first Nyquist zone of the ADC, with four time domain sample points per complete cycle of IF waveform. In this mode, the discrete time nature of the IF waveform becomes evident due to the divide-by-4 digital dividing of the offset input.

## IF SIGNAL PATH

The IF output signal of the mixers is passed through low-pass filters to remove unwanted mixing products and noise. The bandwidth of these filters is SPI-programmable through Register 0x25. The same bandwidth setting is applied to both ADL5960 IF channels.

The IF amplifiers that follow the low-pass filters have individually SPI-programmable gain, adjustable in 6 dB steps. This programmable gain enables optimal interfacing of both channels to the ADC input dynamic range.

The IF output interfaces of the ADL5960 are suited to drive a wide range of ADCs directly. To avoid aliasing of broadband noise, it is recommended to insert a simple antialiasing filter as shown in Figure 53.

Figure 53. Interfacing the ADL5960 to an ADC

Each of the differential IF output nodes are low source impedance. For this reason, it is recommended to use series resistors when necessary, such as for driving filters or highly capacitive loads or cables, as shown on the test circuit.

#### MULTIPORT VECTOR NETWORK ANALYZER

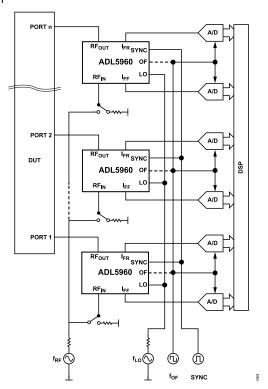

The ADL5960 can also be used to create network analyzers consisting of multiple ports, as shown in Figure 54. Each port connects to one ADL5960 device, and RF switches route the RF signal to one ADL5960 at a time. For optimum phase (and magnitude) accuracy, ensure the connections from the RF source to all ports are equal in length. Further, terminate the RFIN ports of the ADL5960 devices with 50  $\Omega$  at all times, that is, when the RF source is connected but also when the source is not connected to the port. A suitable way to achieve this is by using an SPxT nonreflective switch with the RF source connected to the pole. For VNAs with many ports, a cascade of nonreflective (terminated) RF switches can be used at the expense of larger insertion loss and potentially increased frequency tilt. Note that the connections to the RF source as drawn in Figure 54 are overly simplified, and do not by any means follow the recommendations for an optimal layout of the system.

analog.com Rev. A | 17 of 32

#### THEORY OF OPERATION

Phase synchronization between the ADL5960 devices is achieved through the LO and offset frequency signals. For optimal accuracy, it is preferable to match the propagation delays from the LO source to each of the ADL5960 devices. Residual delay differences can be addressed through calibration procedures for the VNA system. Routing of the signal lines to the offset interface is less critical, because these operate at much lower frequencies.

The SYNC interface is used to force the LO and offset dividers in all ADL5960 devices to the same known initial state, such that no phase ambiguities exist between the devices. A single pulse applied to this input after power-on is sufficient to synchronize all devices. Perform this synchronization before an LO signal is applied. In that case the timing of the SYNC pulse is not critical.

For the optimal accuracy, simultaneous sampling of all ADL5960 IF channels is recommended. For high port counts, a multichannel simultaneous sampling ADC can significantly reduce the solution footprint. Some of these multichannel devices include built-in digital downconversion (DDC) and decimation filters, which reduce the amount of processing required in the digital signal processor (DSP).

The performance of the system can further be enhanced by inserting a programmable RF filter in the RF path to filter any harmonic content of the RF source, and a programmable attenuator to compensate for tilt vs. frequency introduced by filters, switches, and transmission lines.

Figure 54. Multiport Vector Network Analyzer Based on the ADL5960

analog.com Rev. A | 18 of 32

#### THEORY OF OPERATION

#### CALIBRATION AND ERROR CORRECTION

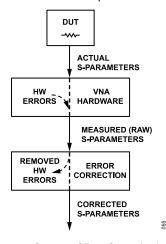

The accuracy of S-parameter measurements is prone to a variety of errors introduced by the hardware in vector network analyzers. Systematic errors, those that are repeatable and predictable, can be eliminated from the measurement results using calibration and error correction techniques. The types of systematic errors that can be eliminated (to a certain extent) include the following:

- ▶ Impedance mismatches

- ▶ Gain and insertion loss differences between channels

- Crosstalk between channels

Various error correction and calibration techniques have been developed over the years (see, for example, *D. K. Rytting, "Network Analyzer Accuracy Overview," 58th ARFTG Conference Digest, 2001, pp. 1-13, doi: 10.1109/ARFTG.2001.327486*) that differ in their effectiveness to eliminate certain errors, complexity, and calibration standards used. The general principals that are applied, however, are the same for all. The systematic errors are determined by measuring the VNA response for a set of DUTs with accurately known S-parameters—the calibration standards. Comparing the measured S-parameters with the known S-parameters allows calculation of the error coefficients. These error coefficients, combined into what is often referred to as an error adapter, can then be used in a postprocessing step to calculate the error corrected S-parameters from the measured S-parameters of an unknown DUT. Figure 55 illustrates the concept.

Figure 55. Concept of Error Correction in VNAs

Different error correction techniques require the use of different sets of calibration standards. Some of the most well known include short, open, load, thru (SOLT), thru, reflect, line (TRL), and thru, reflect, match (TRM). The standards within a set are chosen to have significantly different S-parameters, such that they span a large area on the Smith chart. The calibration standards themselves, particularly the ones with extreme S-parameter values such as short and open standards, are typically not completely ideal either and usually include a manufacturer supplied model for the S-parameters

vs. frequency. In general, calibration standards can be subdivided into the two following categories:

- ▶ One-port calibration standards, measured at each VNA port

- Two-port calibration standards, measured for each combination of VNA ports

The calibration procedure for a VNA built from ADL5960 devices is similar to that for any other VNA system. For maximum accuracy, it is important to note that the frequencies used. Additionally, the ADL5960 SPI gain, bandwidth, and frequency multiplier/divider settings used during calibration must exactly match the settings used during an actual DUT measurement. Calibrate the VNA for multiple different configurations if the settings are expected to be different during an actual measurement because gain and other settings are subject to device-to-device and channel-to-channel spread (mismatch).

Although S-parameters are the result of a power ratio calculation and, in principle, independent of absolute power levels, it is often important to accurately control the RF source power vs. frequency during a measurement. When the DUT exhibits nonlinearity across the applied RF power levels, such as semiconductor devices, a change in power level can result in a change of the DUT behavior that affects the measurement accuracy. The ADL5960 forward IF channel can be used to monitor the power levels in the RF signal path, particularly when the port is terminated with 50  $\Omega$ , such as during calibration of the system with a load standard. The conversion gain of the ADL5960 itself does exhibit roll-off vs. frequency as well, which must be taken into account to achieve an accurate power measurement.

#### **One-Port Calibration**

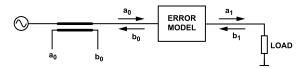

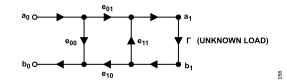

The calibration procedure for a one-port S-parameter measurement can be explained using the flow diagram in Figure 56 (see also D. K. Rytting, "Network Analyzer Accuracy Overview," 58th ARFTG Conference Digest, 2001, pp. 1-13, doi: 10.1109/ARFTG.2001.327486). The directional coupler and error model together describe the operation of a practical VNA. The incident wave,  $a_0$ , and reflected wave,  $b_0$ , represent the forward and reverse power measured by the VNA. When using the ADL5960, these vectors are obtained from the IF outputs, IFFx and IFRx. The actual power incident on the load is represented by  $a_1$ , whereas  $b_1$  represents the actual power reflected by the load. An error-free VNA measures  $a_1$  and  $b_1$ .

analog.com Rev. A | 19 of 32

## THEORY OF OPERATION

Figure 56. Error Model for One-Port S-Parameter Measurements

The flow diagram provides a more detailed description of the various error contributions that cause the measured reflection coefficient,  $\Gamma_M = b_0/a_0$ , to differ from the actual reflection coefficient,  $\Gamma = b_1/a_1$ . The factor,  $e_{11}$ , represents impedance mismatch of the VNA port (from 50  $\Omega$ ). A fraction of  $b_1$  is reflected back to the load. The  $e_{01}$  and  $e_{10}$  factors represent the tracking error. In relation to the ADL5960, the tracking error comprises insertion loss of the bridge, the conversion gain from RFIN to IFFx and RFOUT to IFRx, as well as the mismatch in conversion gain between the channels. Finally,  $e_{00}$  represents the finite directivity of a practical VNA, a measure for the ability to separate the forward and reverse traveling power waves. If the load is a perfect 50  $\Omega$ , then  $b_1$  = 0 and an ideal VNA measures  $b_0$  = 0. However, in a practical VNA, the directivity is finite and some signal leaks from the forward path to the reverse path.

Using Figure 56, the measured reflection coefficient can be expressed in terms of the error coefficients and the reflection coefficient of the load as follows:

$$\Gamma_M = e_{00} + \frac{e_{01}e_{10}}{1 - \Gamma e_{11}} \Gamma \tag{7}$$

Equation 7 can be rearranged into a linear expression for the error coefficients as follows:

$$e_{00} - \Delta_e \Gamma + e_{11} \Gamma_M = \Gamma_M \Delta_e = e_{00} e_{11} - e_{01} e_{10}$$

(8)

A calibration procedure that measures three different known loads, that is, collects three combinations of measured and actual reflection coefficients, can then be used to calculate the error coefficients as follows:

$$\begin{bmatrix}

1 & -\Gamma_1 & \Gamma_{M1} \\

1 & -\Gamma_2 & \Gamma_{M2} \\

1 & -\Gamma_3 & \Gamma_{M3}

\end{bmatrix}

\begin{bmatrix}

e_{00} \\

\Delta_e \\

e_{11} \\

\overrightarrow{e}

\end{bmatrix} = \begin{bmatrix}

\Gamma_{M1} \\

\Gamma_{M2} \\

\Gamma_{M3} \\

\overrightarrow{\Gamma_{M}}

\end{bmatrix} \Rightarrow \overrightarrow{e} = T^{-1} \overrightarrow{\Gamma_{M}}$$

(9)

After the system is calibrated, the corrected reflection coefficient can be calculated from the measured coefficient by rearranging Equation 7:

$$\Gamma = \frac{\Gamma_M - e_{00}}{e_{11}\Gamma_M - \Delta_e} \tag{10}$$

Although in principle any combination of sufficiently different standards can be used to calibrate the system, a combination of a short, an open, and a 50  $\Omega$  load are by far the most common choice. Note that the procedure outlined in Equation 9 needs to be repeated at every frequency point of interest.

#### **Two-Port Calibration**

The calibration procedure for a two-port S-parameter measurement can be explained using Figure 57. The VNA is modeled by Port 0, Port 2, and the error model. As a result of the hardware errors in the system, the measured S-parameters at Port 0 differ from the actual DUT S-parameters observed at Port 1, and the S-parameters measured at Port 2 differ from the DUT S-parameters at Port 3. As long as the error contributions scale linearly with power, the incident and reflected waves at Port 0 and Port 2 can be related to those at Port 1 and Port 3 using a block matrix, as follows:

$$\begin{bmatrix} b_0 \\ a_0 \\ b_2 \\ a_2 \end{bmatrix} = \begin{bmatrix} T_{01} & T_{03} \\ T_{21} & T_{23} \end{bmatrix} \begin{bmatrix} b_1 \\ a_1 \\ b_3 \\ a_3 \end{bmatrix}$$

$$\begin{bmatrix} a_0 \\ b_0 \\ b_0 \end{bmatrix} = \begin{bmatrix} a_1 \\ b_1 \\ b_1 \\ b_1 \end{bmatrix}$$

$$\begin{bmatrix} a_1 \\ b_1 \\ b_1 \\ b_2 \end{bmatrix}$$

$$\begin{bmatrix} a_1 \\ b_1 \\ b_1 \\ b_2 \end{bmatrix}$$

$$\begin{bmatrix} a_1 \\ b_1 \\ b_1 \\ b_2 \end{bmatrix}$$

$$\begin{bmatrix} a_1 \\ b_1 \\ b_1 \\ b_2 \end{bmatrix}$$

$$\begin{bmatrix} a_1 \\ b_1 \\ b_1 \\ b_2 \end{bmatrix}$$

$$\begin{bmatrix} a_1 \\ b_1 \\ b_1 \\ b_2 \end{bmatrix}$$

$$\begin{bmatrix} a_1 \\ b_1 \\ b_1 \\ b_2 \end{bmatrix}$$

$$\begin{bmatrix} a_1 \\ b_1 \\ b_1 \\ b_2 \end{bmatrix}$$

$$\begin{bmatrix} a_1 \\ b_1 \\ b_1 \\ b_2 \end{bmatrix}$$

$$\begin{bmatrix} a_1 \\ b_1 \\ b_1 \\ b_2 \end{bmatrix}$$

$$\begin{bmatrix} a_1 \\ b_1 \\ b_1 \\ b_2 \end{bmatrix}$$

$$\begin{bmatrix} a_1 \\ b_1 \\ b_2 \\ b_2 \end{bmatrix}$$

$$\begin{bmatrix} a_1 \\ b_1 \\ b_1 \\ b_2 \end{bmatrix}$$

$$\begin{bmatrix} a_1 \\ b_1 \\ b_1 \\ b_2 \end{bmatrix}$$

$$\begin{bmatrix} a_1 \\ b_1 \\ b_1 \\ b_2 \end{bmatrix}$$

$$\begin{bmatrix} a_1 \\ b_1 \\ b_1 \\ b_2 \end{bmatrix}$$

$$\begin{bmatrix} a_1 \\ b_1 \\ b_2 \\ b_2 \end{bmatrix}$$

$$\begin{bmatrix} a_1 \\ b_1 \\ b_1 \\ b_2 \\ b_2 \end{bmatrix}$$

$$\begin{bmatrix} a_1 \\ b_1 \\ b_1 \\ b_2 \\ b_2 \end{bmatrix}$$

Figure 57. Error Model for Two-Port S-Parameter Measurements

Each of the matrix elements, T in Equation 11, is a 2×2 matrix that describes the interaction between one VNA port and one DUT port, resulting in a total of 16 unknown error coefficients. A wide range of different calibration strategies are reported in literature to determine either a subset of or all of the error coefficients (matrix elements).

One strategy to simplify the error model assumes that the crosstalk between the VNA channels is negligible, that is, that contributions of Port 1 to measurement errors in Port 2, and contributions of Port 3 to measurement errors in Port 0 are very small. This assumption is plausible in a VNA based on the ADL5960, because each VNA port is realized by a separate device. Interaction between the VNA channels can be minimized through careful PCB layout. For this situation, only the block matrices on the diagonal in Equation 11 have nonzero elements, resulting in the following:

analog.com Rev. A | 20 of 32

# THEORY OF OPERATION

where

$T_{31}$  represents the transmission matrix of the DUT itself (the quantity to be measured).

$T_M$  the transmission matrix measured by the VNA.

The error corrected transmission matrix can then be expressed as follows:

$$T_{CORRECTED} = T_{23}^{-1} T_M T_{01} (13)$$

Many different calibration techniques are available to determine the transmission matrices,  $T_{01}$  and  $T_{23}$ . One of the simplest yet effective methods is the SOLT calibration, in which a one-port calibration that is applied to each port, followed by measurement of a thru connection (short between Port 1 and Port 3).

## **Multiport Calibration**

Calibration of VNAs consisting of more than two ports can be performed along similar procedures as the two-port calibration discussed in Two-Port Calibration. The number of error coefficients to be determined grows quadratically as  $4n^2$ , where n is the number of ports. However, when interactions between the VNA ports can be neglected only the coefficients on the block diagonal of the error model need to be taken into account, resulting in 4n remaining coefficients.

A practical problem arising with multiport calibration is that calibration standards are usually either one-port (loads) or two-port, whereas the calibration procedure, in principle, requires the measured n×n S-matrix and an n×n S-matrix for the actual standard S-parameters. This problem can be addressed by constructing the n-port S-matrix from a series of two-port measurements. Equation 14 illustrates the concept for a four-port system.

$$S = \begin{bmatrix} m_{12} & m_{12} & m_{13} & m_{14} \\ m_{12} & m_{12} & m_{23} & m_{24} \\ m_{13} & m_{23} & m_{13} & m_{34} \\ m_{14} & m_{24} & m_{34} & m_{14} \end{bmatrix}$$

(14)

where  $m_{xy}$  indicate from which two-port measurement the corresponding S-parameter is determined.

For example, a two-port measurement using Port 1 and Port 2, indicated by  $m_{12}$ , can be used to determine  $s_{11}$ ,  $s_{12}$ ,  $s_{21}$ , and  $s_{22}$ . Measurements on different combinations of two ports are needed to fill the entire S-matrix. Some parameters are determined multiple times (like  $s_{11}$ ) and can be disregarded in all but one measurement. In general, the full set of  $n^2$  S-parameters can be determined with n(n-1)/2 two-port measurement sessions.

When the SOLT calibration method is applied to an n-port VNA, for example, it requires measurement of three loads on each port,

followed by a thru standard measurement between all combinations of two ports. The total number of measurement runs required for this is

$$3n + n(n-1)/2 = n(n+5)/2$$

(15)

# **Rejection of IF Spurious Tones**

Besides the desired output signal, a variety of other spurious tones and mixing products are generally present in the IF output signal spectrum. Some of these undesired tones appear at the same frequency as the desired IF signal, and therewith reduce the measurement accuracy. The techniques described in this section can be used to reduce the impact of such undesired tones and enhance the measurement accuracy.

The LO interface configurations that use the OF interface are most vulnerable to IF spurious tones. Harmonics, sub-harmonics, mixing products between the LO and OF, and partially suppressed image frequencies contribute to spurious tones in the IF output spectrum. The impact of spurious tones is most pronounced when the DUT at the RFOUT port is well matched, such that the desired signal in the reverse IF output channel is very small. Figure 58 illustrates the impact of spurious tones at the IF frequency, comparing a return loss measurement result corrected for IF spurious tones and a raw, uncorrected result. As apparent from this figure, spurious tones introduce ripple vs. frequency in the measurement result, and reduce the measurement sensitivity, particularly at frequencies below 5GHz.

Figure 58. Return Loss Measurement of a 50  $\Omega$  Load, With and Without Correction of IF Spurious Tones

The following simple procedure can significantly reduce the ripple due to spurious tones:

- 1. Measure the IF output signal with RF present.

- 2. Calculate the complex fast Fourier transform (FFT) frequency component at the IF output frequency.

- Measure the IF output signal with the RF signal off, or set to a very low level.

analog.com Rev. A | 21 of 32

# THEORY OF OPERATION

- **4.** Calculate the frequency component at the IF frequency for this case.

- **5.** Subtract the result obtained in Step 4 from the result in Step 2.

- **6.** Apply error correction and further processing to the result of Step 5).

The order of the steps described can be changed, and the frequency sweep without RF signal can be stored in memory for correction of future measurements.

analog.com Rev. A | 22 of 32

## **APPLICATIONS INFORMATION**

## INTERFACE DESCRIPTIONS

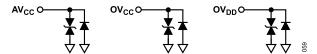

# **Power Supply Interfaces**

The AVCC, OVCC, and OVDD pins have independent supply clamps and must be ramped slower than 100  $\mu$ s to avoid triggering the clamps. Decoupling of the supply interfaces with 1 nF//4.7  $\mu$ F capacitors is recommended to suppress residual high-frequency ripple. OVDD can be connected to the supply of the SPI controller to eliminate the need for logic level translators in the SPI bus lines.

Figure 59. Simplified Power Supply Interface Schematics

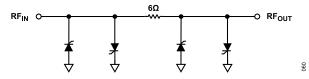

#### RFIN and RFOUT Interface

RFIN and RFOUT are both single-ended RF inputs with 50  $\Omega$  characteristic impedance. Because both interfaces are internally coupled, the input impedance observed at RFIN (or RFOUT) is 50  $\Omega$  if, and only if, the other interface, RFOUT (or RFIN) is terminated with 50  $\Omega$ .

Both pins are internally DC-coupled through a 6  $\Omega$  series resistance of the bidirectional bridge. DC currents up to 100 mA can be safely passed through the bridge to bias a DUT such as an RF amplifier. The bridge is designed to support average signal levels up to 30 dBm in matched conditions and peak levels up to 35 dBm. Signal voltages on the interfaces must stay within the range from –5 V to +10 V under extreme mismatched conditions, such as an open circuit, that can result in larger voltage swings than observed with a matched termination.

Figure 60. Simplified RFIN and RFOUT Interfaces

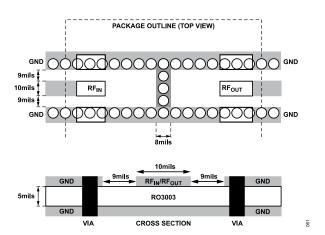

To achieve the best possible bridge directivity, both RFIN and RFOUT must be connected to carefully matched 50  $\Omega$  broadband transmission lines. A grounded coplanar waveguide (GCPW) as shown in Figure 61 is a suitable implementation for this purpose. Use Pin 2 and Pin 4 (AGND) as the RF return path for the RFIN interface, and use Pin 18 and Pin 20 as the return path for the RFOUT interface. A ground shield between RFIN and RFOUT is necessary to minimize interaction outside of the bridge, which also impacts the measured directivity. The top ground and bottom ground layers must be connected with as many vias as possible in the shield between RFIN and RFOUT and around the edge of the ground return conductors of the GCPW.

Figure 61. Example GCPW Design for Interfacing RFIN and RFOUT

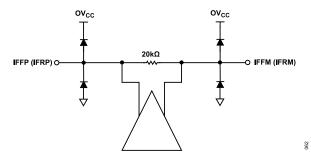

## IFFP, IFFM, IFRP, and IFRM Interfaces

The differential IF output amplifiers are capable of driving 100  $\Omega$  differential loads up to 8 V p-p. In the event of an output short circuit to ground or AVCC, an internal clamp limits the current to less than roughly 200 mA for each of the single-ended outputs (IFFM, IFFP, IFRP, and IFRM).

Figure 62. Simplified Schematic of the IF Output Interfaces

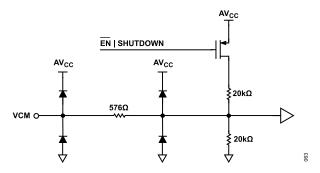

#### **VCM** Interface

The VCM interface controls the common-mode voltage level at the IFFx and IFRx output interfaces and simplifies DC-coupled interfacing to a wide variety of ADCs. If provided by the ADC of choice, this pin can be connected to the common-mode output or reference output pin to align the common-mode levels and maximize the available dynamic range.

When the VCM pin is left floating, an internal voltage-divider sets the common-mode voltage level to OVCC/2. When externally driven, a low-impedance voltage source must be used to set the voltage on this pin. The tracking range of the VCM pin voltage to the common-mode output voltage is linear in the range from 1 V to 4 V. For voltage levels outside this range, the output common-mode level is clamped to 1 V or 4 V, respectively.

analog.com Rev. A | 23 of 32

## **APPLICATIONS INFORMATION**

Figure 63. Simplified Schematic of the Common-Mode Control Interface

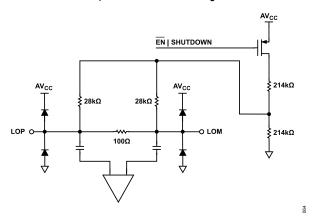

## **LOP and LOM Interface**

The LO interface can be driven differentially or single-ended. A differentially driven LO with a well designed PCB layout (for example, using a ground, signal, signal, ground coplanar waveguide) can help to reduce LO signal radiated emission and unwanted coupling to other nets in the system. The LOP and LOM inputs are internally biased at AVCC/2. When driven single-ended, the internal 100  $\Omega$  termination can be impedance matched using a 2:1 external balun.

Figure 64. Simplified LO Interface

## **OFP and OFM Interface**

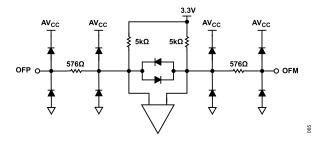

The offset frequency interface (OFP and OFM) is internally biased at a common-mode level of 3.3 V, and must be AC-coupled to an external signal source. The inputs can be driven differentially or single-ended with one terminal AC-grounded with a high value capacitor. A value of 10 nF or higher is recommended for a 400 kHz input frequency.

Figure 65. Simplified Offset Frequency Interface

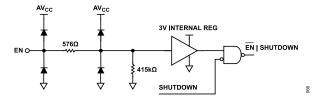

#### **EN Interface**

The chip is in shutdown if either the shutdown bit in DEVICE\_CONFIG (Register 0x02, Bit 1) is set, or the EN pin is deasserted. An internal 415 k $\Omega$  pull-down ensures the device is off (shut down) if the pin is left floating.

Figure 66. Simplified Enable Interface

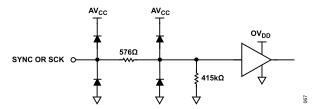

## SYNC and SCK Interfaces

The SYNC and SCK interfaces are both high-impedance CMOS logic input interfaces. As listed in Table 1, the logic high and logic low levels are defined relative to the serial port supply interface, OVDD. Both inputs are internally pulled low when left floating.

Figure 67. SYNC and SPI Clock Interface

The SYNC interface is used to synchronize all ADL5960 devices in a system. A falling edge on this interface resets the frequency dividers in the LO and OF interfaces to a known, predefined state. All ADL5960 devices receive the negative SYNC edge before the next edge on the LO or OF interface arrives. The SYNC pulse can also be applied directly after power-on, before an LO and OF clock are applied.

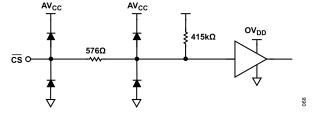

## **CS** Interface

The  $\overline{CS}$  interface controls the start and ending of the communication through the serial interface of the device. The SPI is active when the voltage on  $\overline{CS}$  represents logic low and is disabled when the voltage on  $\overline{CS}$  is logic high, as defined in Table 1. The input is internally pulled high, disabling the SPI, when this pin is left floating.

Figure 68. SPI Chip Select Interface

analog.com Rev. A | 24 of 32

#### **APPLICATIONS INFORMATION**

# **SDIO Interface**

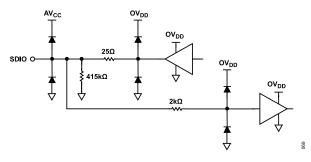

Figure 69. Simplified SDIO Interface

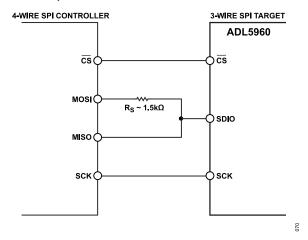

The ADL5960 implements a 3-wire SPI that uses a single line for transmission/reception of data. When receiving data, that is, during a write operation to the device, the transmitter output becomes high-impedance such that the transmitting device can pull the data line low or high as desired. To connect this interface to an SPI controller using a 4-wire interface, with separate data input and data output lines, a series current limiting resistor as shown in Figure 70 is recommended to isolate the controller and target outputs. This resistor provides protection in the event that both outputs become simultaneously active.

Figure 70. SPI 4-Wire to 3-Wire Interfacing

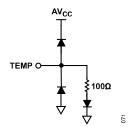

#### **TEMP Interface**

In addition to the on-chip digital thermometer, the TEMP pin can be used to monitor the die temperature by applying a known reference current into the pin and measure the pin voltage relative to ground. An injected current of 42  $\mu A$  results in a nominal voltage of 0.775 V at 25°C and a temperature slope of approximately -1.54 mV/°C.

Figure 71. Temperature Diode Interface

# LO INTERFACE CONFIGURATION

The LO interface supports a bypass mode and four different multiply/divide modes that are selectable through register 0x20 in the SPI interface. Each of these operating modes is discussed in the Bypass Mode (Bypass = 1) section to Multiply by 4 Mode (LOMODE = 3) section.

# Bypass Mode (Bypass = 1)

The LO signal is routed directly to the internal downconversion mixers, bypassing the frequency multipliers and dividers. The LO multipliers and dividers and the OF interface are disabled. The ADL5960 achieves the widest bandwidth and highest dynamic range in this mode.

# Divide by 2 Mode (LOMODE = 0)